# Las Palmas de Instituto Universitario de Gran Canaria Microelectrónica Aplicada

# Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

## Trabajo Fin de Máster

Metodología de diseño de sistemas de control para dispositivos SoC FPGA

**Autor:** Gabriel Santana Quintana **Tutor(es):** Dr. Pedro Pérez Carballo

Dr. Carlos Betancor Martín

Fecha: Marzo 2022

### Instituto Universitario de Microelectrónica Aplicada

# Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

## Trabajo Fin de Máster

# Metodología de diseño de sistemas de control para dispositivos SoC FPGA

#### **HOJA DE FIRMAS**

**Alumno:** Gabriel Santana Quintana Fdo.:

**Tutor:** Dr. Pedro Pérez Carballo Fdo.:

**Tutor:** Dr. Carlos Betancor Martín Fdo.:

Fecha: Marzo 2022

### Las Palmas de Instituto Universitario de Gran Canaria Microelectrónica Aplicada

## Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

### Trabajo Fin de Máster

## Metodología de diseño de sistemas de control para dispositivos SoC FPGA

#### HOJA DE EVALUACIÓN

| Calificación:   |                                 |       |

|-----------------|---------------------------------|-------|

| Presidente      | Dr. Sebastián López Suárez      | Fdo.: |

| Secretario      | Dr. Sunil Lalchand Khemchandani | Fdo.: |

| Vocal           | Dr. Alfonso Medina Escuela      | Fdo.: |

| Fecha: Marzo 20 | 022                             |       |

## Agradecimientos

A mi familia, por apoyarme y darme fuerzas durante el proceso de realización de este trabajo

#### Resumen

En este Trabajo Fin de Máster se propone una metodología de alto nivel para el diseño de sistemas de control a ser implementados en dispositivos SoC FPGA. Este desarrollo se aborda en dos fases. En la primera se presenta la metodología propuesta y en la segunda se realiza un ejemplo de implementación para su validación.

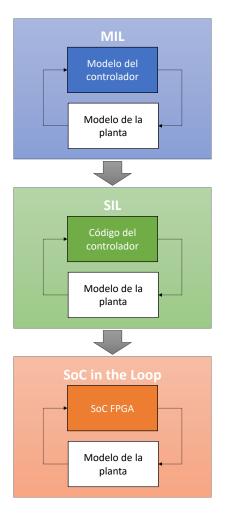

Para la metodología de diseño propuesta se utilizan las herramientas MATLAB/Simulink y Vivado Design Suite. Esta metodología consta de tres pasos claves, siendo estos, las simulaciones *Model in the Loop* (MIL), *Software in the Loop* (SIL) y *SoC in the Loop*. Con la simulación MIL se verifica el funcionamiento de los algoritmos de control desarrollados en conjunto con el modelo del sistema a controlar. La simulación SIL se realiza con el fin de comprobar que MATLAB/Simulink es capaz de generar código de los algoritmos diseñados y que con este se obtienen resultados análogos a los de la simulación MIL. Finalmente, la simulación *SoC in the Loop* se lleva a cabo para verificar el funcionamiento de la implementación de los algoritmos desarrollados sobre un dispositivo SoC FPGA, simulando su funcionamiento en conjunto con el modelo del sistema a controlar.

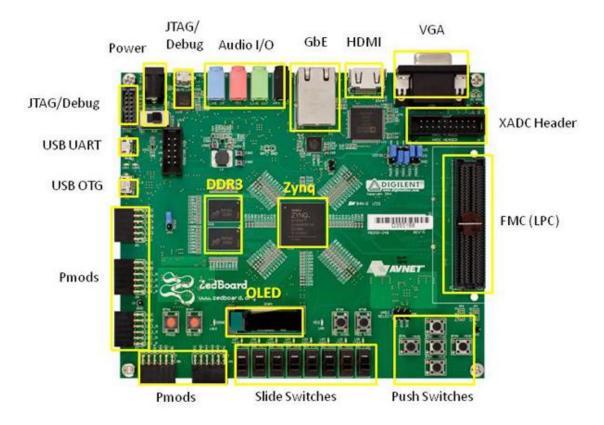

Como ejemplo de implementación se escoge el algoritmo MMTES (*Maximun-Minimum Tier Equalization Swapping*) en conjunto con un controlador MPPT (*Maximum Power Point Tracker*) para maximizar la producción de potencia de un sistema fotovoltaico en condiciones de sombras parciales. Se realiza una implementación *hardware* del controlador MPPT y una implementación *hardware/software* del algoritmo MMTES. El modelado del sistema a controlar se realiza en Simulink y los algoritmos de control se desarrollan utilizando MATLAB/Simulink. La placa de desarrollo sobre la que se implementan estos algoritmos es la ZedBoard, que incluye un dispositivo Zyng 7000.

La verificación del sistema implementado sobre la ZedBoard se realiza en conjunto con el modelo del sistema en Simulink. El sistema implementado tiene una utilización de recursos y un consumo de potencia relativamente bajo. La producción de potencia obtenida al realizar la simulación *SoC in the Loop* es equiparable a los resultados de las simulaciones MIL y SIL. Por lo tanto, se valida el correcto funcionamiento del sistema implementado en la ZedBoard y con ello, la funcionalidad de la metodología de diseño.

#### Abstract

This Master Thesis proposes a high-level methodology for the design of control systems to be implemented in SoC FPGA devices. This development is approached in two phases. In the first one, the proposed methodology is presented and in the second one, an example of implementation is carried out for its validation.

MATLAB/Simulink and Vivado Design Suite tools are used for the proposed design methodology. This methodology consists of three key steps: Model in the Loop (MIL), Software in the Loop (SIL) and SoC in the Loop simulations. The MIL simulation verifies the operation of the control algorithms developed in conjunction with the model of the system to be controlled. The SIL simulation is carried out to verify that MATLAB/Simulink is capable of generating code for the designed algorithms and that the results obtained are similar to those of the MIL simulation. Finally, the SoC in the Loop simulation is carried out to verify the performance of the implementation of the algorithms developed on a SoC FPGA device, simulating its operation in conjunction with the model of the system to be controlled.

As an example of implementation, the MMTES (Maximun-Minimum Tier Equalization Swapping) algorithm is chosen in conjunction with an MPPT (Maximum Power Point Tracker) controller to maximize the power production of a photovoltaic system under partial shading conditions. A hardware implementation of the MPPT controller and a hardware/software implementation of the MMTES algorithm are carried out. The modelling of the system to be controlled is done in Simulink and the control algorithms are developed using MATLAB/Simulink. The development board on which these algorithms are implemented is the ZedBoard, which includes a Zynq 7000 device.

The verification of the system implemented on the ZedBoard is carried out in conjunction with the system model in Simulink. The implemented system has a relatively low resource utilisation and power consumption. The power output obtained by performing the SoC in the Loop simulation is comparable to the results of the MIL and SIL simulations. Therefore, the correct functioning of the system implemented on the ZedBoard is validated and with it, the functionality of the design methodology.

## **Tabla de Contenidos**

| TABLA [  | E CONTENIDOS                      |                                                                         |

|----------|-----------------------------------|-------------------------------------------------------------------------|

| ÍNDICE I | DE FIGURAS                        | v                                                                       |

| ÍNDICE I | DE TABLAS                         | ıx                                                                      |

| ÍNDICE I | DE CÓDIGOS                        | xı                                                                      |

| ACRÓNI   | MOS                               | XIII                                                                    |

| CAPÍTUI  | .O 1. INTRODUCCIÓN                | 1                                                                       |

| 1.1.     | ANTECEDENTES                      |                                                                         |

| 1.2.     | OBJETIVOS                         | 6                                                                       |

| 1.3.     | PETICIONARIO                      | 7                                                                       |

| 1.4.     | ESTRUCTURA DEL DOCUMENTO          |                                                                         |

| CAPÍTUI  | .O 2. ESTADO DEL ARTE             | 9                                                                       |

| 2.1.     | INTRODUCCIÓN                      | 9                                                                       |

| 2.2.     | USO DE FPGA PARA SISTEMAS DE CON  | NTROL EN ROBÓTICA9                                                      |

| 2.3.     | CONTROLADORES EMPOTRADOS PARA     | APLICACIONES INDUSTRIALES BASADOS EN FPGA                               |

| 2.4.     | CONTROL BASADO EN FPGA PARA ELE   | CTRÓNICA DE POTENCIA Y SISTEMAS DE GENERACIÓN DE ENERGÍA ELÉCTRICA . 13 |

| 2.5.     | METODOLOGÍAS DE DISEÑO            |                                                                         |

| 2.6.     | CONCLUSIONES                      |                                                                         |

| CAPÍTUI  | .O 3. CASO DE IMPLEMENTA          | CIÓN17                                                                  |

| 3.1.     | INTRODUCCIÓN                      |                                                                         |

| 3.2.     | ÁREA DE APLICACIÓN                |                                                                         |

| 3.3.     | CASO DE ESTUDIO                   |                                                                         |

| 3.4.     | CONCLUSIONES                      |                                                                         |

| CAPÍTUI  | .O 4. METODOLOGÍA DE DISE         | ÑO19                                                                    |

| 4.1.     | INTRODUCCIÓN                      |                                                                         |

| 4.2.     | MATLAB/SIMULINK                   |                                                                         |

| 4.2      | .1. Simscape Electrical           |                                                                         |

| 4.2      | .2. Fixed-Point Designer          |                                                                         |

| 4.2      | .3. MATLAB Coder                  |                                                                         |

| 4.2      | .4. Simulink Coder                | 21                                                                      |

| 4.2      | .5. Embedded Coder                | 21                                                                      |

| 4.2      | .6. HDL Coder                     | 21                                                                      |

| 4.2      |                                   | e for Xilinx Zynq Platform21                                            |

| 4.2      | .8. Embedded Coder Support F      | Package for Xilinx Zynq Platform21                                      |

| 4.3.     | HERRAMIENTAS DE SÍNTESIS E IMPLEM | ENTACIÓN PARA FPGA                                                      |

| 4.3      | .1. Xilinx Vivado Design Suite    |                                                                         |

| 44       | METODOLOGÍA DE DISEÑO             | 23                                                                      |

| 4.5. CONCLUSIONES                                                          | 27 |

|----------------------------------------------------------------------------|----|

| CAPÍTULO 5. ALGORITMO DE RECONFIGURACIÓN DINÁMICA DE PANELES FOTOVOLTAICOS | 29 |

| 5.1. Introducción                                                          | 29 |

| 5.2. ALGORITMO MMTES                                                       | 31 |

| 5.2.1. Características principales                                         | 31 |

| 5.2.2. Funcionamiento                                                      | 32 |

| 5.2.3. Matriz de interruptores                                             |    |

| 5.3. IMPLEMENTACIÓN DEL ALGORITMO MMTES EN MATLAB                          |    |

| 5.3.1. Función MMTESSort                                                   |    |

| 5.3.2. Función PairForSwapping                                             |    |

| 5.3.3. Función SwapPair                                                    |    |

| 5.4. MEJORAS PROPUESTAS PARA UNA IMPLEMENTACIÓN HW/SW                      |    |

| 5.4.1. Bitonic Sort                                                        |    |

| 5.4.1.1. AdaptInputData                                                    |    |

| 5.4.1.2. BitonicSort                                                       |    |

| 5.4.2. PairForSwapping paralelo                                            |    |

| 5.4.2.1. PfsPllInData                                                      |    |

| 5.4.2.2. PairForSwappingPll                                                |    |

| 5.4.2.3. PfsPllOutData                                                     | 49 |

| 5.5. CONCLUSIONES                                                          | 50 |

| CAPÍTULO 6. CONTROLADOR MPPT                                               | 51 |

| 6.1. Introducción                                                          | 51 |

| 6.2. CONTROLADOR MPPT                                                      |    |

| 6.2.1. Perturbación y Observación (P&O)                                    |    |

| 6.2.2. Conductancia incremental                                            |    |

| 6.2.3. Tensión a circuito abierto fraccional                               |    |

| 6.3. IMPLEMENTACIÓN DEL CONTROLADOR.                                       |    |

| 6.4. CONCLUSIONES                                                          |    |

| CAPÍTULO 7. MODELADO DEL SISTEMA                                           | 57 |

| 7.1. Introducción                                                          | 57 |

| 7.2. SISTEMA A MODELAR                                                     |    |

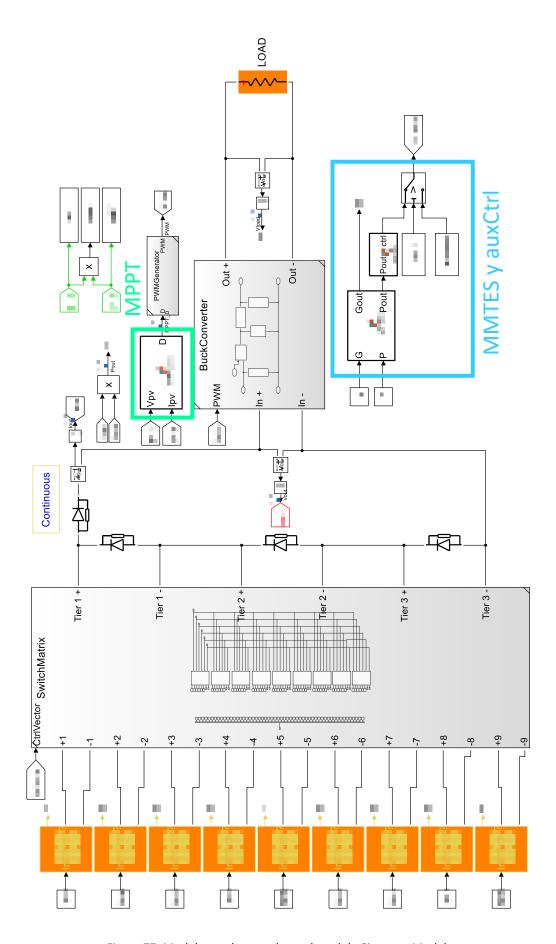

| 7.3. MODELADO DEL HARDWARE                                                 |    |

| 7.3.1. Paneles fotovoltaicos                                               |    |

| 7.3.2. Switch matrix                                                       |    |

| 7.3.3. Buck Converter                                                      |    |

| 7.4. MODELADO DE LOS ALGORITMOS A IMPLEMENTAR EN EL SOC FPGA               | 65 |

| 7.4.1. Función auxCtrl                                                     | 65 |

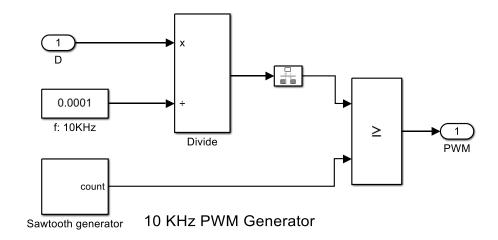

| 7.4.2. Generador de PWM                                                    | 66 |

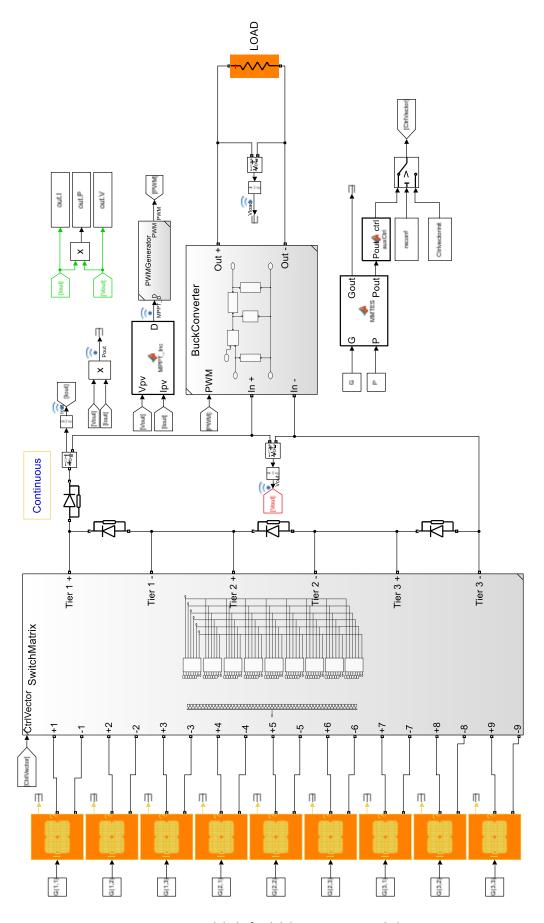

| 7.5. SISTEMA FINAL                                                         | 67 |

| 7.6. SIMULACIÓN MODEL-IN-THE-LOOP (MIL)                                    |    |

| 7.7. SIMULACIÓN SOFTWARE-IN-THE-LOOP (SIL)                                 | 84 |

| 7.8. CONCLUSIONES                                                          | 85 |

| CAPÍTULO 8. DESARROLLO Y VERIFICACIÓN DE LOS BLOQUES IP                    | 87 |

| 8.1. Introducción                                                          |    |

|                                                                            |    |

| 8.2. PLACA DE DESARROLLO                                                   | _  |

| 8.4. MPPT                                                                  |    |

| 8.4.1. Conversión a punto fijo                                             |    |

| 8.4.2. Verificación del bloque IP generado                                 |    |

| 8.5. GENERADOR DE PWM                                                      |    |

| 8.5.1. Verificación del bloque IP generado                                 |    |

| 8.6. MMTES                                                                 |    |

| 8.6.1. MMTESSort                                                           |    |

|                                                                            |    |

| 8.6.1.1. Conversión a punto fijo             | 94  |

|----------------------------------------------|-----|

| 8.6.1.2. Verificación del bloque IP generado | 94  |

| 8.6.2. PairForSwapping                       | 95  |

| 8.6.2.1. Conversión a punto fijo             |     |

| 8.6.2.2. Verificación del bloque IP generado | 95  |

| 8.6.3. Bitonic Sort                          | 95  |

| 8.6.3.1. Verificación del bloque IP generado | 96  |

| 8.6.4. PairForSwapping paralelo              | 96  |

| 8.6.4.1. Verificación del bloque IP generado | 96  |

| 8.6.5. Comparación de resultados             | 97  |

| 8.7. CONCLUSIONES                            | 99  |

| CAPÍTULO 9. IMPLEMENTACIÓN Y VERIFICACIÓN    | 101 |

| 9.1. Introducción                            |     |

| 9.2. IMPLEMENTACIÓN DEL SISTEMA FINAL        | 101 |

| 9.3. VERIFICACIÓN                            | 108 |

| 9.4. CONCLUSIONES                            | 117 |

| CAPÍTULO 10. CONCLUSIONES Y TRABAJOS FUTUROS | 119 |

| 10.1. CONCLUSIONES                           | 119 |

| 10.2. Trabajos futuros                       | 121 |

| REFERENCIAS                                  | 123 |

| ANEXO                                        | 131 |

|                                              |     |

# Índice de Figuras

| FIGURA 1. REPRESENTACION DE LA COMPLEJIDAD ALGORITMICA Y LA CAPACIDAD DE PROCESAMIENTO PARALELO PARA LAS DISTINTAS TECNOLOGÍAS DE IMPLEMENTACIÓN DE SISTEMAS DE CONTROL INDUSTRIAL [3] | 2 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| FIGURA 2. MERCADO GLOBAL DE FPGA POR REGIÓN 2020-2026 [8]                                                                                                                              | 4 |

| FIGURA 3. DIVISIÓN DEL MERCADO DE FPGA POR SECTORES [9]                                                                                                                                | 5 |

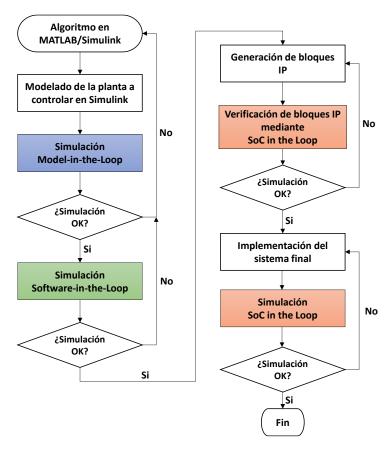

| FIGURA 4. MODOS DE SIMULACIÓN DE LA METODOLOGÍA DE DISEÑO                                                                                                                              | 6 |

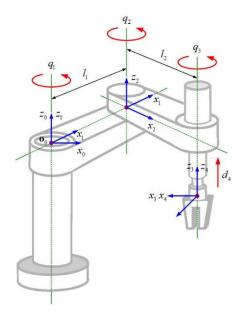

| FIGURA 5. ROBOT SCARA [29]1                                                                                                                                                            | 1 |

| FIGURA 6. PUMA 560 [30]1                                                                                                                                                               | 1 |

| FIGURA 7. DIAGRAMA DE BLOQUES DEL MODELO DEL SISTEMA CONTROLAR1                                                                                                                        | 8 |

| FIGURA 8. CODISEÑO HARDWARE/SOFTWARE PARA PLATAFORMAS SOC [67]2                                                                                                                        | 2 |

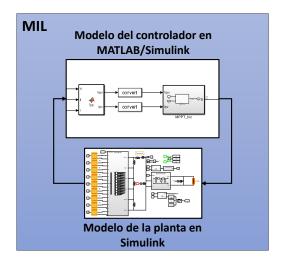

| FIGURA 9. SIMULACIÓN MIL2                                                                                                                                                              | 3 |

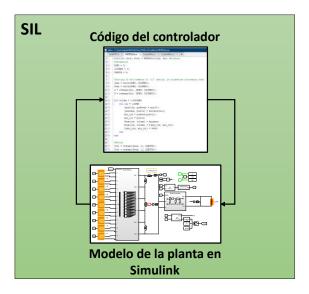

| FIGURA 10. SIMULACIÓN SIL2                                                                                                                                                             | 4 |

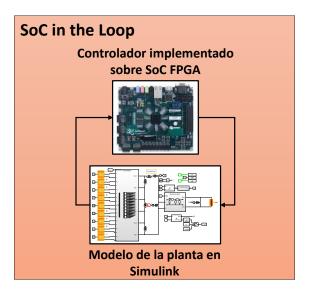

| FIGURA 11. SIMULACIÓN <i>SOC IN THE LOOP</i> 2                                                                                                                                         | 5 |

| FIGURA 12. FLUJO DE DISEÑO2                                                                                                                                                            | 6 |

| FIGURA 13. DISTRIBUCIÓN DE LOS PASOS DEL FLUJO DE DISEÑO SEGÚN LAS HERRAMIENTAS NECESARIAS                                                                                             |   |

| 2                                                                                                                                                                                      |   |

| FIGURA 14. EJEMPLO DE SOMBRAS PARCIALES SOBRE UNA INSTALACIÓN FOTOVOLTAICA [72] 2                                                                                                      |   |

| FIGURA 15. CONFIGURACIÓN TCT 3X3                                                                                                                                                       |   |

| FIGURA 16. DIAGRAMA DE FLUJO DEL ALGORITMO MMTES [56]                                                                                                                                  |   |

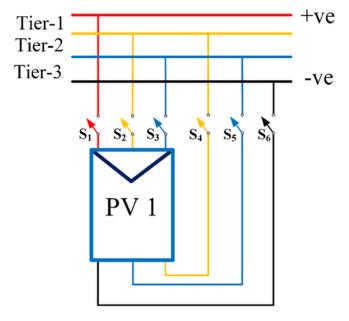

| FIGURA 17. EJEMPLO DE MATRIZ DE INTERRUPTORES PARA UN ARRAY 3 X 3 [56]                                                                                                                 | 5 |

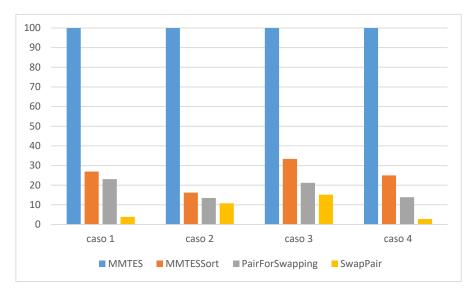

| FIGURA 18. REPRESENTACIÓN EN PORCENTAJES DEL TIEMPO DE EJECUCIÓN DEL ALGORITMO MMTES 4                                                                                                 | 0 |

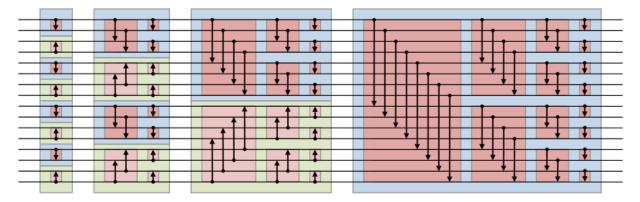

| FIGURA 19. BITONIC SORTING NETWORK PARA UN ARRAY DE ENTRADA DE 16 ELEMENTOS [78]4                                                                                                      | 2 |

| FIGURA 20.ESQUEMÁTICO DEL BITONIC SORT PARA EL CASO 1, 2 Y 44                                                                                                                          | 2 |

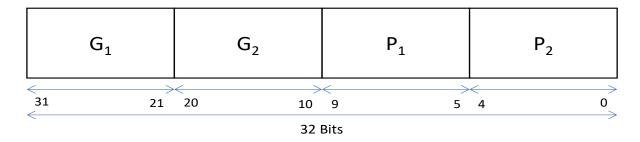

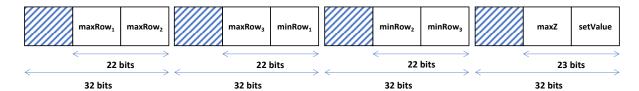

| FIGURA 21. PAQUETE DE DATOS A TRANSMITIR AL BITONIC SORT                                                                                                                               |   |

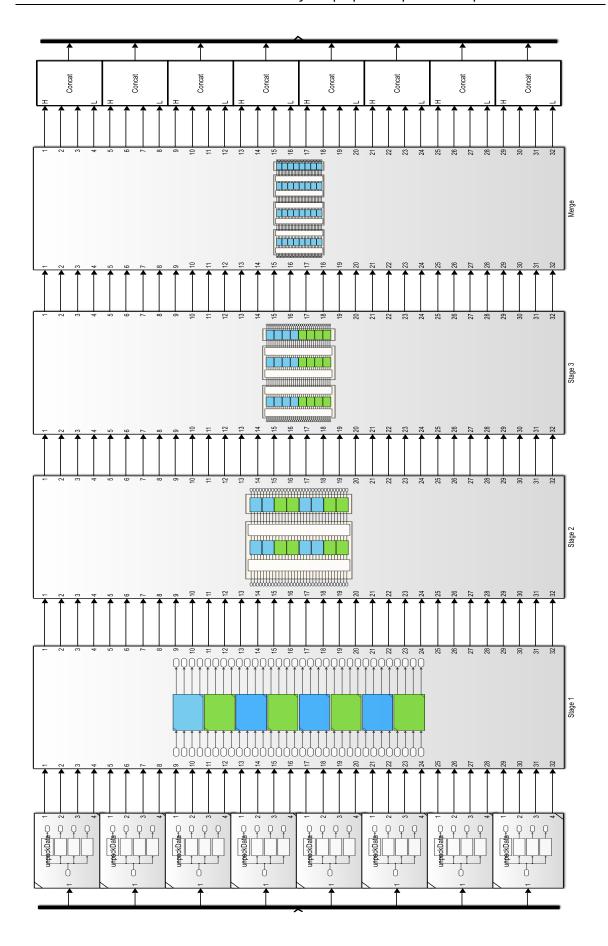

| FIGURA 22. BITONICSORT4                                                                                                                                                                | 5 |

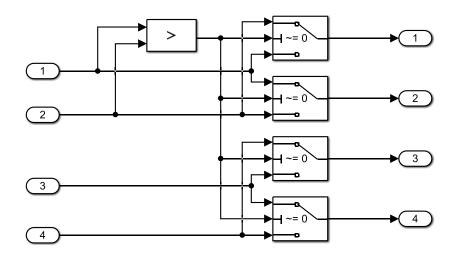

| FIGURA 23.BLOQUE DE ORDENAMIENTO CRECIENTE4                                                                                                                                            | 6 |

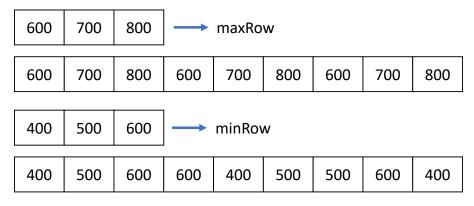

| FIGURA 24. ARRAY DE SALIDA DE LA FUNCIÓN PFSPLLINDATA4                                                                                                                                 | 7 |

| FIGURA 25. ARRAYS AUXILIARES EN LA FUNCIÓN PAIRFORSWAPPINGPLL4                                                                                                                         | 8 |

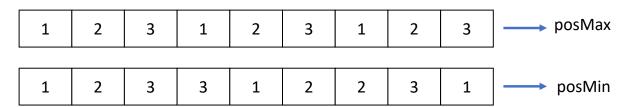

| FIGURA 26. ARRAYS POSMAX Y POSMIN4                                                                                                                                                     | 8 |

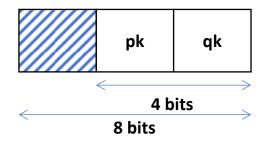

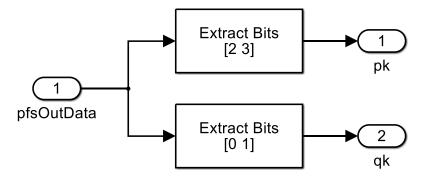

| FIGURA 27. EMPAQUETADO DE LOS DATOS DE SALIDA DE PAIRFORSWAPPINGPLL                             |    |

|-------------------------------------------------------------------------------------------------|----|

| FIGURA 28. FUNCIÓN PFSPLLOUTDATA                                                                | 49 |

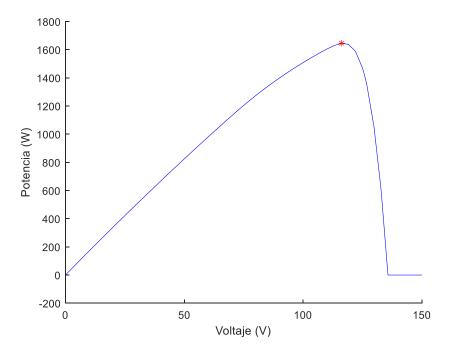

| FIGURA 29. DIAGRAMA P-V DE UNA INSTALACIÓN FOTOVOLTAICA                                         | 52 |

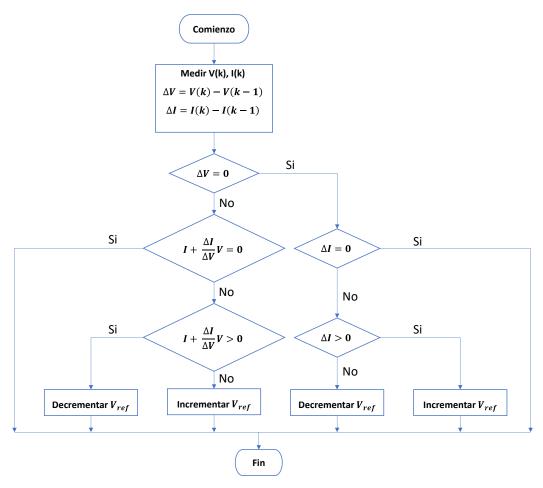

| FIGURA 30. DIAGRAMA DE FLUJO DEL ALGORITMO MPPT DE CONDUCTANCIA INCREMENTAL [82]                | 54 |

| FIGURA 31. DIAGRAMA DE BLOQUES DEL SISTEMA A MODELAR.                                           | 58 |

| FIGURA 32. MODELO DE MÓDULO FOTOVOLTAICO IMPLEMENTADO POR EL BLOQUE PV ARRAY [85]               | 59 |

| FIGURA 33. COMPARATIVA DE CARACTERÍSTICAS I-V A TEMPERATURA CONSTANTE PARA EL MODELO CS6A-170PE | 60 |

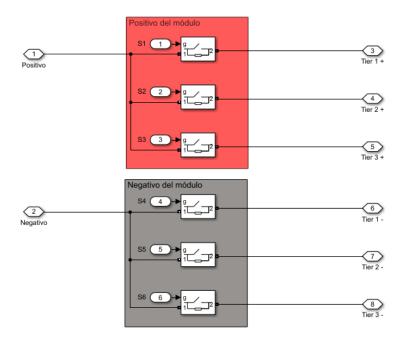

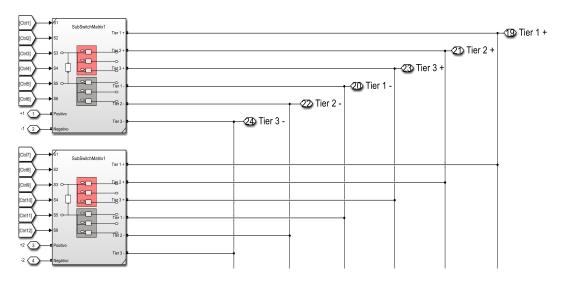

| FIGURA 34. SUBSYSTEM SUBSWITCHMATRIX                                                            | 61 |

| FIGURA 35. EJEMPLO DE CONEXIONADO DE LOS SUBSWITCHMATRIX                                        | 61 |

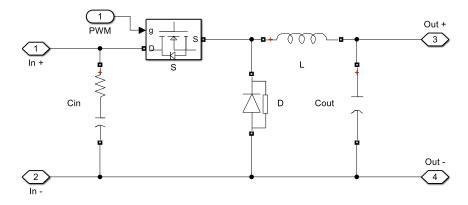

| FIGURA 36. IMPLEMENTACIÓN DEL BUCK CONVERTER EN SIMULINK.                                       | 64 |

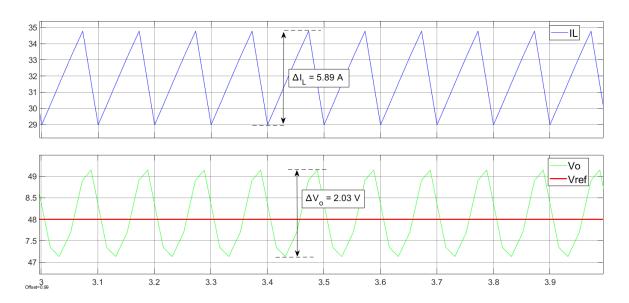

| FIGURA 37. CORRIENTE DE RIZADO DEL INDUCTOR Y RIZADO DE LA TENSIÓN DE SALIDA                    | 64 |

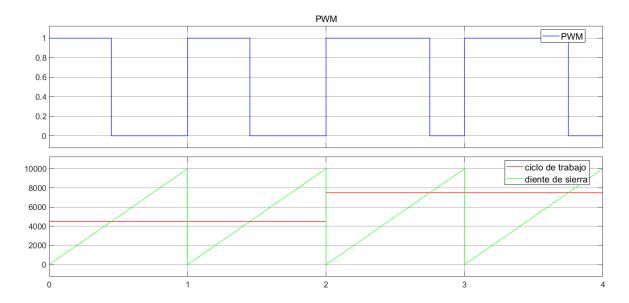

| FIGURA 38. GENERACIÓN DE LA SEÑAL PWM                                                           | 66 |

| FIGURA 39. IMPLEMENTACIÓN DEL GENERADOR DE PWM.                                                 | 67 |

| FIGURA 40. MODELADO FINAL DEL SISTEMA EN SIMULINK                                               |    |

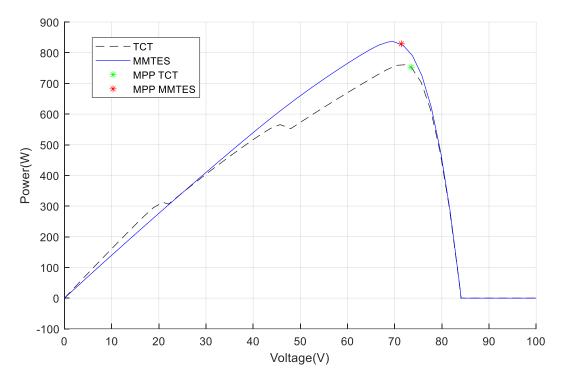

| FIGURA 41. CURVAS P-V CASO 1                                                                    | 70 |

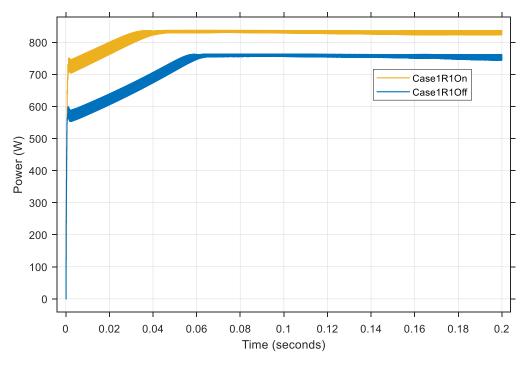

| FIGURA 42. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R1 EN EL CASO 1                       | 71 |

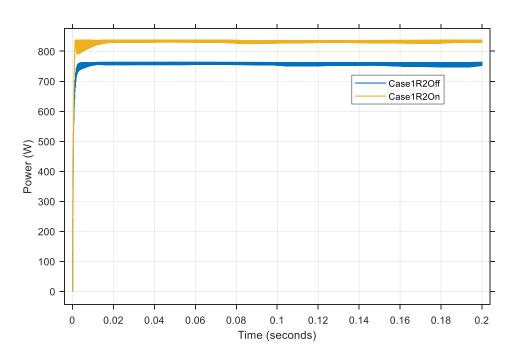

| FIGURA 43.COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R₂ EN EL CASO 1                        | 71 |

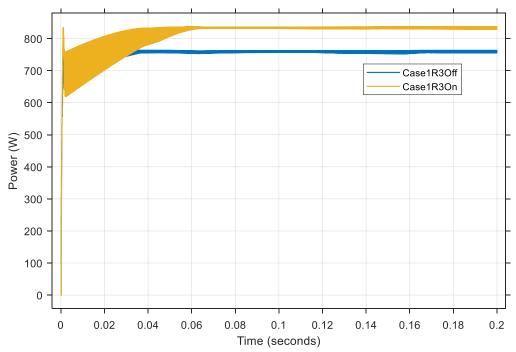

| FIGURA 44.COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R3 EN EL CASO 1                        | 72 |

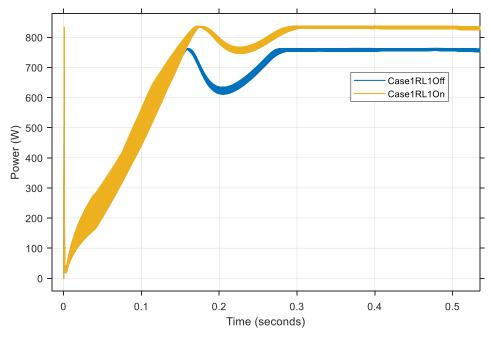

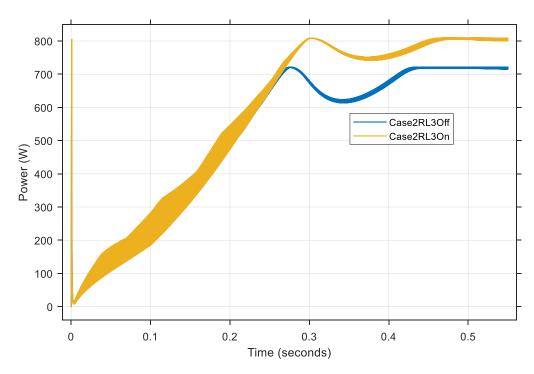

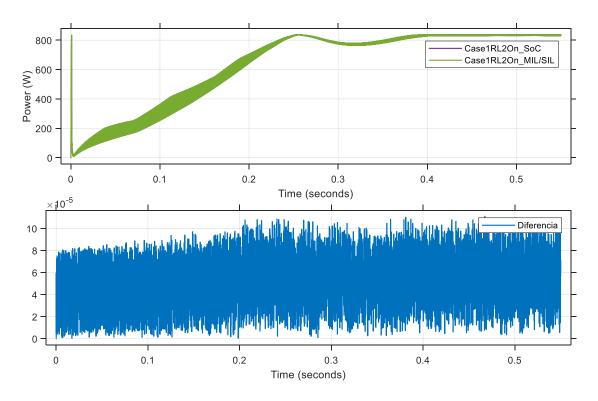

| FIGURA 45. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL1 EN EL CASO 1                      | 73 |

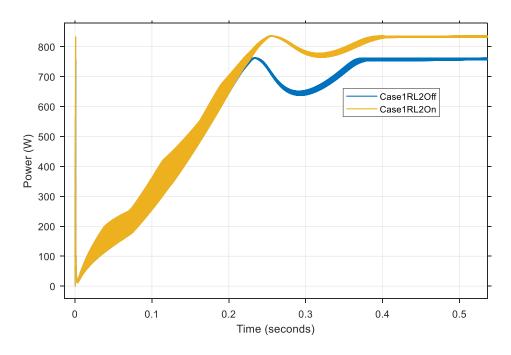

| FIGURA 46. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL₂ EN EL CASO 1                      | 73 |

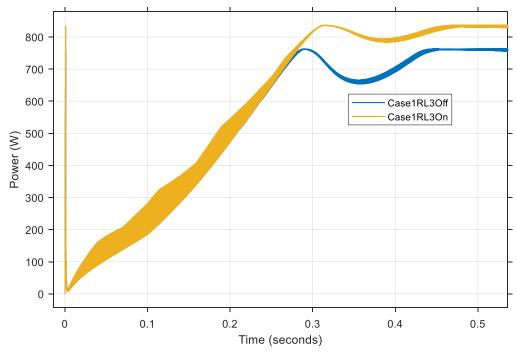

| FIGURA 47. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL₃ EN EL CASO 1                      | 74 |

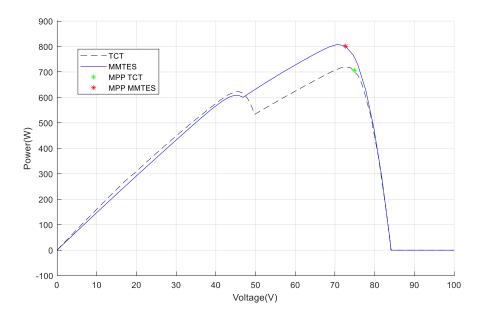

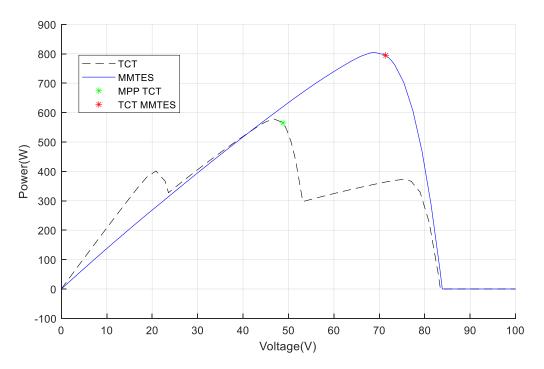

| FIGURA 48. CURVAS P-V CASO 2                                                                    | 75 |

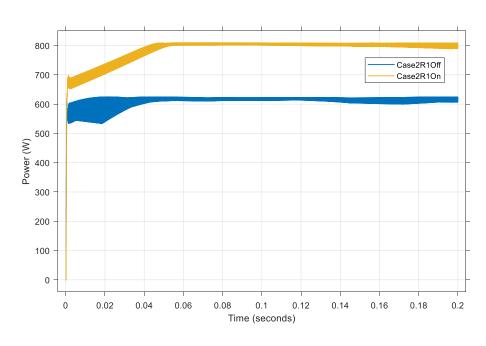

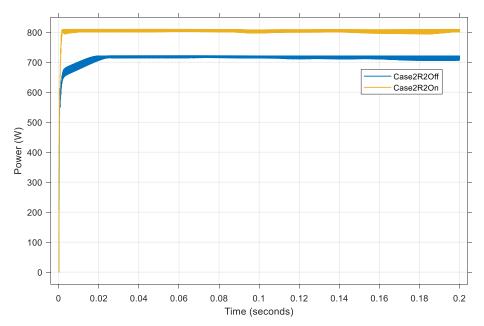

| FIGURA 49.COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R1 EN EL CASO 2                        | 75 |

| FIGURA 50. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R₂ EN EL CASO 2                       | 76 |

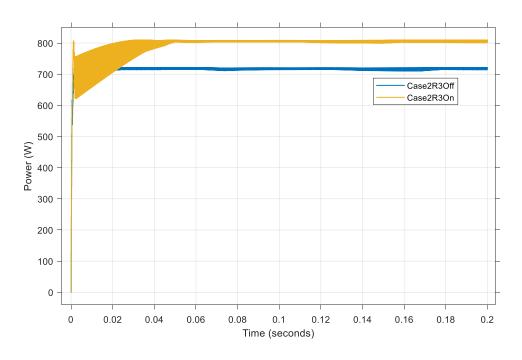

| FIGURA 51. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R3 EN EL CASO 2                       | 76 |

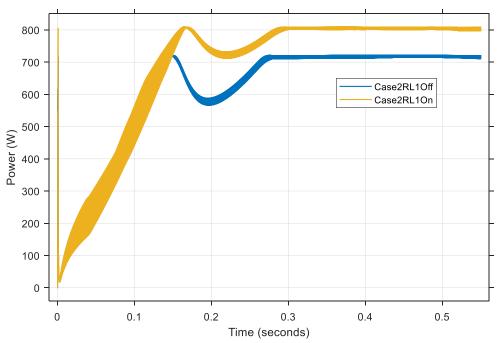

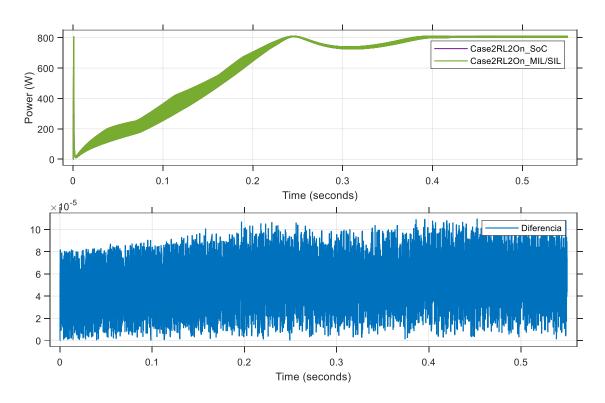

| FIGURA 52. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL1 EN EL CASO 2                      | 77 |

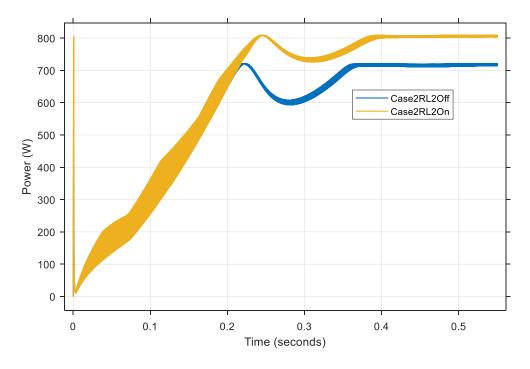

| FIGURA 53. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL₂ EN EL CASO 2                      | 78 |

| FIGURA 54. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL₃ EN EL CASO 2                      | 78 |

| FIGURA 55.CURVAS P-V CASO 4                                                                     | 79 |

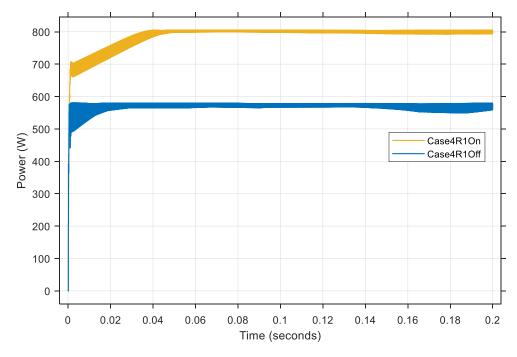

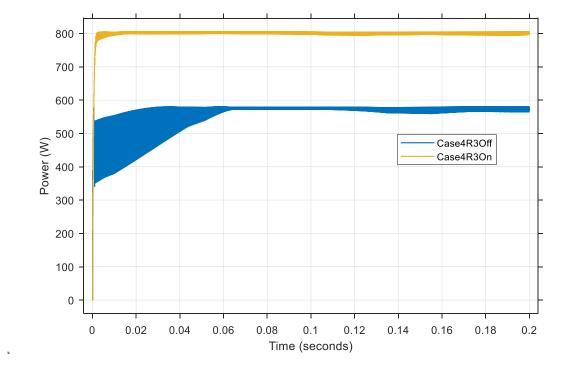

| FIGURA 56. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R1 EN EL CASO 4                       | 80 |

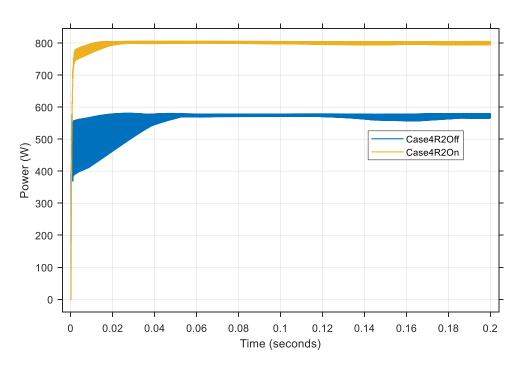

| FIGURA 57. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R₂ EN EL CASO 4                       | 80 |

| FIGURA 58. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA R3 EN EL CASO 4                       | 81 |

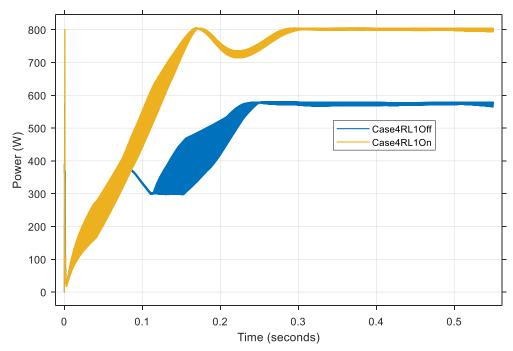

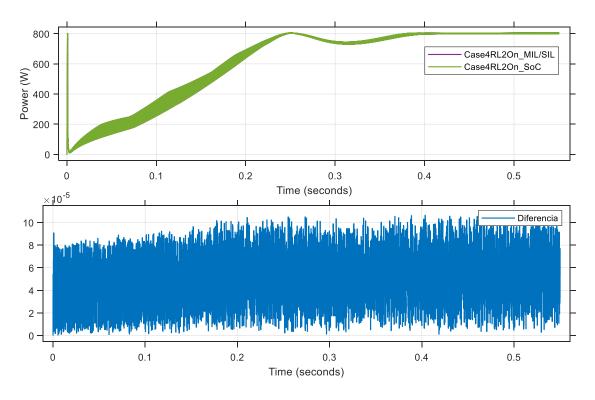

| FIGURA 59. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL1 EN EL CASO 4                      | 82 |

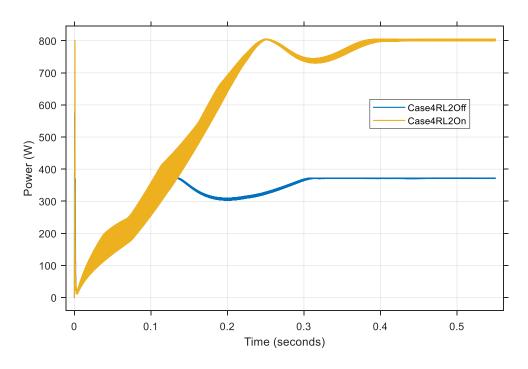

| FIGURA 60. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL₂ EN EL CASO 4                      | 82 |

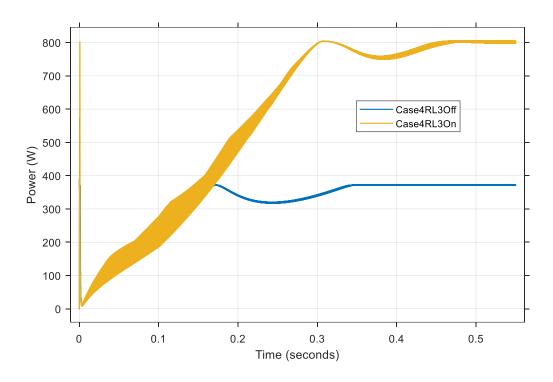

| FIGURA 61. COMPARATIVA DE LA POTENCIA DE SALIDA CON CARGA RL₃ EN EL CASO 4                      | 83 |

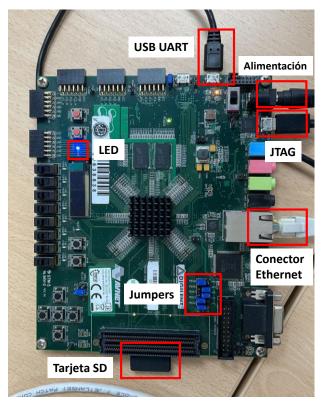

| FIGURA 62. OVERLAY VIEW DE LA ZEDBOARD [98]                                                     | 88 |

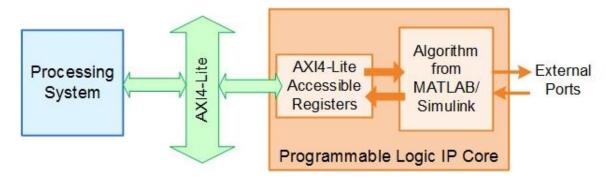

| FIGURA 63. COMUNICACIÓN ENTRE EL BLOQUE IP Y EL PROCESADOR EMPOTRADO [100]                      | 89 |

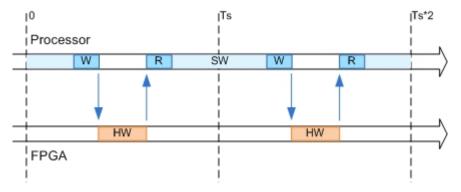

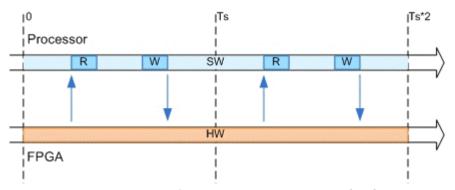

| FIGURA 64. MODO DE FUNCIONAMIENTO BLOQUEANTE [101]                                              | 89 |

| FIGURA 65. MODO DE FUNCIONAMIENTO NO BLOQUEANTE [101]                                              | 89    |

|----------------------------------------------------------------------------------------------------|-------|

| FIGURA 66. SIMULACIÓN EN MODO EXTERNO DESDE SIMULINK [99]                                          | 90    |

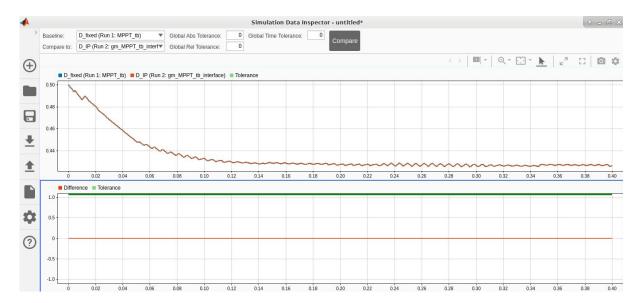

| FIGURA 67. COMPARATIVA DEL CICLO DE TRABAJO CALCULADO POR EL BLOQUE IP Y LA SIMULACIÓN<br>SIMULINK |       |

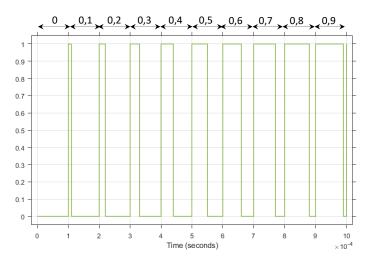

| FIGURA 68. VERIFICACIÓN DEL IP PWM_GENERATOR                                                       | 93    |

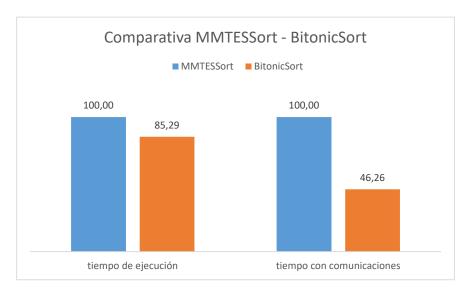

| FIGURA 69. COMPARATIVA MMTESSORT Y BITONICSORT                                                     | 98    |

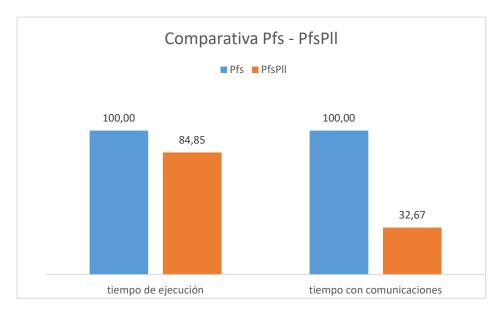

| FIGURA 70. COMPARATIVA PAIRFORSWAPPING Y PAIRFORSWAPPINGPLL                                        | 99    |

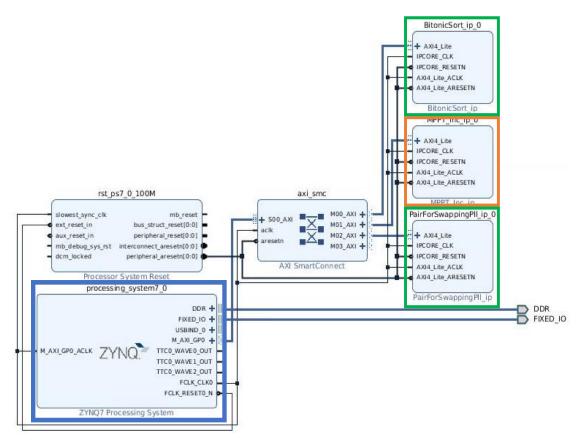

| FIGURA 71. DIAGRAMA DE BLOQUES DE LA PLATAFORMA HARDWARE GENERADA                                  | . 102 |

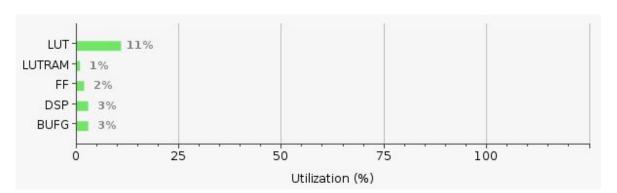

| FIGURA 72. UTILIZACIÓN DE RECURSOS DEL SISTEMA                                                     | . 103 |

| FIGURA 73. RESULTADOS DE TEMPORIZACIÓN DEL SISTEMA                                                 | . 104 |

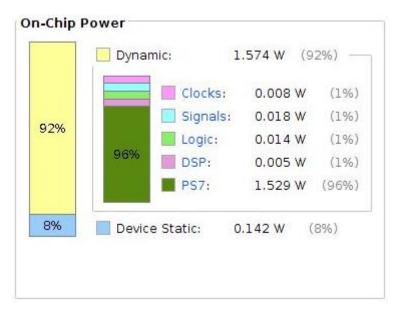

| FIGURA 74. CONSUMICIÓN DE POTENCIA DEL SISTEMA DISEÑADO                                            | . 104 |

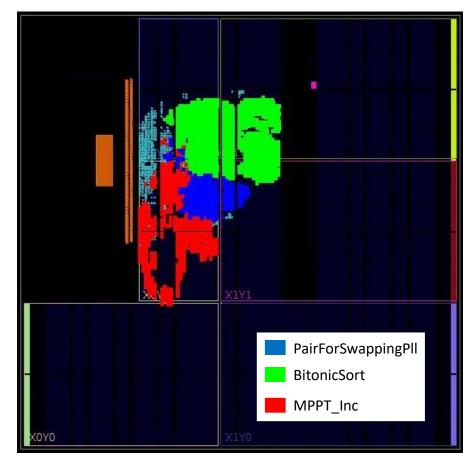

| FIGURA 75. LAYOUT DEL SISTEMA                                                                      | . 105 |

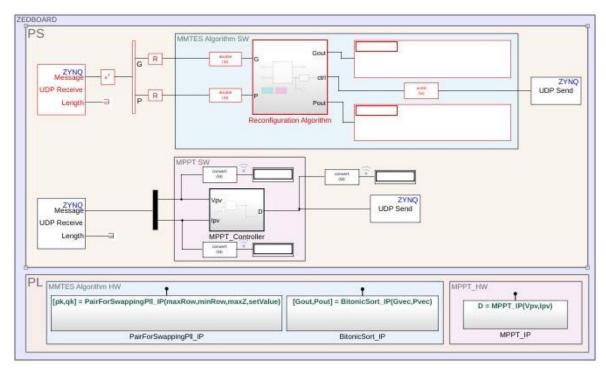

| FIGURA 76. MODELO ZEDBOARDMODEL                                                                    | . 106 |

| FIGURA 77. MODELO EN EL QUE SE BASA EL MODELO SIMSCAPEMODEL                                        | . 109 |

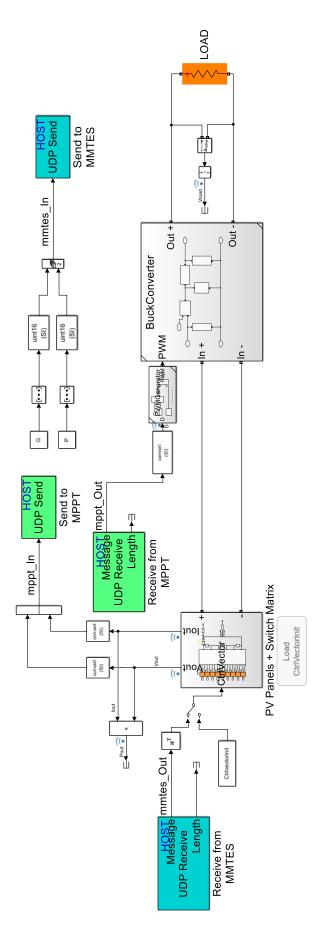

| FIGURA 78. MODELO SIMSCAPEMODEL.                                                                   | . 110 |

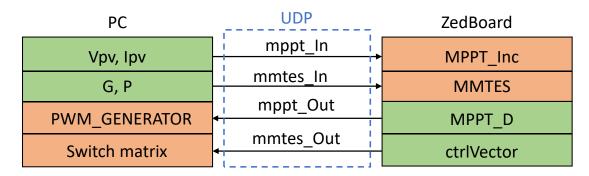

| FIGURA 79. FLUJO DE DATOS ENTRE SIMSCAPEMODEL Y LA ZEDBOARD                                        | . 111 |

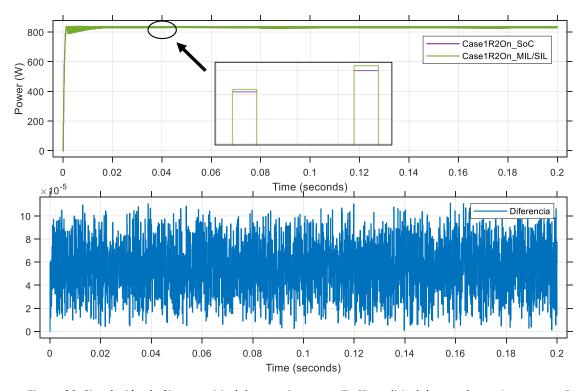

| FIGURA 80. SIMULACIÓN DE SIMSCAPEMODEL EN CONJUNTO CON ZEDBOARDMODEL PARA EL CASO<br>CON CARGA R2  |       |

| FIGURA 81. SIMULACIÓN DE SIMSCAPEMODEL EN CONJUNTO CON ZEDBOARDMODEL PARA EL CASO<br>CON CARGA R2  |       |

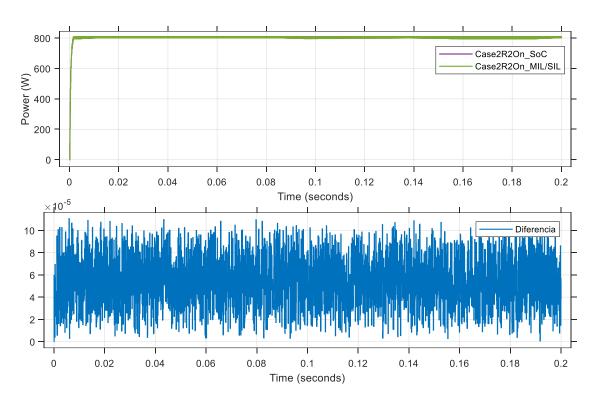

| FIGURA 82. SIMULACIÓN DE SIMSCAPEMODEL EN CONJUNTO CON ZEDBOARDMODEL PARA EL CASO<br>CON CARGA R2  |       |

| FIGURA 83. SIMULACIÓN DE SIMSCAPEMODEL EN CONJUNTO CON ZEDBOARDMODEL PARA EL CASO<br>CON CARGA RL2 |       |

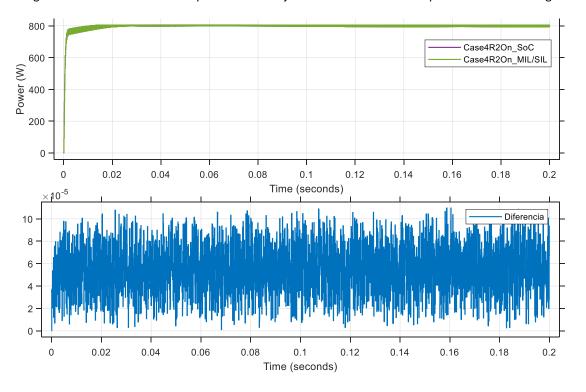

| FIGURA 84. SIMULACIÓN DE SIMSCAPEMODEL EN CONJUNTO CON ZEDBOARDMODEL PARA EL CASO<br>CON CARGA RL2 |       |

| FIGURA 85. SIMULACIÓN DE SIMSCAPEMODEL EN CONJUNTO CON ZEDBOARDMODEL PARA EL CASO<br>CON CARGA RL2 |       |

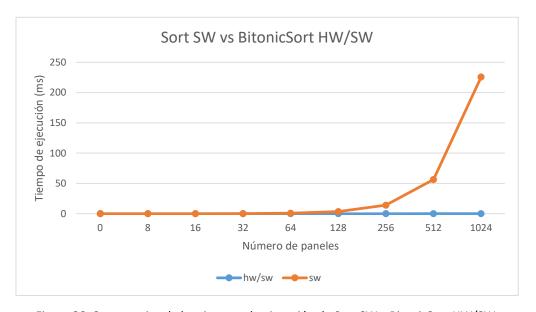

| FIGURA 86. COMPARATIVA DE LOS TIEMPOS DE EJECUCIÓN DE SORT SW Y BITONICSORT HW/SW                  | . 116 |

| FIGURA 87. CONEXIONADO DE LA ZEDBOARD CON LA ESTACIÓN DE TRABAJO                                   | . 131 |

| FIGURA 88. CONFIGURACIÓN DE LOS JUMPERS DE LA ZEDBOARD                                             | . 132 |

| FIGURA 89. VENTANA MANAGE ADD-ONS                                                                  | . 132 |

| FIGURA 90. HARDWARE SETUP: ELECCIÓN DE LA PLACA DE DESARROLLO                                      | . 133 |

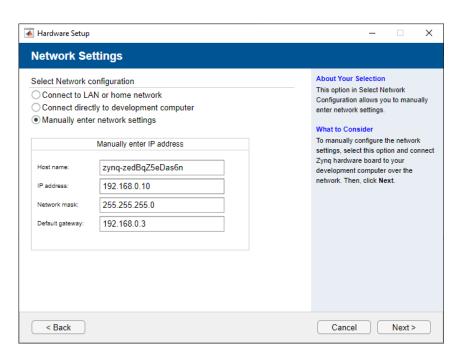

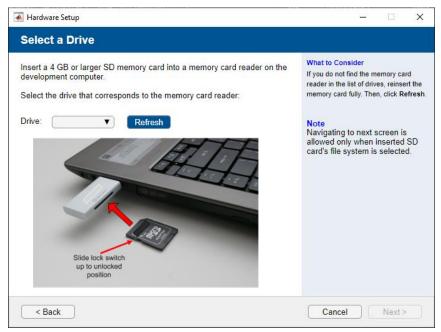

| FIGURA 91. HARDWARE SETUP: CONFIGURACIÓN DE RED DEL SISTEMA OPERATIVO                              | . 133 |

| FIGURA 92. HARDWARE SETUP: CARGA DE LA IMAGEN EN LA TARJETA SD                                     | . 134 |

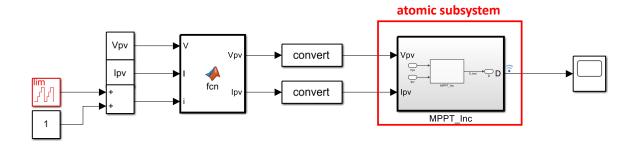

| FIGURA 93. TESTBENCH DEL CONTROLADOR MPPT.                                                         | . 135 |

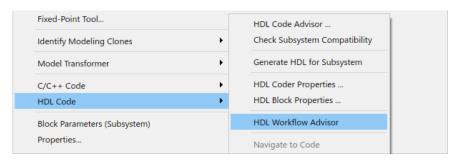

| FIGURA 94. LANZAMIENTO DE LA HERRAMIENTA HDL WORKFLOW ADVISOR                                      | . 135 |

| FIGURA 95. ELECCIÓN DE LA PLACA DE DESARROLLO Y NOMBRE DEL PROYECTO                                | . 136 |

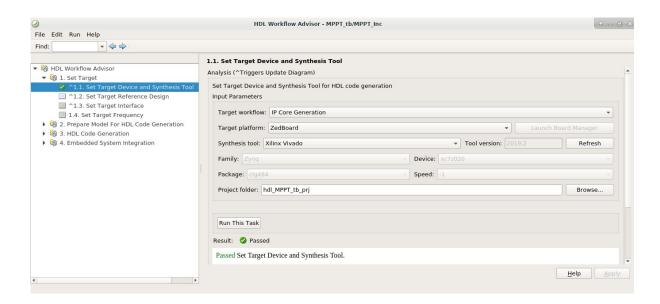

| FIGURA 96. SELECCIÓN DEL DISEÑO DE REFERENCIA                                                      | . 136 |

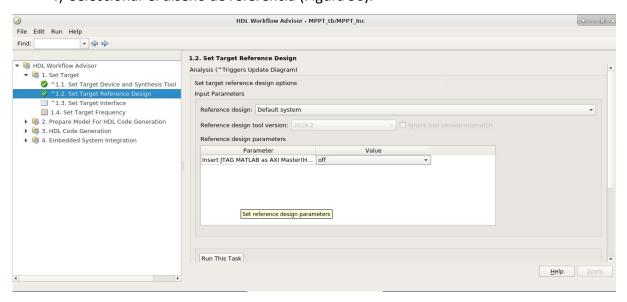

| FIGURA 97. SELECCIÓN DEL MODO DE FUNCIONAMIENTO E INTERFAZ DE ENTRADA/SALIDA DEL BLOC              |       |

| IP                                                                                                 | . 137 |

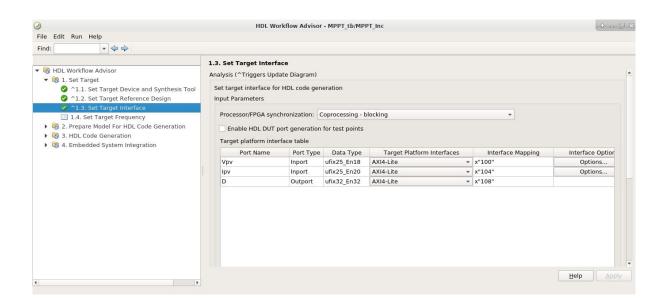

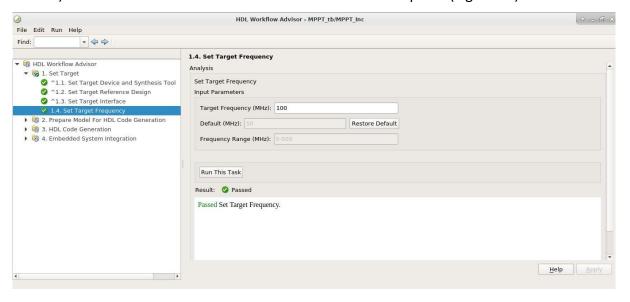

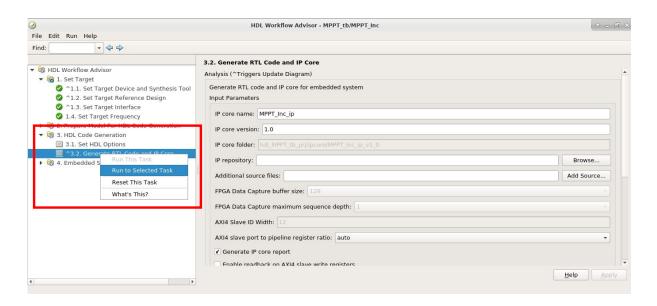

| FIGURA 98. SELECCIÓN DE LA FRECUENCIA DE FUNCIONAMIENTO | 137 |

|---------------------------------------------------------|-----|

| FIGURA 99. EJECUCIÓN ÍTEM 3.2 DEL HDL WORKFLOW ADVISOR  | 138 |

| FIGURA 100 MODELO SOFTWARE INTERFACE GENERADO           | 129 |

## Índice de Tablas

| TABLA 1. VENTAJAS Y DESVENTAJAS DE LAS DIFERENTES TECNOLOGÍAS DIGITALES (ADAPTADO DE [3]).                   | 3         |

|--------------------------------------------------------------------------------------------------------------|-----------|

| TABLA 2. ESTADOS POSIBLES DE LOS INTERRUPTORES DE LA MATRIZ DE INTERRUPTORES PARA UN <i>ARR</i><br>3 X 3     |           |

| TABLA 3. CASOS DE ESTUDIO DEL ALGORITMO MMTES                                                                | . 39      |

| TABLA 4. TIEMPO DE EJECUCIÓN DEL ALGORITMO MMTES EN MATLAB                                                   | . 39      |

| TABLA 5. VALORES DE IRRADIANCIA UTILIZADOS EN LA SIMULACIÓN MIL Y SIL                                        | . 69      |

| TABLA 6. CARGAS UTILIZADAS DURANTE LA SIMULACIÓN MIL Y SIL                                                   | . 69      |

| TABLA 8. COMPARATIVA DE RESULTADOS DE LA SIMULACIÓN MIL CON CARGA INDUCTIVA                                  | . 84      |

| TABLA 9. COMPARATIVA DE LAS POTENCIAS DE SALIDA OBTENIDAS EN LA SIMULACIÓN MIL Y SIL CON<br>CARGA RESISTIVA  | . 84      |

| TABLA 10. COMPARATIVA DE LAS POTENCIAS DE SALIDA OBTENIDAS EN LA SIMULACIÓN MIL Y SIL CON<br>CARGA INDUCTIVA | i<br>. 84 |

| TABLA 11. RESULTADOS DE CONVERSIÓN A PUNTO FIJO DE LA FUNCIÓN MPPT_INC                                       | . 91      |

| TABLA 12. CASO DE ESTUDIO 1                                                                                  | . 91      |

| TABLA 13. TIEMPOS DE EJECUCIÓN IP MMTESSORT                                                                  | . 95      |

| TABLA 14. TIEMPO DE EJECUCIÓN IP PAIRFORSWAPPING                                                             | . 95      |

| TABLA 15. TIEMPO DE EJECUCIÓN IP BITONICSORT                                                                 | . 96      |

| TABLA 16. TIEMPO DE EJECUCIÓN IP PAIRFORSWAPPINGPLL.                                                         | . 97      |

| TABLA 17. COMPARACIÓN TIEMPOS DE EJECUCIÓN MMTESSORT Y BITONICSORT                                           | . 97      |

| TABLA 18. COMPARACIÓN TIEMPOS DE EJECUCIÓN PAIRFORSWAPPING Y PAIRFORSWAPPINGPLL                              | . 98      |

| TABLA 19. DIRECCIONES DE MEMORIA DE LOS BLOQUES IP DESARROLLADOS 1                                           | 103       |

| TABLA 20. UTILIZACIÓN DE RECURSOS POR BLOQUE IP1                                                             |           |

| TABLA 21. CONSUMICIÓN DE POTENCIA DE LOS BLOQUES IP1                                                         | 104       |

| TABLA 22. COMPARATIVA DE LOS TIEMPOS DE EJECUCIÓN PARA LA IMPLEMENTACIÓN SOFTWARE Y<br>HARDWARE/SOFTWARE1    | 115       |

| TABLA 23. COMPARATIVA DE IMPLEMENTACIONES DE ALGORITMOS DPVAR SOBRE FPGA                                     | 120       |

| TABLA 24. COMPARATIVA DE IMPLEMENTACIONES DE CONTROLADORES MPPT SOBRE FPGA                                   | 121       |

# Índice de Códigos

| CÓDIGO FUENTE 1. | FUNCIÓN MMTESSORT       | 36 |

|------------------|-------------------------|----|

| CÓDIGO FUENTE 2. | FUNCIÓN PAIRFORSWAPPING | 37 |

| CÓDIGO FUENTE 3. | FUNCIÓN SWAPPAIR        | 38 |

| CÓDIGO FUENTE 4. | FUNCIÓN MPPT_INC        | 55 |

| CÓDIGO FUENTE 5. | FUNCIÓN AUXCTRL         | 65 |

#### **Acrónimos**

ASIC Application-Specific Integrated Circuit

AXI Advanced eXtensible Interface

CHB-MLI Cascade H-Bridge MultiLevel Invertir

CORDIC COordinate Rotation Digital Computer

CPU Central Processing Unit

DPVAR Dynamic Photovoltaic Array Reconfiguration

DSP Digital Signal Processor

EKF Extended Kalman Filter

FF Flip-Flop

FPGA Field Programmable Gate Array

FS-MPC Finite-State Model Predictive Control

GPU Graphics Processing Unit

GUI Graphical User Interface

HC Honey Comb

HDL Hardware Description Language

ILA Integrated Logic Analyzer

IP Intellectual Property

IUMA Instituto Universitario de Microelectrónica Aplicada

LUT Look Up Table

MIL Model-In-the-Loop

MMTES Maximum-Minimun Tier Equalisation Swapping

MPC Model Predictive Control

MPP Maximum Power Point

MPPT Maximum Power Point Tracker

MRR Modular Reconfigurable Robot

NREL National Renewable Energy Laboratory

P&O Perturb & Observe

PI Proportional Integral

PL Programmable Logic

PMSM Permanent Magnet Synchronous Motor

PS Processing System

PUMA Programmable Universal Manipulation Arm

PWM Pulse Width Modulation

RTL Register-Transfer Level

RTOS Real-Time Operating System

SCARA Selective Compliant Articulated Robot Arm

SCC Specialized Computational Cores

SICAD Sistemas Industriales y CAD

SIL Software-In-the-Loop

SMPS Switched Mode Power Supplies

SoC System on Chip

SPST Single Pole, Single Throw

SPWM Sinusoidal Pulse Width Modulation

SRAM Static Random-Access Memory

SVPWM Space Vector PWM

TCT Total Cross Tied

TFM Trabajo Fin de Máster

UDP User Datagram Protocol

ULPGC Universidad de las Palmas de Gran Canaria

USD United States Dollar

Very High Speed Integrated Circuit Hardware Description VHDL

Language

## Capítulo 1. Introducción

#### 1.1. Antecedentes

Debido a las propuestas de los nuevos paradigmas en la industria, tales como la industria 5.0 [1], se exige a los nuevos sistemas de control industrial un mejor rendimiento, mayor flexibilidad y un mayor grado de fiabilidad. Además, para mantener la competitividad en el mercado actual, el coste y el consumo de potencia de los controladores son puntos claves a tener en cuenta, introduciendo el ahorro energético como una exigencia adicional a las ya citadas.

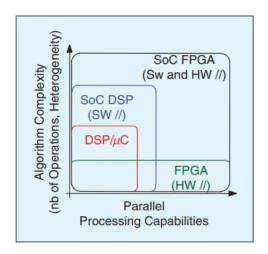

A la hora de implementar sistemas de control industrial en tiempo real eficientes, los diseñadores cuentan tradicionalmente con dos tecnologías principales de dispositivos digitales [2]. Por una parte, siguiendo una aproximación software, se utilizan microcontroladores y procesadores de señales digitales (DSP, Digital Signal Processors) y, por otra parte, una aproximación hardware, usando dispositivos FPGA (Field Programmable Logic Array). Existe una tercera vía que representa una solución hardware/software usando dispositivos SoC (System-on-Chip), que incluyen capacidad de procesamiento software y soporte para FPGA. En la Figura 1 se presentan las tecnologías citadas, comparando la complejidad algorítmica y capacidad de procesamiento en paralelo que son capaces de abordar.

Los microcontroladores y DSP son dispositivos digitales para los que se desarrolla una solución en el dominio *software*, estando formados principalmente por un microprocesador y varios periféricos, así como unidades de procesamiento especiales para

el caso de los DSP. Estos son los componentes con los que se realiza el control del sistema objetivo, así como los encargados de llevar a cabo las comunicaciones. Las ventajas que ofrece esta tecnología en las aplicaciones de control industrial son su flexibilidad y bajo coste. Entre sus desventajas podemos citar su alto consumo de potencia y la dificultad para aprovechar el paralelismo de los algoritmos de control que se implementan debido a su naturaleza secuencial.

Figura 1. Representación de la complejidad algorítmica y la capacidad de procesamiento paralelo para las distintas tecnologías de implementación de sistemas de control industrial [3].

Las FPGA, al contrario que los microcontroladores y DSP, son dispositivos para los que se desarrolla una solución principalmente en el dominio *hardware*. Este tipo de dispositivos proporcionan ventajas para aplicaciones en tiempo real exigentes en respuesta temporal (*hard real time*) frente a soluciones basadas en microprocesadores, como pueden ser su capacidad de procesamiento paralelo y el bajo consumo de potencia. Al implementar controladores utilizando esta tecnología, se consiguen tiempos de ejecución bajos gracias a que se aprovecha el paralelismo de los algoritmos de control implementándolos en *hardware*, consiguiendo además un tamaño y costo reducido.

La velocidad y el determinismo que se consiguen al realizar la implementación de los controladores en FPGA presenta ventajas importantes al trabajar con sistemas de control en red frente a las implementaciones basadas en microcontroladores. En los sistemas de control en red, el *software* de comunicación juega un papel importante, siendo frecuente sacrificar el rendimiento del controlador para lograr una implementación *software* conjunta del controlador y las comunicaciones. En caso de utilizar FPGA no existe esta

limitación, ya que se desarrolla una implementación *hardware* del controlador, lo que permite conseguir una gran mejora en el rendimiento del sistema diseñado.

Como se observa en la Figura 1, existen variantes *System on Chip* (SoC), de las tecnologías ya mencionadas, que presentan mejoras en la complejidad algorítmica y la capacidad de procesamiento en paralelo. Se aprecia sobre todo una mejoría en los SoC FPGA que mantienen la capacidad de procesamiento en paralelo, ganando mucha complejidad algorítmica y ofreciendo la posibilidad de desarrollar una implementación *hardware/software* de los algoritmos de control. Un ejemplo de SoC FPGA es la familia Zynq-7000 [4] de Xilinx que combina un doble núcleo ARM Cortex-A9 [5] con una FPGA de la serie 7 [6] de Xilinx junto con diversos periféricos. En la Tabla 1 se resumen las ventajas y desventajas de las diferentes tecnologías digitales comentadas con anterioridad.

Tabla 1. Ventajas y desventajas de las diferentes tecnologías digitales (adaptado de [3]).

| Criterio                                         | DSP/μC    | FPGA                                                  | SoC DSP                                            | SoC FPGA                              |

|--------------------------------------------------|-----------|-------------------------------------------------------|----------------------------------------------------|---------------------------------------|

| Perspectiva algorítmica                          | media     | media                                                 | buena                                              | muy buena                             |

| Gestión de la complejidad<br>algorítmica         | media     | media                                                 | buena                                              | muy buena                             |

| Rapidez, posibilidad de paralelismo              | media     | buena (Paralelismo<br>HW: concurrencia y<br>pipeline) | buena (Paralelismo<br>SW con múltiples<br>núcleos) | muy buena<br>(paralelismo SW y<br>HW) |

| Precisión (capacidad de punto flotante)          | muy buena | buena                                                 | muy buena                                          | SW: muy buena<br>HW: buena            |

| Conectividad                                     | media     | media                                                 | buena                                              | buena                                 |

| Interfaz analógica (ADC, DAC)                    | buena     | media                                                 | buena                                              | media                                 |

| Interfaz digital (número de E/S)                 | buena     | muy buena                                             | buena                                              | muy buena                             |

| Periféricos integrados                           | buena     | buena                                                 | muy buena                                          | muy buena                             |

| Sistema operativo integrado (acceso a Internet,) | media     | media                                                 | media                                              | muy buena                             |

| Flexibilidad de uso                              | buena     | buena                                                 | buena                                              | buena                                 |

| Facilidad de código                              | muy buena | buena                                                 | muy buena                                          | buena                                 |

| Adaptación de la microarquitectura               | mala      | muy buena                                             | media                                              | muy buena                             |

| Curva de aprendizaje                             | muy buena | buena                                                 | buena                                              | media                                 |

| Coste                                            | medio     | alto                                                  | medio                                              | alto                                  |

Entre las desventajas que presenta las soluciones basadas en FPGA frente a los DSP y los microcontroladores podemos citar su coste. Hoy en día, el coste de las FPGA es superior al de los DSP y microcontroladores, incluido el coste de diseño *hardware* implícito en la solución y de integración en los casos en que se utilicen soluciones *hardware/software*.

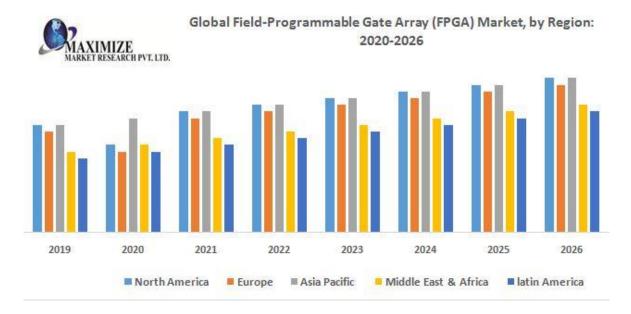

Hay que mencionar que se prevé un crecimiento en el mercado de las FPGA a medio plazo. En el año 2020, el mercado de las FPGA superó los 6 mil millones USD y se estima un crecimiento del 15% en el período de 2021 a 2027 [7]. En la Figura 2 se puede observar cómo las regiones de Norteamérica, Europa y Asia-Pacífico tienen un impacto mucho mayor en el mercado que el resto. De entre estas 3 regiones, se espera que el mercado de Asia-Pacífico sea el principal contribuidor al mercado mundial de las FPGA [8], seguido de cerca por el mercado norteamericano y el europeo.

Figura 2. Mercado global de FPGA por región 2020-2026 [8].

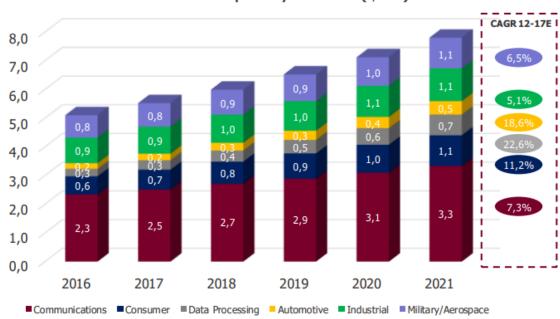

En la Figura 3 se muestra la división del mercado mundial por sectores (comunicaciones, consumidor, procesamiento de datos, automovilístico, industrial y militar/aeroespacial) en el período de 2016 a 2021. El sector predominante es el de las comunicaciones con mucha diferencia frente al resto. Le siguen en segunda posición los sectores militar/aeroespacial, industrial y consumidor y algo más rezagados el sector de procesamiento de datos y automovilístico.

#### FPGA market split by sector (\$bn)

Figura 3. División del mercado de FPGA por sectores [9].

El uso tanto de FPGA como SoC FPGA en aplicaciones de control es objeto de gran interés, ya que es una tecnología flexible que permite implementar algoritmos de control para diferentes procesos industriales. Entre los campos de aplicación más destacados se encuentran:

- a. Robótica ([10]-[12]).

- b. Controladores empotrados para aplicaciones industriales ([13]–[15]).

- c. Controladores para electrónica de potencia y sistemas de generación de energía eléctrica ([16]–[18]).

El campo de aplicación escogido para este TFM es el de controladores para electrónica de potencia y sistemas de generación de energía eléctrica. En concreto, se desarrolla un controlador para maximizar la producción de potencia de una instalación fotovoltaica que se encuentra afectada por sombras parciales. La implementación de este controlador se lleva a cabo siguiendo la metodología de diseño que se propone en este trabajo.

Dicha metodología consta de 3 puntos principales: la simulación MIL, la simulación SIL y la simulación *SoC in the Loop*. El funcionamiento de estas simulaciones se presenta en

detalle en el apartado 4.4 del Capítulo 4. Como se muestra en la Figura 4, todas estas simulaciones se llevan a cabo en conjunto con un modelo del sistema a controlar.

Figura 4. Modos de simulación de la metodología de diseño.

#### 1.2. Objetivos

El objetivo principal de este Trabajo Fin de Máster (TFM) consiste en validar la funcionalidad de la metodología de diseño de sistemas de control para dispositivos SoC FPGA que se presenta. Para ello se desarrolla un sistema de control para la producción de energía solar fotovoltaica desde modelos de alto nivel y se realiza su implementación sobre una placa de desarrollo usando dispositivos SoC FPGA Zynq.

Los objetivos operativos que se plantean son los siguientes:

O1. Estudio del estado del arte para los campos de aplicación y otras metodología de diseño existentes.

- O2. Definir la arquitectura del sistema de control y realizar su modelo de alto nivel en MATLAB.

- O3. Desarrollar los bloques de la arquitectura *hardware/software* para una implementación SoC FPGA.

- O4. Realizar la integración del sistema sobre un dispositivo SoC FPGA.

- O5. Validar, evaluar y documentar el trabajo realizado.

#### 1.3. Peticionario

Actúa como peticionario de este TFM la División de Sistemas Industriales y CAD (SICAD) del Instituto Universitario de Microelectrónica Aplicada (IUMA) de la Universidad de Las Palmas de Gran Canaria (ULPGC).

Igualmente, este TFM permite satisfacer los requisitos de la asignatura Trabajo Fin de Máster, dentro del plan de estudios del Máster en Electrónica y Telecomunicación Aplicadas impartido por el IUMA.

#### 1.4. Estructura del documento

En este primer capítulo se introduce al lector a los antecedentes y los objetivos planteados para este TFM. En el Capítulo 2 se realiza un análisis del estado del arte sobre el uso de FPGA en aplicaciones de control, haciendo hincapié en los campos de aplicación mencionados anteriormente, y sobre diferentes metodologías de diseño existentes. Tras realizar el análisis, en el Capítulo 3 se presenta el caso de implementación escogido para la verificación de la metodología de diseño.

En el Capítulo 4 se presenta la metodología de diseño propuesta, cuya funcionalidad se pretende validar, así como los recursos *software* y *hardware* que se precisan para esta tarea.

En el Capítulo 5 se introducen los algoritmos de reconfiguración dinámica de paneles fotovoltaicos (DPVAR, *Dynamic Photovoltaic Array Reconfiguration*) y se explica el funcionamiento y como se realiza la implementación del algoritmo escogido, así como su partición *hardware/software*.

En el Capítulo 6 se presentan los algoritmos de *Maximum Power Point Tracker* (MPPT) y se explica la implementación de la variante seleccionada.

En el Capítulo 7 se muestra el modelado del sistema a controlar en Simulink. Una vez se tiene este modelo se realiza la simulación *Model in the Loop* (MIL) y *Software in the Loop* (SIL) del algoritmo DPVAR y el controlador MPPT. Los resultados de las simulaciones se comparan para verificar el correcto funcionamiento del sistema.

En el Capítulo 8 se generan y se verifica el funcionamiento de los bloques IP correspondientes a la implementación en *hardware* del controlador MPPT y el algoritmo DPVAR.

En el Capítulo 9 se integran los bloques IP del controlador MPPT y del algoritmo DPVAR en una plataforma *hardware*. Dicha plataforma se vuelca sobre la placa de desarrollo y junto con la partición *software* del algoritmo DPVAR permite realizar una simulación *SoC in the Loop* y verificar el funcionamiento en conjunto del sistema sobre la placa de desarrollo.

Finalmente, se presentan los resultados y conclusiones obtenidas de la realización del proyecto y líneas de trabajo futuro, así como la bibliografía referenciada en el documento.

## Capítulo 2. Estado del arte

#### 2.1. Introducción

En este capítulo se hace un análisis del estado del arte en el uso de FPGA para la implementación de controladores en las áreas de robótica, controladores empotrados para aplicaciones industriales y electrónica de potencia y sistemas de generación de energía eléctrica y.

También, se presentan diferentes metodologías de diseño para realizar la implementación de algoritmos sobre tecnología FPGA.

#### 2.2. Uso de FPGA para sistemas de control en robótica

El campo de la robótica se puede beneficiar en gran medida del uso de FPGA, ya que usualmente los sistemas robóticos integran una gran variedad y cantidad de sensores que generan un alto número de datos a procesar en tiempo real.

En caso de tratarse de sistemas con recursos energéticos limitados, como pueden ser drones o vehículos autónomos, el consumo de energía del controlador es un aspecto clave. El uso de CPU y GPU en robótica está muy extendido. El consumo de potencia de estas plataformas de cómputo oscila entre los 10 W y los 100 W, lo cual es relativamente elevado para sistemas robóticos con recursos limitados [10].

El uso de FPGA en estas situaciones permite procesar una gran cantidad de datos en tiempo real, aprovechando las posibilidades de paralelización que ofrecen y consiguiendo un consumo de potencia inferior a otras plataformas de cómputo. Ejemplos de uso de FPGA

en sistemas robóticos con recursos limitados se encuentran en [11], donde Divya et al. presentan un entorno inteligente para el parking de vehículos robotizados de uso en interiores utilizando dispositivos SoC FPGA Zynq [12]. En dicho trabajo se revisan diferentes aplicaciones para vehículos autónomos basados en la implementación de inteligencia artificial sobre FPGA. En esta misma línea, Yakun et al. [19] realizan la implementación de un algoritmo DS-SLAM de alta eficiencia energética sobre una plataforma heterogénea basada en FPGA.

Recientemente se han utilizado también FPGA, además de otras tecnologías, para implementar el cálculo del gradiente de la dinámica de cuerpos rígidos. Esta es una operación clave en la planificación del estado del arte y en los algoritmos de control para robótica [20].

La robótica modular, donde la dinámica de cada módulo se calcula por un controlador empotrado local, se beneficia del uso de FPGA. Esto se puede ver en [21] donde se consiguen frecuencias de muestreo mayores que utilizando un sistema centralizado.

Otros ejemplos de uso de FPGA en robótica modular aparecen en [22] donde Vinzenz Bargsten et al. proponen un método para el cálculo distribuido de la dinámica de movimiento de sistemas robóticos utilizando FPGA. Romanov et al. [23] proponen un nuevo enfoque de organización de un sistema de computación distribuida, basado en núcleos de computación especializados (SCCs) sobre FPGA para robots modulares reconfigurables (MRR). Además, la flexibilidad que ofrecen los SoC FPGA junto con la filosofía de la robótica modular, permite modificar fácilmente estos sistemas modulares [24].

En el ámbito de la robótica industrial también se pueden encontrar distintos casos de uso de FPGA. En [25] se presenta el desarrollo de un bloque IP para el cálculo de la cinemática directa e inversa de un robot SCARA (Figura 5). De igual forma, en [26] se mejora el movimiento mediante el desarrollo de un controlador basado en FPGA para robots industriales de arquitectura abierta. En [27] se describe el desarrollo de un controlador de arquitectura abierta para el robot PUMA 560 (Figura 6). Por último se presenta el desarrollo de un controlador basado en FPGA para robots colaborativos [28].

Figura 5. Robot SCARA [29].

Figura 6. PUMA 560 [30].

# 2.3. Controladores empotrados para aplicaciones industriales basados en FPGA

Algunas de las aplicaciones más interesantes para sistemas empotrados son las relacionadas con la industria de la automoción y la industria aeroespacial. Los controladores que se desarrollan para estas aplicaciones deben cumplir en muchos casos especificaciones de tiempo real y para ello es muy frecuente que precisen de una alta capacidad computacional. Es por esto, que el uso de FPGA se ha incrementado notablemente en estos campos de aplicación [13].

Tanto para la industria automovilística como para la aeroespacial, el uso de controladores predictivos basados en modelo (*Model predictive Control*, MPC) ha cobrado gran relevancia, como se puede observar en las distintas publicaciones existentes, entre las que destacan [14], [15], [31], [32]. Estos son controladores capaces de trabajar con sistemas de múltiples variables y cuyo fin es resolver un problema de optimización para determinar la acción de control. En estos campos de aplicación el controlador MPC debe ser capaz de resolver el problema de optimización en tiempo real, generalmente en condiciones *hard-real time*. Al implementar estos controladores sobre FPGA, se puede aprovechar la capacidad de cómputo en paralelo que ofrecen estos dispositivos para lograr alcanzar los altos requerimientos [33].

Algunos casos de aplicación dentro de la industria aeroespacial se presentan a continuación. En [34] Hartley et al. implementan un MPC sobre FPGA para el control de un Boeing 747. Los mismos autores muestran en [35] la implementación de un MPC sobre FPGA y demuestran su funcionamiento con una simulación *FPGA-in-the-loop* en la que se controla una simulación no lineal de un avión de pasajeros de gran escala.

En la industria de la automoción también se pueden encontrar ejemplos de aplicación de MPC sobre FPGA. En [36], Reda et al. describen la implementación para realizar el control de la dirección automática en vehículos. Guo et al. [37] presentan el control de la estabilidad lateral del chasis activo de vehículos inteligentes. Dentro de esta misma línea, en [38] Petrelli presenta la implementación una plataforma para la realización del control necesario para evadir obstáculos y seguir una trayectoria a partir de la lectura de sensores, respetando las restricciones especificadas. Como se puede apreciar todas las aplicaciones se utilizan para sistemas críticos del automóvil.

En estos sistemas empotrados destinados a aplicaciones en el ámbito de la automoción o la aviación, la seguridad es un punto clave. En [39], Falk Salewski y Stefan Kowalewski llevan a cabo una comparativa entre microcontroladores y FPGA con respecto a sus propiedades de seguridad y fiabilidad en el ámbito de la automoción. Como resultado se muestra que las FPGA presentan ventajas en cuanto al encapsulamiento de funciones en tiempo real. Para reforzar el aspecto de la seguridad, en [40] Philippa Conmy e lain Bate muestran cómo puede ser analizado un diseño modular empotrado sobre FPGA con el fin

de derivar las propiedades de fallo y seguridad para dar la evidencia necesaria para un caso de seguridad.

# 2.4. Control basado en FPGA para electrónica de potencia y sistemas de generación de energía eléctrica

El uso de FPGA en los sistemas electrónicos de potencia es de especial interés cuando se requiere un alto grado de paralelismo en la aplicación. Un ejemplo de aplicación donde se aprovecha esta característica se muestra en [16], donde se realiza una implementación hardware de un algoritmo de modulación por ancho de pulso del vector espacial (multilevel multiphase space vector PWM, SVPWM) para un convertidor de voltaje multinivel polifásico o en [17] donde se implementa la técnica de modulación por ancho de pulso sinusoidal (sinusoidal pulse width modulation, SPWM) para controlar un inversor multinivel de puentes H de 5 niveles (H-Bridge multilevel invertir, CHB-MLI). A la hora de trabajar con frecuencias de muestreo muy elevadas, el uso de FPGA también gana importancia. Esto ocurre al trabajar con fuentes conmutadas (SMPS) de baja tensión, tal como se presenta en [18].

Los dispositivos FPGA también se utilizan en electrónica de potencia para realizar el control de motores. Por ejemplo, para motores síncronos de imanes permanentes (PMSM) existen varias publicaciones sobre diferentes controladores. En [41] se propone un controlador compensador basado en filtros Kalman extendidos (*Extended Kalman Filters*, EKF) para mejorar las prestaciones del controlador proporcional integral (PI) ya implementado.

En [42] se desarrolla un controlador de corriente basado en control predictivo de estados finitos (*Finite-State Model Predictive Control*, FS-MPC). Se decide implementar sobre FPGA para explotar el paralelismo del algoritmo de control y conseguir una implementación que cumpla con especificaciones de tiempo real.

De igual manera, en [43] se propone otra aproximación para desarrollar un controlador de corriente basado en control predictivo por modelo (MPC), que se decide implementar en FPGA debido al alto coste computacional.

Finalmente en [44] se utiliza un sistema digital para la rotación de coordenadas (Coordinate Rotation Digital Computer, CORDIC) implementada sobre una FPGA para hacer la estimación de la posición y velocidad de un motor PMSM.

Los dispositivos FPGA también se utilizan para desarrollar controladores para sistemas de generación de energía eléctrica. Por ejemplo en, [3] se presentan 2 casos diferentes de control de sistemas eléctricos. El primero es el control, estimación y prognosis de un sistema de células de combustible (*Fuel Cells*, FC) híbrido y el segundo es la reconfiguración dinámica de módulos de energía solar fotovoltaica afectados por sombras parciales. En [45] se sigue en la línea del segundo caso y se implementa también un algoritmo de este tipo.

En FPGA también se pueden implementar los controladores MPPT que se utilizan en sistemas de generación eléctrica basado en turbinas eólicas o paneles fotovoltaicos. Estos controladores maximizan la extracción de potencia independientemente de las condiciones ambientales. Ejemplos de implementación de diferentes tipos de MPPTs sobre FPGA se pueden observar en las publicaciones [46]–[49].

#### 2.5. Metodologías de diseño

Existen varías metodologías de diseño diferentes para llevar a cabo la implementación de algoritmos sobre tecnología SoC FPGA. Por ejemplo, en [50] Monmasson et al. presentan una metodología de diseño basada en tres aspectos principales: refinamiento del algoritmo, modularidad y optimización de la implementación.

Con el refinamiento del algoritmo se busca su adaptación a una implementación sobre FPGA cambiando, por ejemplo, la aritmética en coma flotante por punto fijo. Por otro lado, la modularidad disminuye el ciclo de diseño en sistemas complejos ya que maximiza la reutilización de los módulos diseñados. Finalmente, se propone utilizar la metodología A<sup>3</sup> (*Algorithmic Architecture Adequation*) [51] para encontrar la arquitectura *hardware* óptima del algoritmo que se quiere implementar para que cumpla con las restricciones de tiempo y área establecidas.

Otro ejemplo de metodología se presenta en [52], donde se describen los pasos necesarios para, a partir de la implementación HDL del algoritmo deseado, obtener el *bitstream* de programación de la FPGA. Los pasos a seguir en esta metodología para generar el *bitstream* son: síntesis, implementación, mapeado, colocado de bloques e interconexionado. Esta es una metodología similar a la que se sigue en Vivado Design Suite para generar el *bitstream* de programación de la FPGA.

También existen metodologías diseñadas para herramientas específicas como puede ser MATLAB/Simulink. Por ejemplo, en [53] se presenta una metodología de diseño en la que se implementa el algoritmo deseado en Simulink y se genera código VHDL a partir de este. Para verificar el funcionamiento del código generado, se realiza su co-simulación con ayuda de un simulador HDL. Por otro lado, en [54] se propone una metodología que combina la síntesis de alto nivel mediante Vivado HLS con MATLAB/Simulink. En esta metodología se implementa el algoritmo deseado en C/C++/SystemC y se utiliza Vivado HLS para generar el bloque IP correspondiente al algoritmo. Tras esto, se verifica el funcionamiento del bloque IP en Simulink mediante una co-simulación con un simulador HDL de manera similar a [53].

#### 2.6. Conclusiones

En este capítulo se ha realizado el estudio de distintos trabajos presentes en la literatura en relación con los sistemas de control basados en dispositivos FPGA, mostrando sus ventajas y desventajas para aplicaciones en el ámbito industrial, incluida la generación de energías renovables y el transporte inteligente. También se han presentado diversas variantes de metodologías de diseño para dispositivos SoC FPGA.

## Capítulo 3. Caso de implementación

#### 3.1. Introducción

En este capítulo se presenta el área de aplicación y el caso de implementación escogidos. El caso de implementación estudiado en este capítulo se utiliza como caso práctico para verificar la funcionalidad de la metodología de diseño que se propone en el Capítulo 4.

#### 3.2. Área de aplicación

En el área de aplicación de controladores para electrónica de potencia y generación de energía eléctrica se ha optado por implementar un algoritmo DPVAR, junto con un controlador MPPT.

Existen varios ejemplos de implementación de diversas variantes de controladores MPPT sobre tecnología FPGA ([46]–[49]), mostrando la viabilidad de la tecnología FPGA para la implementación de este tipo de controladores. Por otro lado, existen también algunos casos de implementación de algoritmos DPVAR sobre SoC FPGA ([55]).

Los dispositivos SoC FPGA representan un buen candidato para la implementación de este tipo de algoritmos debido a la flexibilidad que ofrecen. Generalmente los algoritmos DPVAR son complejos y conllevan un alto coste computacional. Poder realizar una implementación hardware/software de estos algoritmos permite, por ejemplo, implementar en C/C++ sobre el procesador integrado las partes más secuenciales del algoritmo y en hardware las partes de mayor coste computacional. En la partición hardware

del algoritmo se explota el paralelismo existente para conseguir reducir el tiempo de ejecución total frente a una implementación puramente *software*.

#### 3.3. Caso de estudio

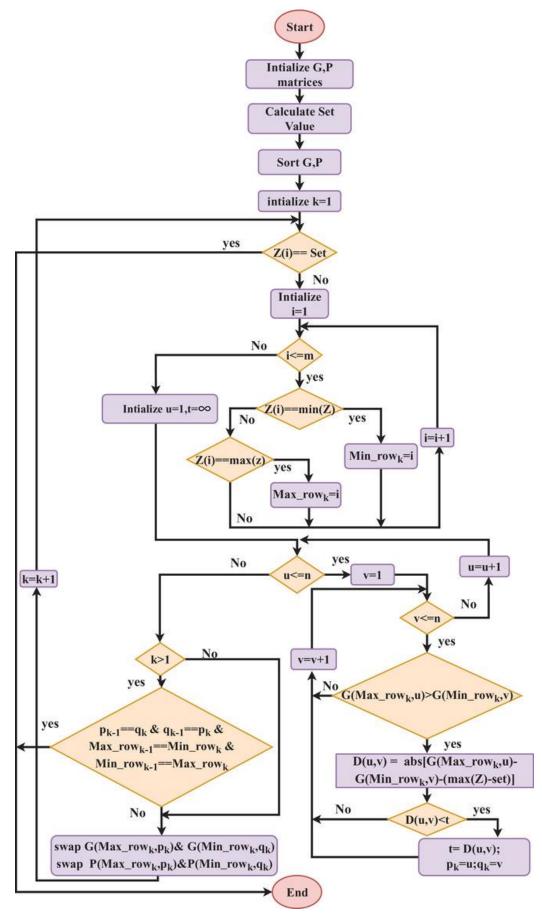

El algoritmo DPVAR que se escoge implementar es el que se presenta en [56]. Este es un algoritmo relativamente nuevo y que no ha sido implementado aún sobre tecnología SoC FPGA. Se ha elegido este algoritmo porque se han identificado varias partes que se pueden implementar de forma paralela en *hardware* y mejorar así el tiempo de ejecución total. En conjunto con el algoritmo DPVAR se implementa un controlador MPPT de conductancia incremental.

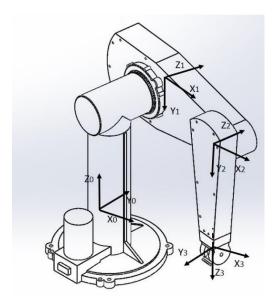

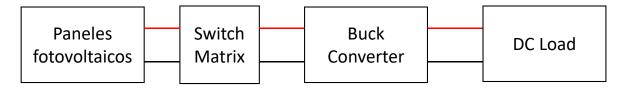

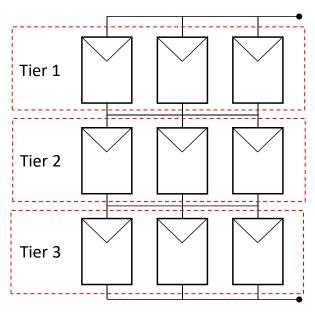

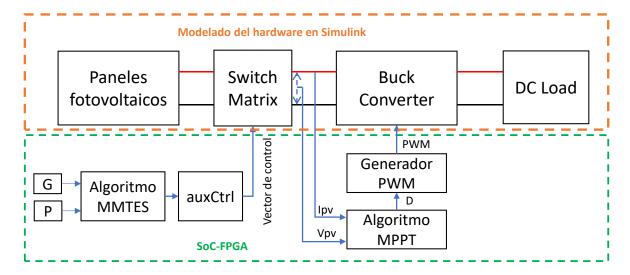

El funcionamiento del algoritmo DPVAR y el controlador MPPT se simula en conjunto con el modelo del sistema a controlar (Figura 7). Está formado por un *array* de nueve paneles fotovoltaicos, una matriz de interruptores, un convertidor reductor (*Buck Converter*) y una carga. El modelo del sistema a controlar se presenta con mayor detalle en el Capítulo 7.

Figura 7. Diagrama de bloques del modelo del sistema controlar.

#### 3.4. Conclusiones

En este capítulo se ha presentado el área de aplicación escogida, así como el caso de implementación. Se justifica la implementación del algoritmo DPVAR elegido sobre SoC FPGA debido a la capacidad de explotar el paralelismo que ofrece el mismo al utilizar esta tecnología.

### Capítulo 4. Metodología de diseño

#### 4.1. Introducción

En este capítulo se presenta la metodología de diseño que se propone junto con las herramientas necesarias para implementarla. En primer lugar, se introduce MATLAB/Simulink, entorno que se utiliza para realizar la implementación del algoritmo DPVAR y el controlador MPPT y verificar su correcto funcionamiento. A continuación, se explica brevemente la herramienta de implementación del diseño, Xilinx Vivado Design Suite. Por último, se presenta paso a paso la metodología de diseño propuesta en este TFM para sistemas de control sobre dispositivos SoC FPGA.

#### 4.2. MATLAB/Simulink

MATLAB (MATrix LABoratory) [57] es un entorno de programación y cálculo numérico. Entre sus muchas aplicaciones se encuentran el desarrollo de algoritmos, análisis de datos o generación automática de código. El lenguaje de programación de MATLAB está basado en matrices y puede ser convertido automáticamente en código C/C++ y HDL.

Simulink [58] provee un entorno gráfico basado en bloques en el que se pueden realizar simulaciones multidominio y diseño basado en modelos. Entre las capacidades con las que cuenta esta herramienta están la generación automática de código, la realización de simulaciones y la comprobación y verificación de sistemas integrados.

MATLAB y Simulink son herramientas diseñadas para trabajar en conjunto. Se puede hacer uso de los algoritmos diseñados en MATLAB en los modelos creados en Simulink y a

su vez, se pueden exportar los datos generados en las simulaciones realizadas en Simulink a MATLAB para su análisis.

MATLAB y Simulink cuentan con una gran variedad de *Add-Ons* denominados *toolbox*. Estos *toolbox* permiten añadir funcionalidades al entorno como, por ejemplo, la posibilidad de generar bloques IP para dispositivos FPGA a partir de algoritmos desarrollados en MATLAB/Simulink.

A continuación, se describe la funcionalidad de los diferentes *toolbox* que son necesarios para realizar la implementación del algoritmo DPVAR y el controlador MPPT.

#### 4.2.1. Simscape Electrical

Simscape Electrical [59] es un *toolbox* de Simulink que proporciona diversas librerías de componentes que permiten modelar y simular sistemas electrónicos, mecatrónicos y de potencia. En estas librerías se encuentran modelos de semiconductores, generadores de energías renovables o motores entre otros.

En este TFM se utilizan diversos componentes de estas librerías para modelar el sistema fotovoltaico a controlar.

#### 4.2.2. Fixed-Point Designer

Fixed-Point Designer [60] es un *toolbox* que proporciona herramientas para generar código en punto fijo o punto flotante a partir de algoritmos generados en MATLAB/Simulink. También permite optimizar e implementar código para *hardware* empotrado.

En este TFM se utiliza la aplicación Fixed-Point Converter proporcionada por el *toolbox* Fixed-Point Designer para generar una implementación en punto fijo de la partición *hardware* del algoritmo DPVAR y el controlador MPPT que se desarrollan en MATLAB/Simulink.

#### 4.2.3. MATLAB Coder

MATLAB Coder [61] es un *toolbox* que permite generar código C/C++ a partir de código en lenguaje MATLAB. Admite la mayoría de las expresiones del lenguaje MATLAB y

una gran variedad de *toolboxes*. El código que se genera es portable y se puede combinar con código C/C++ ya existente.

#### 4.2.4. Simulink Coder

Simulink Coder [62] es un *toolbox* que ejecuta y genera código C/C++ de modelos de Simulink, gráficos de Stateflow y funciones de MATLAB. El código generado se puede usar, por ejemplo, en aplicaciones con o sin especificaciones de tiempo real o comprobaciones *Hardware-in-the-Loop*.

#### 4.2.5. Embedded Coder

Embedded Coder [63] es un *toolbox* que complementa a MATLAB Coder y Simulink Coder y permite generar código C/C++ leíble, compacto y rápido para procesadores empotrados. También añade optimizaciones para mejorar la eficiencia del código y la facilidad de su integración con código previamente existente.

#### 4.2.6. HDL Coder

HDL Coder [64] es un toolbox que permite generar código Verilog y VHDL portable y sintetizable a partir de funciones de MATLAB, modelos de Simulink y gráficos Stateflow. El código generado se puede utilizar para programar FPGA o prototipar en ASICs. HDL Coder provee un flujo de trabajo que automatiza y guía en la tarea de programar FPGA de Xilinx, Microsemi e Intel. El código generado por HDL Coder tiene trazabilidad con el modelo de Simulink facilitando la verificación de este.

#### 4.2.7. HDL Coder Support Package for Xilinx Zynq Platform

HDL Coder Support Package for Xilinx Zynq Platform [65] es un paquete adicional del toolbox HDL Coder. Permite generar bloques IP que se pueden exportar a Xilinx Vivado o Vivado ISE y realizar diseños para dispositivos de la plataforma Zynq de Xilinx.

#### 4.2.8. Embedded Coder Support Package for Xilinx Zyng Platform

Embedded Coder Support Package for Xilinx Zynq Platform [66] es un paquete adicional del toolbox Embedded Coder. Permite generar código ANSI C a partir de funciones de MATLAB, gráficos Stateflow y modelos de Simulink para los núcleos ARM de los dispositivos SoC Xilinx Zynq.

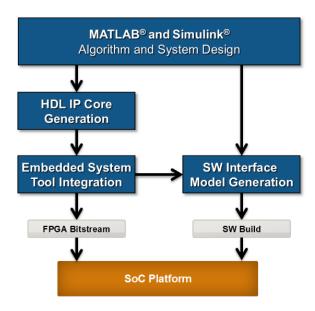

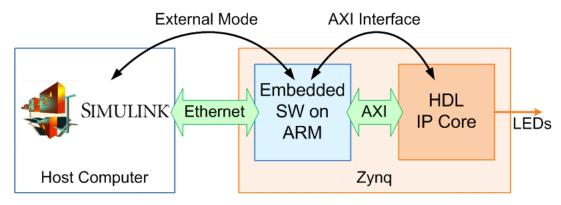

Si se usa en combinación con HDL Coder Support Package for Xilinx Zynq Platform, se puede programar directamente el dispositivo Xilinx Zynq con el código C y HDL generado siguiendo el codiseño *hardware/software* (Figura 8). Esto permite realizar simulaciones, verificar el funcionamiento del código y los bloques IP y realizar la implementación final.

Figura 8. Codiseño hardware/software para plataformas SoC [67].

#### 4.3. Herramientas de síntesis e implementación para FPGA

En la síntesis lógica se obtiene la implementación del diseño a nivel lógico a partir de las especificaciones de funcionamiento RTL, es decir, se generan las puertas lógicas a partir del RTL. A la fase de síntesis le sigue una fase de implementación y de generación del *bitstream*. Todo este proceso es dependiente de la tecnología y por tanto será necesario utilizar los entornos de los fabricantes de los dispositivos FPGA. Para este TFM se utilizan dispositivos Zynq de Xilinx, por lo que se utilizará Vivado Design Suite.

#### 4.3.1. Xilinx Vivado Design Suite

Xilinx Vivado Design Suite [68] tiene una *Graphical User Interface* (GUI) que permite realizar diferentes tareas de diseño y crear la plataforma *hardware* donde se implementan los diferentes bloques IP desarrollados. Igualmente, dispone de la posibilidad de trabajar en modo de línea de comandos.

La implementación de la plataforma *hardware* se realiza en varias etapas. Estas etapas son el análisis, la síntesis lógica y la implementación. En todo momento, durante la ejecución de estas etapas, se pueden realizar mejoras en el consumo de recursos, consumo de potencia y prestaciones temporales. Tras cumplir con estas tres etapas, el siguiente paso es la generación del *bitstream*. Mediante este *bitstream* se programa la FPGA con la plataforma *hardware* diseñada.

Para la implementación final hay que tener en cuenta que la programación de las FPGA de Xilinx es volátil debido a que utilizan tecnología basada en SRAM. Por lo tanto, para poder asegurar el funcionamiento tras una pérdida de la alimentación del sistema, hay que descargar el *bitstream* en una tarjeta SD o memoria Flash para que el sistema puede arrancar correctamente al reiniciarlo.

#### 4.4. Metodología de diseño

La metodología propuesta comienza con el diseño en MATLAB/Simulink de los algoritmos que se quieren implementar en el SoC FPGA. A continuación, se procede a realizar el modelado de la planta a controlar en Simulink, para lo cual se utilizan bloques pertenecientes al *toolbox* Simscape Electrical. Con el modelo de la planta se realiza la simulación *Model in the Loop* (MIL) (Figura 9), que consiste en simular conjuntamente los algoritmos diseñados en MATLAB/Simulink con el modelado de la planta creado [69]. Con ello se verifica el correcto funcionamiento de los algoritmos. Si el resultado de la simulación MIL es satisfactorio, se puede pasar al siguiente paso.

Figura 9. Simulación MIL.

Tras la simulación MIL, el siguiente paso es realizar la simulación *Software in the Loop* (SIL) (Figura 10). Consiste en generar código C/C++ a partir de los algoritmos diseñados en MATLAB/Simulink mediante el *toolbox* Simulink Coder y simular su funcionamiento en conjunto con el modelado del sistema [70]. El objetivo de la simulación SIL es verificar que MATLAB es capaz de generar código C/C++ a partir de los algoritmos diseñados, que este funciona de manera análoga a los algoritmos originales y que es implementable en *hardware*. En caso de que los resultados de simulación no sean satisfactorios, se revisa el diseño de los algoritmos para asegurar que se pueda generar código y que sean implementables en *hardware*.

Figura 10. Simulación SIL.

Finalizada la simulación SIL, se realiza la generación de bloques IP. En este punto se genera código HDL, VHDL o Verilog, y se crean los bloques IP para aquellas partes de los algoritmos diseñados que se quieran implementar en la lógica programable de la FPGA. Para ello, primero se genera una implementación en punto fijo de las partes destinadas a implementarse en *hardware* mediante el *toolbox* Fixed-Point Designer y tras esto se generan los bloques IP mediante el *toolbox* HDL Coder. Para verificar el funcionamiento de los bloques IP generados, se exportan a Vivado Design Suite donde se genera el *bitstream* con el que programar la FPGA. Una vez programada la FPGA y gracias a los *Support Package* del *toolbox* HDL Coder, se puede realizar la simulación *SoC in the Loop* (Figura 11). El fin de esta simulación es verificar el correcto funcionamiento de los bloques IP diseñados, que

han sido programados en la FPGA, simulando su funcionamiento en conjunto con el modelo del sistema en Simulink.

Figura 11. Simulación SoC in the Loop.

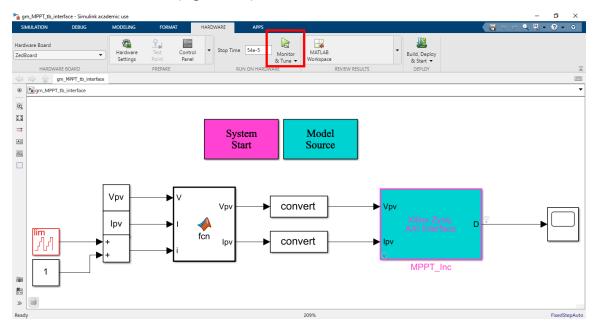

Por último, se realiza una simulación *SoC in the Loop* del sistema al completo con el modelo de la planta creado en Simulink. Para ello se crea en Vivado Design Suite una plataforma *hardware* que integre todos los bloques IP desarrollados, se genera el *bitstream* y se programa la FPGA. A continuación, desde Simulink se genera el código ANSI C de la parte *software* de los algoritmos diseñados mediante el *toolbox* Embedded Coder y se carga en el procesador de la plataforma SoC FPGA. Hecho esto, se simula el funcionamiento del sistema en conjunto con el modelo de la planta. Si la simulación es satisfactoria, el flujo de diseño concluye.

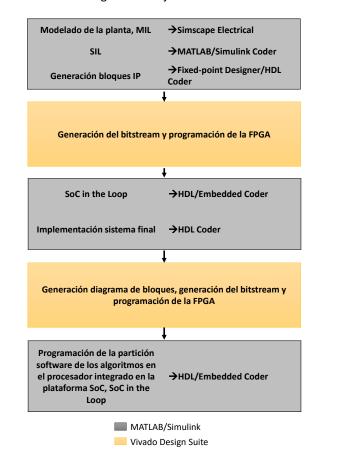

En la Figura 12 se ilustra la metodología presentada mediante un diagrama de flujo. En la Figura 13 se relaciona de forma gráfica los pasos que constituyen el flujo de diseño propuesto, con las herramientas presentadas en los apartados 4.2 y 4.3 necesarias para llevarlos a cabo.

Figura 12. Flujo de diseño.

Figura 13. Distribución de los pasos del flujo de diseño según las herramientas necesarias.

#### 4.5. Conclusiones

En este capítulo se han introducido las diferentes herramientas necesarias y se ha descrito el flujo de diseño para poder realizar la implementación de un controlador MPPT y un algoritmo DPVAR sobre un dispositivo SoC FPGA siguiendo la metodología de diseño propuesta.

Por otro lado, se ha expuesto la metodología de diseño a seguir y se ha explicado, con la ayuda de un diagrama de flujo, cada uno de los pasos que hay que realizar para llevarla a cabo.

# Capítulo 5. Algoritmo de reconfiguración dinámica de paneles fotovoltaicos

#### 5.1. Introducción

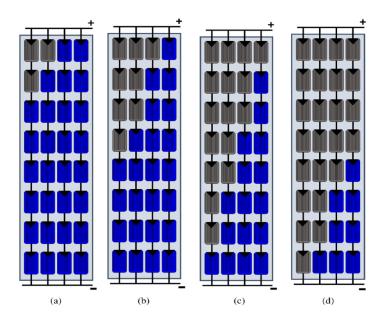

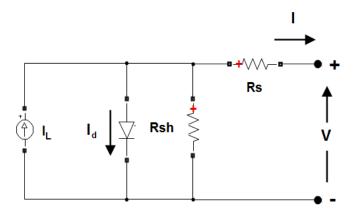

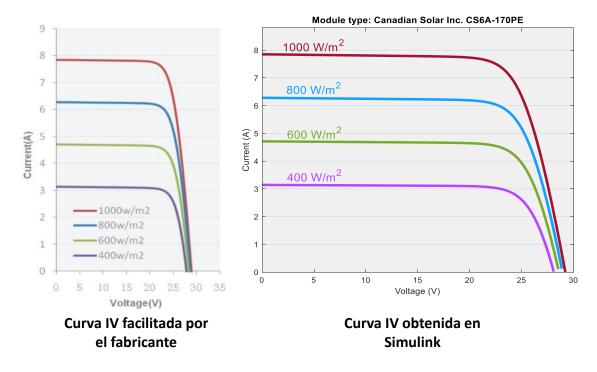

El rendimiento de una instalación fotovoltaica se puede ver afectado por diversos motivos, como por ejemplo la aparición de sombras que afecten a un determinado número de paneles fotovoltaicos de la instalación. Un ejemplo se puede ver en la Figura 14, donde los paneles afectados por sombras están remarcados en gris. Esto se denomina sombras parciales y pueden ser provocadas por nubes, árboles, antenas de telefonía móvil, etc. Las sombras parciales afectan sobre todo a instalaciones fotovoltaicas de gran extensión haciendo que la curva característica de ésta sea más compleja, lo que dificulta optimizar la producción de potencia [71].