#### Instituto Universitario de Microelectrónica Aplicada

## Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

#### Trabajo Fin de Máster

Implementación MPSoC FPGA de Algoritmos de *Machine*Learning para Aplicaciones Clínicas usando Metodologías

de diseño de Alto Nivel

Autor: Mario Daniel Guanche Hernández

Tutor(es): Pedro Pérez Carballo

Sonia Raquel León Martín

Fecha: mayo de 2023

#### Instituto Universitario de Microelectrónica Aplicada

## Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

### Trabajo Fin de Máster

Implementación MPSoC FPGA de Algoritmos de *Machine Learning* para Aplicaciones Clínicas usando Metodologías

de diseño de Alto Nivel

#### **HOJA DE FIRMAS**

Alumno/a: Mario Daniel Guanche Hernández Fdo.:

Tutor/a: Pedro Pérez Carballo Fdo.:

Tutor/a: Sonia Raquel León Martín Fdo.:

Fecha: mayo de 2023

#### Instituto Universitario de Microelectrónica Aplicada

## Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

#### Trabajo Fin de Máster

Implementación MPSoC FPGA de Algoritmos de *Machine Learning* para Aplicaciones Clínicas usando Metodologías

de diseño de Alto Nivel

#### **HOJA DE EVALUACIÓN**

| Calificación:    |           |

|------------------|-----------|

| Presidente       | <br>Fdo.: |

| Secretario       | <br>Fdo.: |

| Vocal            | <br>Fdo.: |

| Fecha: mayo 2023 |           |

## **Agradecimientos**

A mi familia por su apoyo incondicional.

A mis tutores, Pedro Francisco Pérez Carballo y Sonia Raquel León Martín, por el asesoramiento.

Al servicio de soporte técnico del IUMA, por asistirme en la instalación e instrucciones requeridas para el uso de las aplicaciones en este trabajo.

#### Resumen

En este Trabajo Fin de Máster (TFM) se estudia la utilización de aceleradores hardware basados en MPSoC (Multiprocessor System on Chip) FPGAs (Field-programmable Gate Array) aplicados para preprocesar imágenes hiperespectrales con fines médicos, más concretamente para diagnosticar posibles casos de cáncer de piel. Para que las imágenes hiperespectrales resulten útiles, su contenido debe preprocesarse. Con ello, se minimiza en dicha información la influencia de factores ajenos a la naturaleza de la imagen.

Tras el preprocesado, pueden utilizarse las imágenes hiperespectrales resultantes para extraer conclusiones acertadas, automatizadas y útiles para el caso de uso. Para ello, el uso de algoritmos de *machine learning* resulta de gran idoneidad. En este TFM, se considera el algoritmo "k-means", que se emplea para determinar regiones en la piel captada en la imagen según sea tejido sano o afectado.

El preprocesado de imágenes hiperespectrales y el algoritmo "k-means" requieren una carga computacional elevada en una ejecución secuencial. Por ello, resulta muy conveniente implementar aceleración *hardware* que explote las posibilidades de paralelismo de estos algoritmos, reduciendo con ello su tiempo de ejecución y su consumo energético.

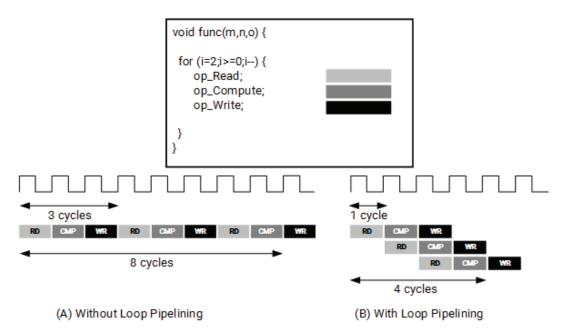

Para lograr dicha aceleración, se utilizan dispositivos MPSoC FPGAs sobre un sistema de prototipado Xilinx Zynq UltraScale+ MPSoC ZCU102. Su elemento central es un MPSoC que contiene, entre otros recursos, un sistema de multiprocesamiento y una FPGA con lógica programable (PL, *Programmable Logic*).

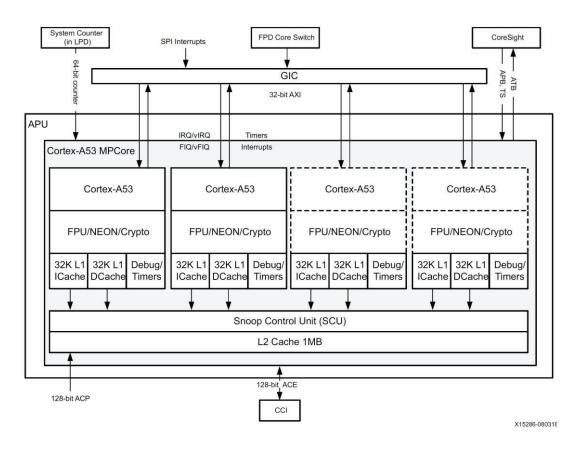

La aplicación hardware/software a implementar está formada por una aplicación software (app.) ejecutada como host y funciones de aceleración hardware o kernels. El host se ejecuta en la APU (Application Processor Unit) basada en un sistema de multiprocesamiento ARM Cortex A53. Los kernels se ejecutan en la FPGA. Para comunicar datos y control entre la APU la FPGA se utiliza un sistema de buses en chip basados en interfaces AMBA AXI4 configurables de alto ancho de banda disponibles en el MPSoC.

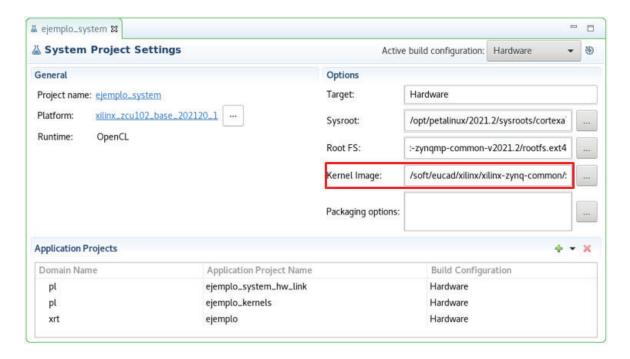

Desde la perspectiva de la metodología de desarrollo, la programación de la aplicación se realiza en C/C++. Por otra parte, el diseño de los *kernels* se realiza desde una

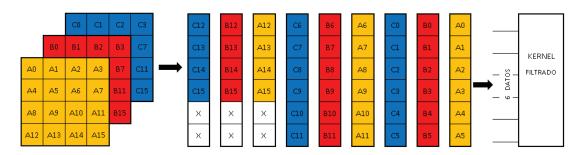

i

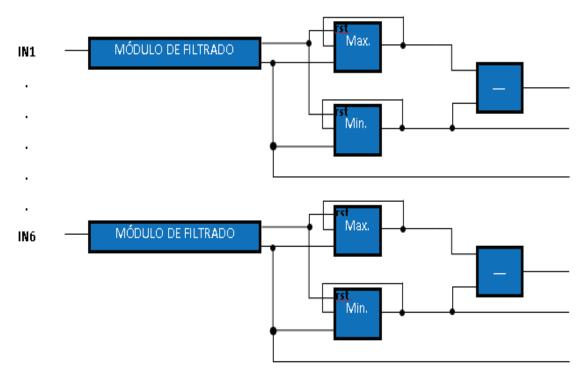

descripción algorítmica mediante la utilización de técnicas de síntesis de alto nivel (HLS). En esta metodología, el diseño de los *kernels* parte de una descripción funcional, sin información temporal (*untimed*) desarrollada en C/C++ combinada con un conjunto de directivas de síntesis que permiten especificar la arquitectura *hardware* del *kernel*. La interacción entre el *host* y los *kernels* se programa usando OpenCL (*Open Computing Language*). Tanto los *kernels* como el *host* se desarrollan utilizando la aplicación Vitis 2021.2 de Xilinx.

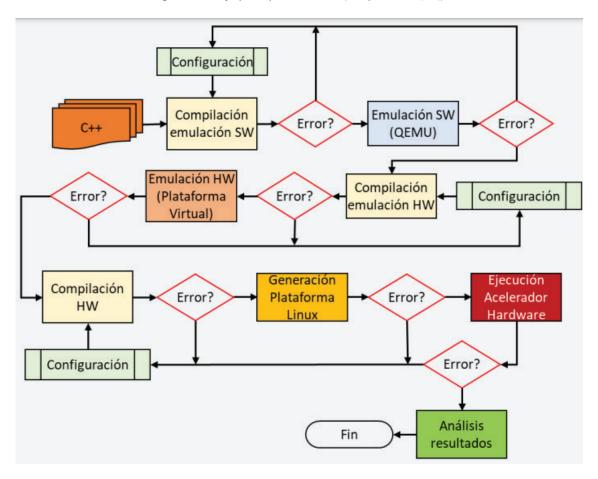

Siguiendo la metodología HLS, la verificación de la aplicación se realiza mediante técnicas de emulación *software* y, posteriormente, mediante emulación *hardware*. La emulación *software* permite la verificación funcional del algoritmo descrito para los *kernels*. Se realiza en C/C++, compilando ya sea sobre un *host* Linux x86 o mediante la utilización de QEMU. La emulación *hardware* posibilita verificar la implementación *hardware* de los *kernels* y obtener información sobre las prestaciones de esta.

Por último, se realiza el diseño final para su prototipado. Tanto el *bitstream* como los componentes *software* (sistema operativo + aplicación) se cargan desde una tarjeta SD (*Secure Digital*) en el MPSoC para su ejecución sobre el hardware real.

Tras desarrollar este trabajo, se obtiene una aplicación capaz de clasificar distintas regiones en imágenes hiperespectrales de pacientes afectados de cáncer de piel. Esta aplicación efectúa el preprocesado de la imagen y el posterior *clustering* de los píxeles, mediante aceleración *hardware* en FPGA. Esta aceleración ha supuesto una mejora significativa de la velocidad de cómputo y del consumo energético de la aplicación.

Por otra parte, a esta aplicación se la ha dotado de parámetros de configuración estáticos, además de cierta versatilidad para reconfigurar los *kernels* FPGA. Esta aplicación puede operar con imágenes hiperespectrales de diferentes dimensiones y formatos. Asimismo, la aplicación posee algunas opciones de configuración que facilitan su adaptabilidad a otras circunstancias de funcionamiento, incluyendo la implementación en otros dispositivos. Adicionalmente, se ha desarrollado un configurador que asiste al usuario en el ajuste de los *kernels* para aprovechar óptimamente la FPGA.

#### **Abstract**

This Master's Thesis (TFM) studies the use of hardware accelerators based on MPSoC (Multiprocessor System on Chip) FPGAs (Field-programmable Gate Array) applied for processing hyperspectral images for medical purposes, more specifically for diagnosing possible cases of skin cancer. In order to make hyperspectral images useful, their content must be pre-processed. This minimizes the influence of factors unrelated to the nature of the image on the information. After preprocessing, it is desirable to use the resulting hyperspectral images to extract accurate, automated and useful conclusions for the use case. To do so, utilizing machine learning algorithms is highly suitable. In this work, the "kmeans" algorithm is considered, using it to determine regions in the skin captured in the image depending on whether it is healthy or affected tissue.

Pre-processing hyperspectral images and the k-means algorithm involve a high computational load in a sequential execution. For this reason, it is highly desirable to implement hardware acceleration that exploits the parallelization possibilities of these algorithms, thereby reducing their runtime and energy consumption.

To achieve this acceleration, MPSoC FPGAs are used on a Xilinx Zynq UltraScale+MPSoC ZCU102 prototyping board, which embodies an MPSoC as central element containing, among other resources, a multiprocessing system and an FPGA with programmable logic (PL, Programmable Logic). The hardware/software application to implement consists of a software application (app.) running as host and hardware acceleration functions or kernels running on the FPGA. The host runs on the APU (Application Processor Unit) based on an ARM Cortex A53 multiprocessing system. The kernels run on the FPGA. For communicating data and control between the APU and the FPGA, an on-chip bus system based on configurable high-bandwidth AMBA AXI4 interfaces available on the MPSoC is used

From the point of view of the development methodology, the programming of the application is carried out in C/C++. On the other hand, the design of the hardware kernels is based on an algorithmic description using high-level synthesis techniques (HLS). In this methodology, the design of the kernels starts from a functional description, without

temporal information (untimed) developed in C/C++ combined with a set of synthesis directives that allow specifying the hardware architecture of the kernel. The interaction between host and kernels is programmed using OpenCL (Open Computing Language). Both kernel and host are done using the Xilinx Vitis 2021.2 application.

Following the HLS methodology, the verification of the application is carried out by using software emulation techniques and, subsequently, hardware emulation. Software emulation provides a functional verification of the algorithm described for the kernels is carried out. This is done in C/C++, compiling either on a Linux x86 host or using QEMU. Hardware emulation allows to verify the hardware implementation of the kernels and to obtain information about its performance. Finally, the final design is prototyped. Both the bitstream and the software components (operating system + application) are loaded from an SD (Secure Digital) card into the MPSoC for execution on the real hardware.

After developing this work, an application capable of classifying different regions in hyperspectral images of patients affected by skin cancer is obtained. This application performs image pre-processing and subsequent pixel clustering by using hardware acceleration via FPGA. This acceleration has led to a significant improvement in the computational speed and energy consumption of the application.

On the other hand, this application has been provided with static configuration parameters, as well as a certain versatility for reconfiguring the FPGA kernels. This application can operate with hyperspectral images of different dimensions and formats. It also has some configuration options to facilitate the adaptability of the application to other operating circumstances, including its implementation in other devices. In addition, a configurator has been developed to assist user when adjusting kernels for optimal use of the FPGA.

## Tabla de contenidos

| Capítulo 1. | Introducción                                   | 1  |

|-------------|------------------------------------------------|----|

| 1.1.        | Introducción                                   | 1  |

| 1.2.        | Objetivos                                      | 5  |

| 1.3.        | Estructura del documento                       | 6  |

| Capítulo 2. | Machine learning                               | 9  |

| 2.1.        | Introducción                                   | 9  |

| 2.2.        | Información de entrenamiento                   | 10 |

| 2.3.        | Clasificadores lineales y polinómicos          | 12 |

| 2.3.1.      | Support Vector Machine (SVM)                   | 13 |

| 2.3.2.      | Clasificadores binarios múltiples              | 16 |

| 2.4.        | Clustering                                     | 17 |

| 2.5.        | Conclusiones                                   | 22 |

| Capítulo 3. | Imágenes hiperespectrales                      | 23 |

| 3.1.        | Introducción                                   | 23 |

| 3.2.        | Factores a considerar para el preprocesamiento | 25 |

| 3.3.        | Organización de los datos                      | 28 |

| 3.4.        | Identificación de muestras                     | 31 |

| 3.5.        | Conclusiones                                   | 33 |

| Capítulo 4. | Sistema de referencia                          | 35 |

| 4.1.        | Introducción                                   | 35 |

| 4.2.        | Cadena de preprocesado                         | 35 |

| 4.3.        | Segmentación automática (o clustering)         | 36 |

| 4.4.        | Conclusiones                                   | 37 |

| Capítulo 5. | Zynq Ultrascale+ MPSoC                         | 39 |

| 5.1.        | Introducción                                   | 39 |

| 5.2.        | Sistema de procesamiento                       | 42 |

| 5.2.1.      | APU basada en ARM Cortex-A53                   | 43 |

| 5.2.2.      | Memoria PS                                     | 45 |

| 5.3.        | Lógica programable (PL)                        | 46 |

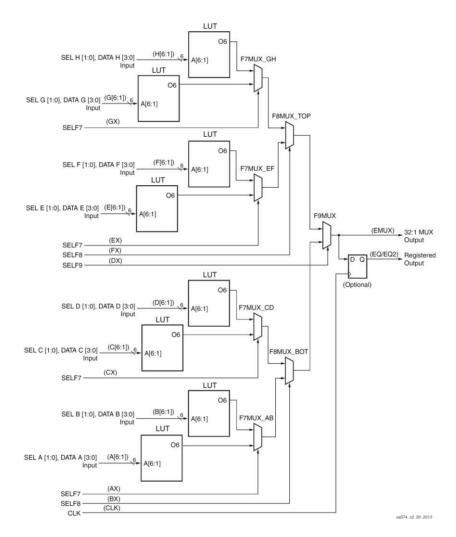

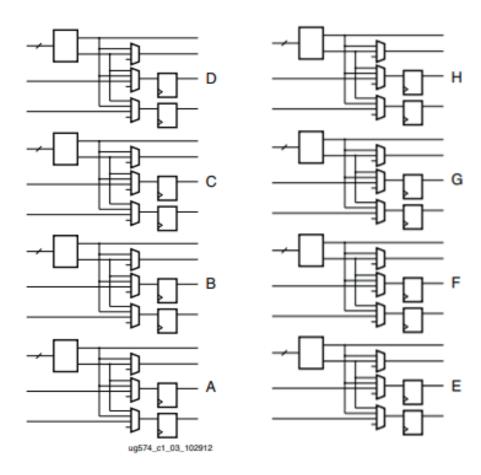

| 5.3.1.      | CLRs                                           | 46 |

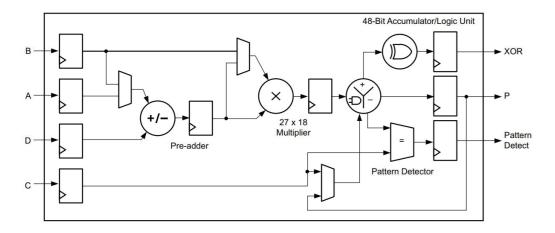

| 5.3.2.      | Bloques DSP48E2                         | 48 |

|-------------|-----------------------------------------|----|

| 5.3.3.      | Memorias RAM                            | 49 |

| 5.4.        | Comunicación PS – PL                    | 50 |

| 5.4.1.      | Interfaz AXI                            | 51 |

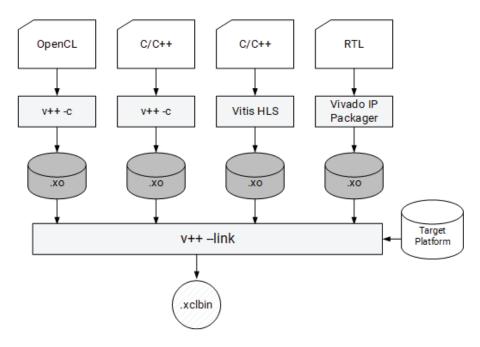

| 5.4.2.      | Transferencias PS-PL                    | 53 |

| 5.5.        | Conclusiones                            | 55 |

| Capítulo 6. | OpenCL para C++                         | 57 |

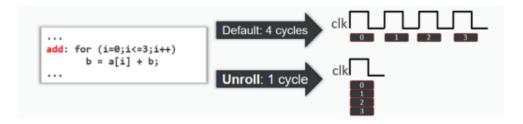

| 6.1.        | Introducción                            | 57 |

| 6.1.1.      | Modelo de ejecución                     | 59 |

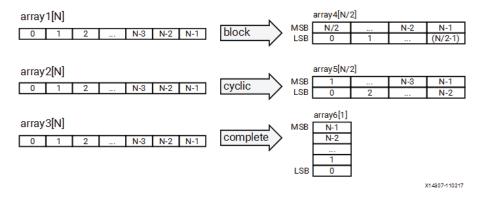

| 6.1.2.      | Xilinx Runtime (XRT)                    | 62 |

| 6.2.        | cl::Platform                            | 64 |

| 6.2.1.      | Función get                             | 64 |

| 6.2.2.      | Función getInfo                         | 64 |

| 6.2.3.      | Función getDevices                      | 66 |

| 6.3.        | cl::Device                              | 66 |

| 6.4.        | cl::Context                             | 67 |

| 6.5.        | cl::CommandQueue                        | 67 |

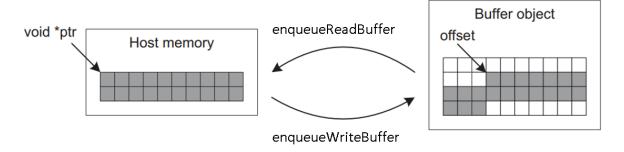

| 6.5.1.      | Función enqueueWriteBuffer              | 69 |

| 6.5.2.      | Función enqueueTask                     | 70 |

| 6.5.3.      | Función enqueueReadBuffer               | 71 |

| 6.5.4.      | Función finish.                         | 72 |

| 6.6.        | cl::Program                             | 73 |

| 6.7.        | cl::Kernel                              | 75 |

| 6.8.        | cl::Buffer                              | 76 |

| 6.9.        | cl::Event                               | 78 |

| 6.9.1.      | Establecimiento de una función callback | 79 |

| 6.9.2.      | Sincronización                          | 80 |

| 6.9.3.      | Medición de tiempo                      | 81 |

| 6.10.       | Conclusiones                            | 83 |

| Capítulo 7. | Metodología de diseño en Vitis          | 85 |

| 7.1.        | Introducción                            | 85 |

| 7.2.        | Flujo de diseño                         | 86 |

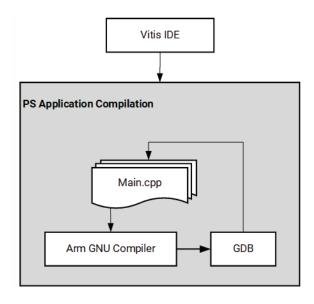

| 7.3.        | Diseño del <i>host</i>                  | 92 |

| 7.4.        | Diseño del kernel                                                                | 93    |

|-------------|----------------------------------------------------------------------------------|-------|

| 7.4.1.      | Flujo de diseño                                                                  | 94    |

| 7.4.2.      | Directivas de optimización                                                       | 95    |

| 7.5.        | Generación de ficheros de la plataforma del sistema                              | 108   |

| 7.6.        | Conclusiones                                                                     | 110   |

| Capítulo 8. | Aplicación desarrollada                                                          | 113   |

| 8.1.        | Introducción                                                                     | 113   |

| 8.2.        | Opciones de configuración                                                        | . 113 |

| 8.3.        | Funciones macro para la creación de variables de precisión arbitraria            | 124   |

| 8.4.        | Conversión de datos entre el <i>host</i> y el <i>kernel</i>                      | . 127 |

| 8.5.        | Kernels FPGA                                                                     | . 128 |

| 8.5.1.      | Inicialización de los kernels desde el host y configuración de las comunicacione |       |

| host-k      | ernel                                                                            |       |

| 8.5.2.      | Interfaces de entrada/salida                                                     | 132   |

| 8.5.3.      | Implementación de la configuración estática                                      | 136   |

| 8.5.4.      | Particionado de los <i>arrays</i>                                                | 138   |

| 8.5.5.      | Medición de los tiempos de ejecución y transferencia                             | 138   |

| 8.6.        | Etapa de preprocesamiento                                                        | 140   |

| 8.7.        | Etapa k-means                                                                    | 159   |

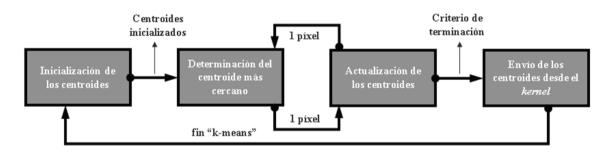

| 8.7.1.      | Inicialización de los centroides                                                 | 162   |

| 8.7.2.      | Determinación del centroide más cercano                                          | 163   |

| 8.7.3.      | Actualización de los centroides                                                  | . 168 |

| 8.7.4.      | Envío de los centroides desde el kernel                                          | 174   |

| 8.7.5.      | Interfaces de entrada/salida                                                     | 175   |

| 8.8.        | Etapa SAM                                                                        | . 177 |

| 8.9.        | Diagrama de bloques de la aplicación                                             | 180   |

| 8.10.       | Configuración de los kernels mediante hoja de cálculo                            | 184   |

| 8.11.       | Prototipado de la aplicación                                                     | 197   |

| 8.12.       | Conclusiones                                                                     | 201   |

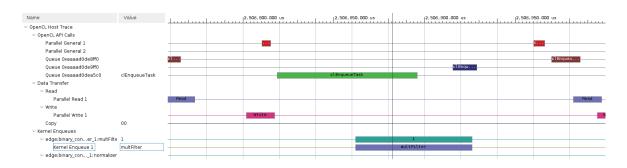

| Capítulo 9. | Resultados de la implementación                                                  | . 203 |

| 9.1.        | Introducción                                                                     | 203   |

| 9.2.        | Validación funcional                                                             | . 204 |

| 9.3.        | Utilización de recursos                                                          | . 214 |

| 9.4.        | Prestaciones temporales de los kernels                                           | . 222 |

|    | 9.5.       | Consumo de potencia             | 227 |

|----|------------|---------------------------------|-----|

|    | 9.6.       | Conclusiones                    | 229 |

| Ca | pítulo 10. | Conclusiones y trabajos futuros | 231 |

|    | 10.1.      | Conclusiones                    | 231 |

|    | 10.2.      | Trabajos futuros                | 234 |

# Índice de figuras

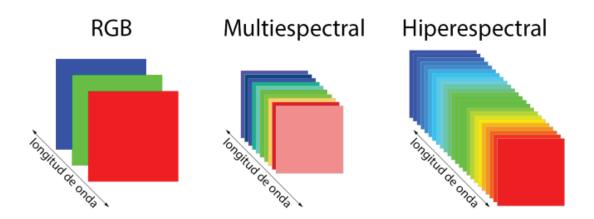

| Figura 1: Comparativa imágenes RGB, multiespectrales e hiperespectrales [5]                   | 2        |

|-----------------------------------------------------------------------------------------------|----------|

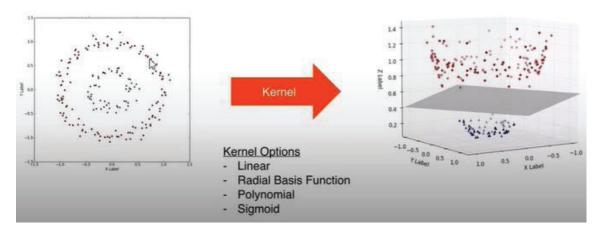

| Figura 2: Aplicación de kernel radial para separar clases linealmente [16]                    | 15       |

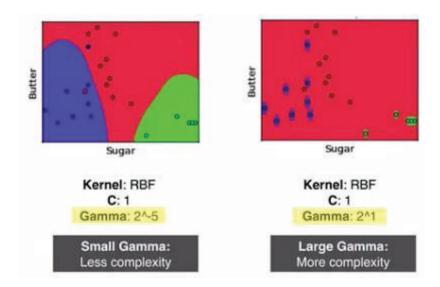

| Figura 3: Caso de " $\gamma$ " reducida (parte izquierda) y elevada (parte derecha) [17]      | 16       |

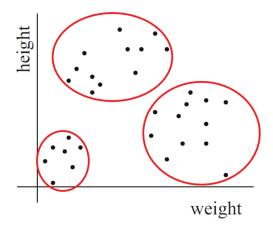

| Figura 4: Ejemplo de detección de clústeres [10]                                              | 18       |

| Figura 5: Distribución de muestras en un espacio bidimensional [10]                           | 19       |

| Figura 6: Ejemplo de distribución de muestras donde "k-means" no sería eficaz [10]            | 21       |

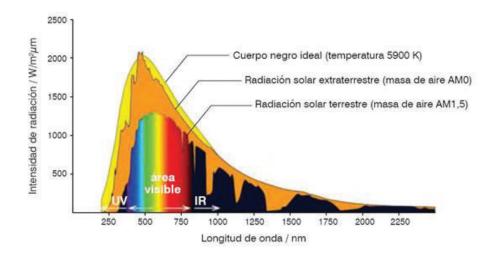

| Figura 7. Composición espectral de la radiación solar en la tierra [7], [20]                  | 25       |

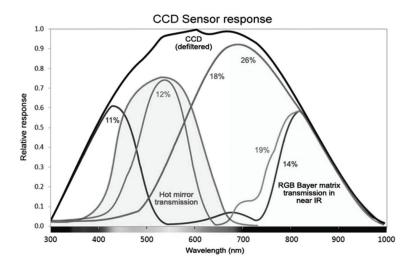

| Figura 8. Sensibilidad del sensor CCD estándar a la luz según la longitud de onda [21]        | 26       |

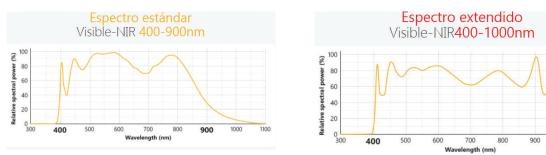

| Figura 9. Espectro de la lámpara Effilux: (a) espectro estándar, (b) espectro extendido [22]  | 27       |

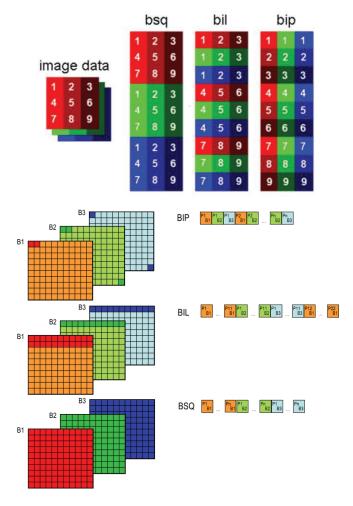

| Figura 10. Formatos básicos de ordenación de los datos de una imagen hiperespectral [25]      | 30       |

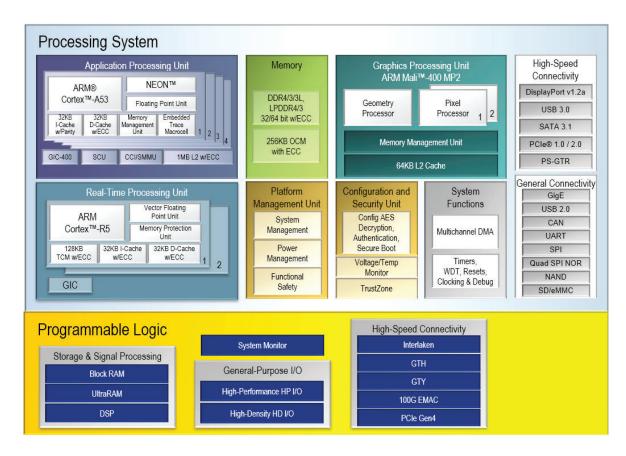

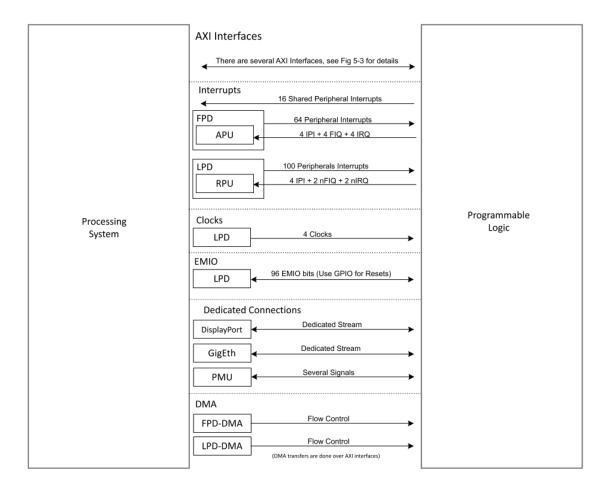

| Figura 11: Módulos hardware del MPSoC a utilizar [31]                                         | 41       |

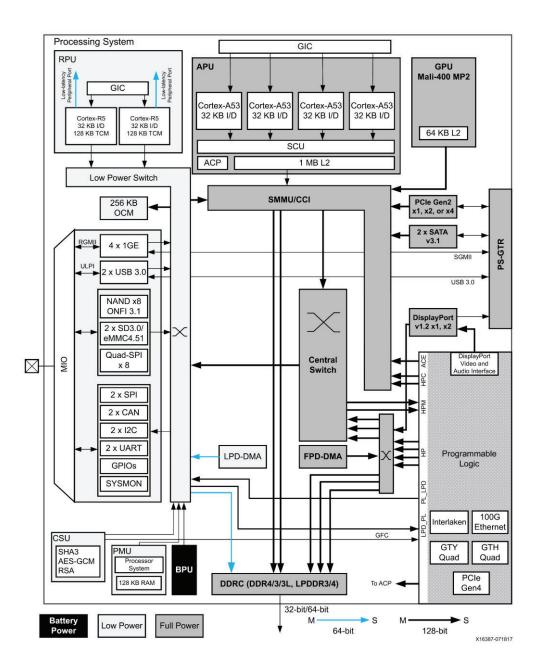

| Figura 12: Diagrama de bloques de la arquitectura Zynq UltraScale+ MPSoC [32]                 | 42       |

| Figura 13: Diagrama de bloques de la APU [34]                                                 | 43       |

| Figura 14: Conexionado entre las LUTs y los multiplexores dentro de un CLB [39]               | 47       |

| Figura 15. LUTs y elementos de almacenamiento de un Slice [39]                                | 48       |

| Figura 16: Esquemático del DSP48E2 [27], [40]                                                 | 49       |

| Figura 17: Conexiones entre PS y PL [33]                                                      | 51       |

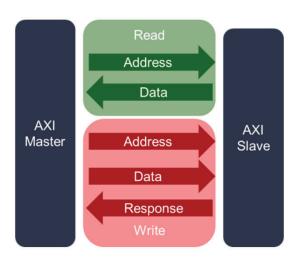

| Figura 18: Canales de una interfaz AXI estándar [41]                                          |          |

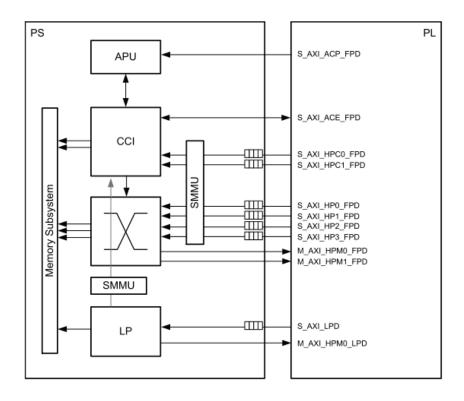

| Figura 19: Conexiones AXI PS – PL [33]                                                        | 53       |

| Figura 20. Modelo de desarrollo con OpenCL [45]                                               | 58       |

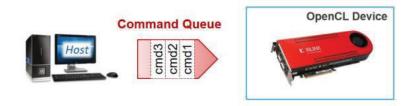

| Figura 21. Ejemplo de colas de comandos [45]                                                  | 58       |

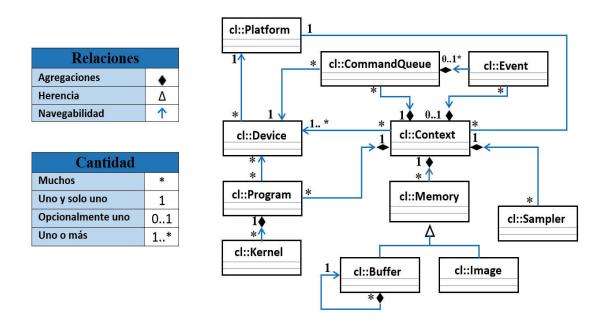

| Figura 22: Relaciones entre clases de OpenCL para C++ (adaptado de [44])                      | 59       |

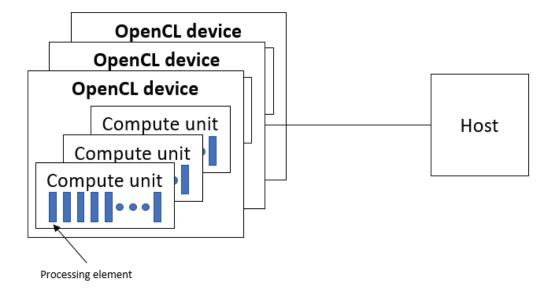

| Figura 23: Arquitectura de un sistema heterogéneo adaptado al estándar OpenCL [44]            | 60       |

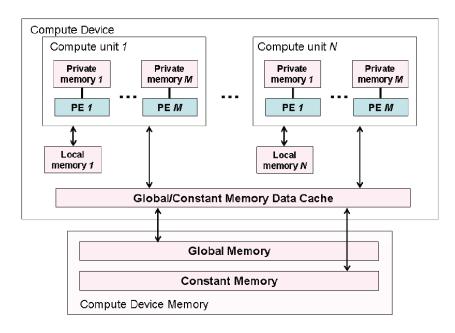

| Figura 24. Arquitectura del modelo de memoria (adaptado de [45])                              | 62       |

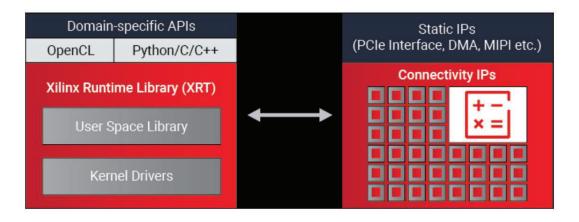

| Figura 25. Comunicación utilizando XRT [46]                                                   | 63       |

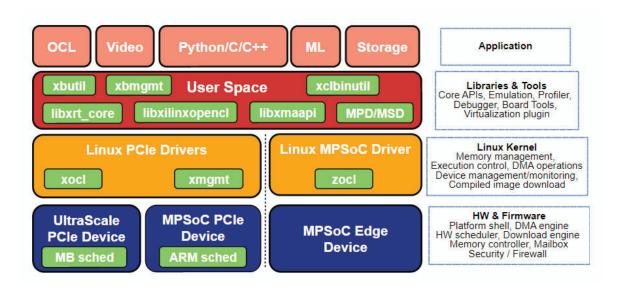

| Figura 26. Xilinx Runtime (XRT) Stack [47]                                                    | 63       |

| Figura 27: Transferencias mediante enqueueReadBuffer y enqueueWriteBuffer [42]                | 73       |

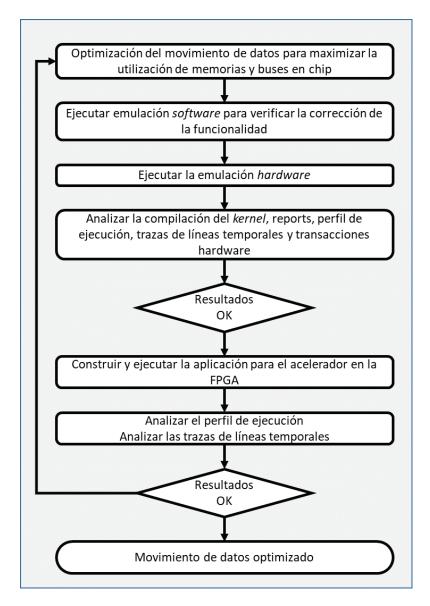

| Figura 28. Flujo principal de diseño (adaptado de [45])                                       | 87       |

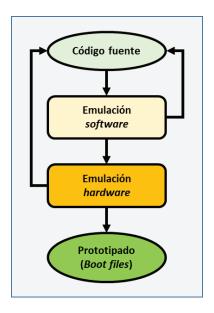

| Figura 29: Metodología de diseño de la aplicación [14]                                        | 87       |

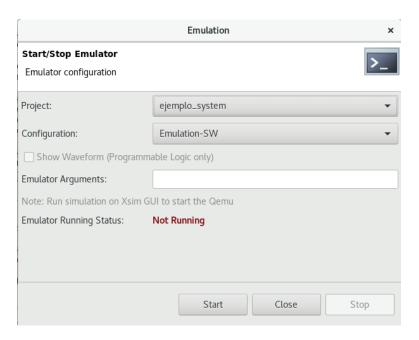

| Figura 30: Arranque del emulador QEMU                                                         | 89       |

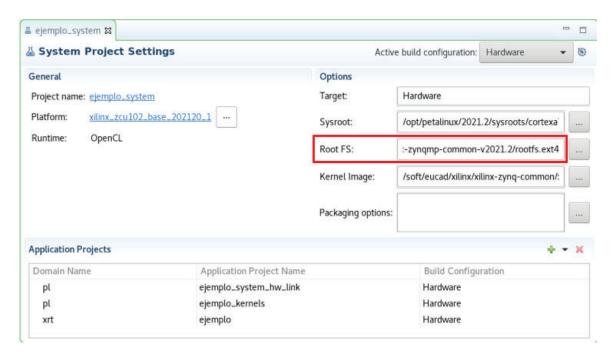

| Figura 31: Especificación del Root FS                                                         | 90       |

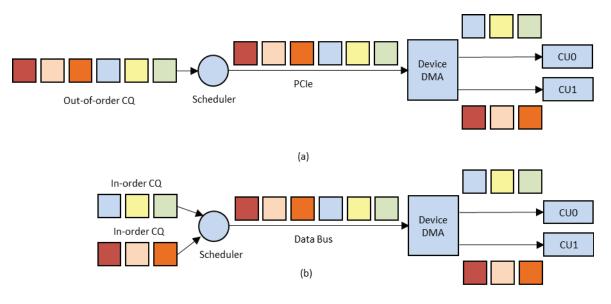

| Figura 32. Planificación de las colas de procesamiento. (a) Planificación fuera de orden de u | una cola |

| de comandos vs. (b) planificación en orden en varias colas de comandos [45]                   | 91       |

| Figura 33. Proceso de optimización en el host [45]                                            | 92       |

| Figura 34: Diseño y depuración de la codificación del host [56]                               | 93       |

| Figura 35: Generación de archivos binarios de la FPGA [52]                                    | 94       |

| Figura 36: Efecto del parámetro "bundle" en los puertos de entrada salida del kernel          | 96       |

| Figura 37. Ejemplo de utilización de HLS unroll [45]                                          | 97       |

| Figura 38. Tipos de partición de los bloques de memoria [57]                                  | 101      |

| Figura 39: Ejecución sin pipelining (opción A) y con pipelining (opción B) [57], [60]         | 102      |

| Figura 40. Ejemplo de ficheros producidos por Vitis                                           | 109      |

| Figura 41: Especificación del kernel de Linux                                             | 110 |

|-------------------------------------------------------------------------------------------|-----|

| Figura 42: Ordenamiento de datos de la imagen hiperespectral para transferirlos al kernel | de  |

| filtrado                                                                                  | 140 |

| Figura 43: Esquema básico del kernel de filtrado                                          | 145 |

| Figura 44: Modos de funcionamiento del kernel "top_kmeans" y transiciones entre ellos     | 161 |

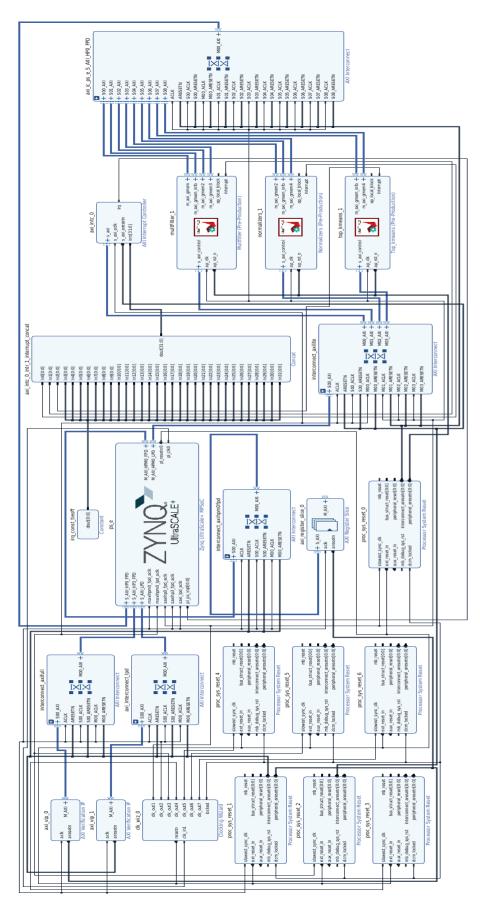

| Figura 45: Diagrama de bloques de la aplicación                                           | 181 |

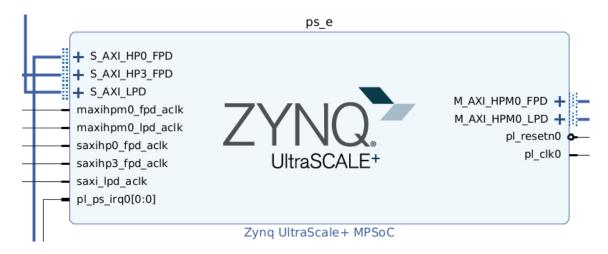

| Figura 46: Bloque PS del diagrama de bloques                                              | 182 |

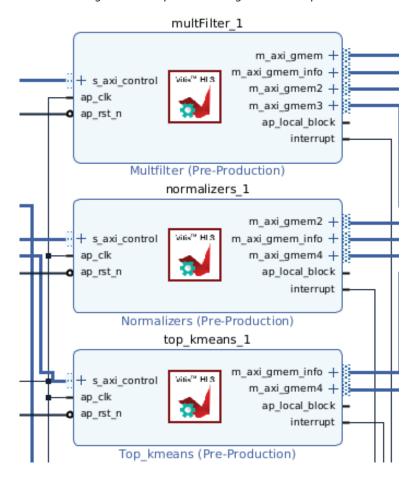

| Figura 47: Kernels FPGA en el diagrama de bloques                                         | 182 |

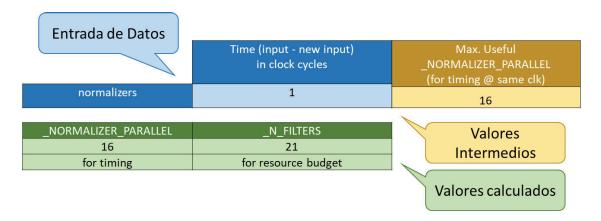

| Figura 48. Vista parcial de la hoja de cálculo de configuración de los kernels            | 185 |

| Figura 49: Sistema de colores de la hoja de cálculo                                       | 186 |

| Figura 50: Parámetros temporales comunes y del throughput del kernel "multFilter"         | 187 |

| Figura 51: Parámetro "Time (input – new input)" del kernel "multFilter"                   | 187 |

| Figura 52: Sección sobre los módulos funcionales del kernel "multFilter"                  | 189 |

| Figura 53: Sección sobre los módulos funcionales del kernel "normalizers"                 | 190 |

| Figura 54: Sección sobre los módulos funcionales del kernel "top_kmeans"                  | 193 |

| Figura 55: "Budget" y máximo paralelismo implementable del kernel "normalizers"           | 195 |

| Figura 56: Paralelización resultante del kernel "multFilter"                              | 195 |

| Figura 57: Parámetros de configuración estática en las estimaciones de "top_kmeans"       | 196 |

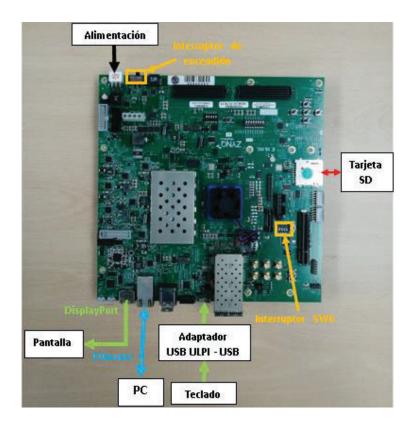

| Figura 58. Configuración del modo de arranque mediante tarjeta SD                         | 199 |

| Figura 59: Indicación del fin del arranque de la placa de prototipado                     | 199 |

| Figura 60: Establecimiento del soporte OTG para la introducción de teclado [14]           | 200 |

| Figura 61: Diagrama de conexionado con la ZCU102                                          | 201 |

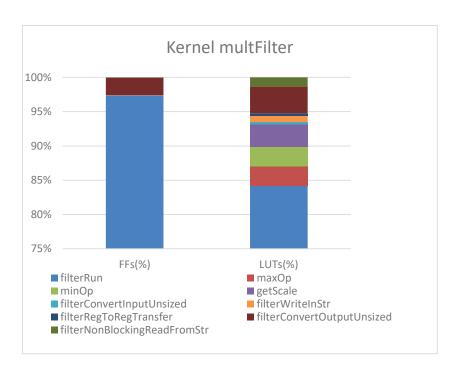

| Figura 62: Utilización relativa de LUTs y FFs de los módulos funcionales de "multFilter"  | 215 |

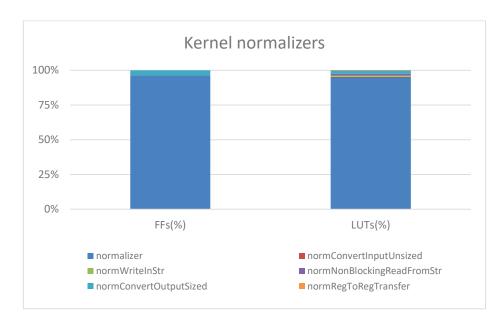

| Figura 63: Utilización relativa de LUTs y FFs de los módulos funcionales de "normalizers" | 216 |

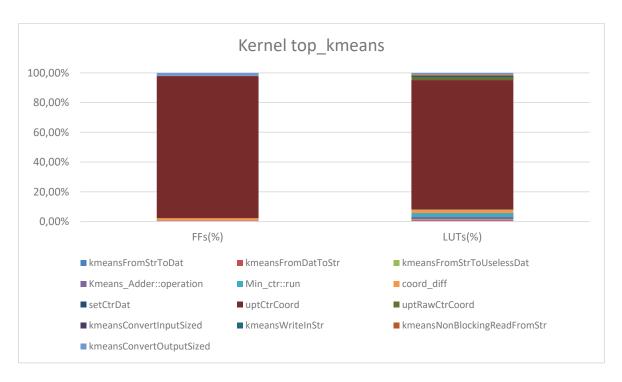

| Figura 64: Utilización relativa de LUTs y FFs de los módulos funcionales de "top_kmeans"  | 217 |

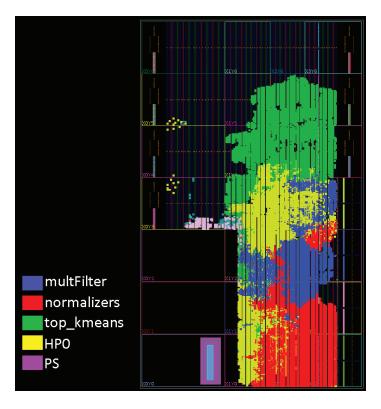

| Figura 65: Distribución de la utilización de recursos                                     | 221 |

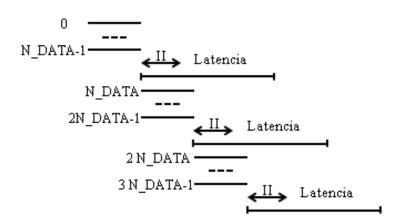

| Figura 66: Capacidades de paralelismo de los kernels FPGA                                 | 223 |

| Figura 67: Impacto de la operación "readreq"                                              | 225 |

| Figura 68: Impacto de la operación "writeresp"                                            | 225 |

| Figura 69: Impacto de la operación "udiv"                                                 | 225 |

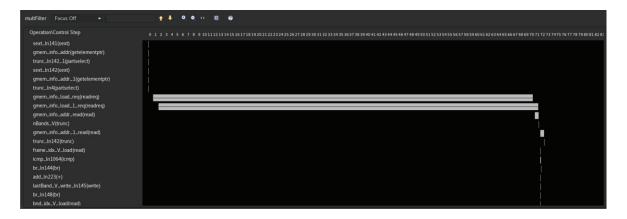

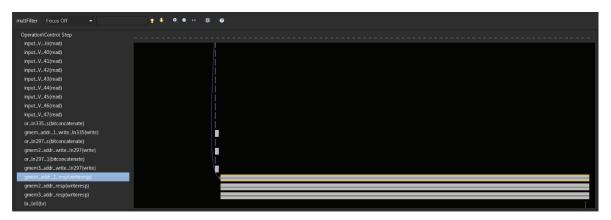

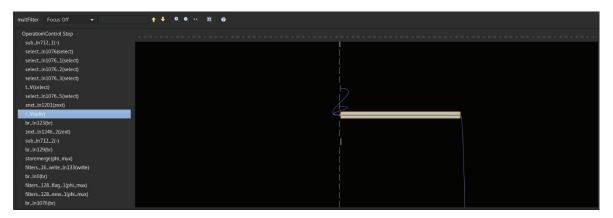

| Figura 70: Timeline del kernel "multFilter"                                               | 226 |

| Figura 71: Timeline del kernel "normalizers"                                              | 226 |

| Figura 72: Timeline del kernel "top_kmeans" en etapa sin generación de salida             | 226 |

| Figura 73: : Timeline del kernel "top_kmeans" en etapa con generación de salida           | 227 |

| Figura 74: Informe sobre el consumo de potencia de la aplicación                          | 227 |

## Índice de Tablas

| Tabla 1: Componentes hardware en función de la subfamilia (adaptada de [28])               | 40  |

|--------------------------------------------------------------------------------------------|-----|

| Tabla 2: Cantidad de recursos de la parte PL [32], [38]                                    | 46  |

| Tabla 3: Macros que identifican diferentes datos de las plataformas [42]                   | 65  |

| Tabla 4: Macros que identifican especificaciones acerca de los dispositivos a buscar [42]  | 66  |

| Tabla 5: Macros que identifican diferentes opciones de configuración de cl::Buffer [42]    | 77  |

| Tabla 6: Macros que identifican instantes de tiempo de los comandos OpenCL [42]            | 82  |

| Tabla 7: Macros que identifican la información a extraer relativa al evento cl::Event [42] | 83  |

| Tabla 8: Especificación de las particiones (adaptado de [72])                              | 198 |

| Tabla 9: Configuración estática de la aplicación                                           | 203 |

| Tabla 10: Características de las imágenes hiperespectrales para el trabajo                 | 203 |

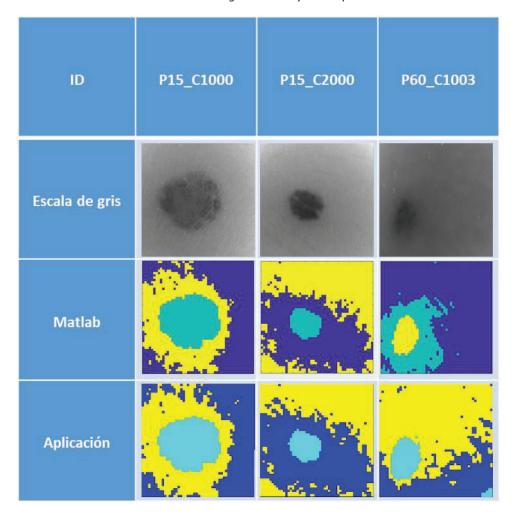

| Tabla 11: Clustering en Matlab y de la aplicación                                          | 208 |

| Tabla 12: Tiempos de ejecución del algoritmo                                               | 212 |

| Tabla 13: Utilización de recursos de los módulos funcionales del kernel "multFilter"       | 214 |

| Tabla 14: Utilización de recursos de los módulos funcionales del kernel "normalizers"      | 216 |

| Tabla 15: Utilización de recursos de los módulos funcionales del kernel "top_kmeans"       | 217 |

| Tabla 16: Utilización de recursos de los kernels FPGA                                      | 218 |

| Tabla 17: Utilización de recursos dentro del bitstream                                     | 222 |

| Tabla 18: Prestaciones temporales de los kernels FPGA                                      | 223 |

## **Índice de Ecuaciones**

| Ecuación (1). Ecuación lineal a ajustar en los clasificadores lineales                 | 12    |

|----------------------------------------------------------------------------------------|-------|

| Ecuación (2). Ecuación de determinación en SVM de los vectores de soporte              | 13    |

| Ecuación (3). Ecuación para la clasificación de las muestras en SVM                    | 14    |

| Ecuación (4). <i>Kernel</i> radial en SVM                                              | 15    |

| Ecuación (5). Spectral Angle Mapper                                                    | 31    |

| Ecuación (6). Spectral Angle Mapper en la aplicación                                   | . 177 |

| Ecuación (7). Simplificación de <i>Spectral Angle Mapper</i> para esta aplicación (I)  | . 178 |

| Ecuación (8). Simplificación de <i>Spectral Angle Mapper</i> para esta aplicación (II) | . 178 |

# Índice de códigos

| Codigo 1: Otilización de la función ci::Platform::get                                     | 64  |

|-------------------------------------------------------------------------------------------|-----|

| Código 2: Utilización de la función cl::Platform::getInfo                                 | 65  |

| Código 3: Utilización de la función cl::Platform::getDevices                              | 66  |

| Código 4: Creación del objeto cl::Context                                                 | 67  |

| Código 5: Creación de los objetos cl::CommandQueue                                        | 68  |

| Código 6: Utilización de la función cl::CommandQueue::enqueueWriteBuffer                  | 70  |

| Código 7: Utilización de la función cl::CommandQueue::enqueueTask                         | 71  |

| Código 8: Utilización de la función cl::CommandQueue::enqueueReadBuffer                   | 72  |

| Código 9: Utilización de la función cl::CommandQueue::finish                              | 72  |

| Código 10: Función setBinary                                                              | 74  |

| Código 11: Creación del objeto cl::Program                                                | 75  |

| Código 12: Creación de objeto cl::Kernel                                                  | 75  |

| Código 13: Utilización de la función cl::Kernel::setArg                                   | 76  |

| Código 14: Cabecera de la función principal del kernel "multFilter"                       | 76  |

| Código 15: Creación de objetos cl::Buffer                                                 | 78  |

| Código 16: Creación e introducción en vector de objeto cl::Event                          | 79  |

| Código 17: Utilización de la función cl::Event::setCallback                               | 79  |

| Código 18: Formato de cabecera de las funciones callback de OpenCL [42]                   | 80  |

| Código 19: Sincronización mediante eventos de comandos de OpenCL                          | 81  |

| Código 20: Utilización de la función clGetEventProfilingInfo                              | 83  |

| Código 21: Invocación de conexión del agente TCF [53]                                     | 90  |

| Código 22: Transferencia de archivos desde el PC hacia el QEMU [53]                       | 91  |

| Código 23: Transferencia de archivos desde QEMU hacia el PC [53]                          | 91  |

| Código 24: Utilización del parámetro "bundle" de la directiva "#pragma HLS interface"     | 96  |

| Código 25: Sintaxis de la directiva "#pragma HLS unroll" [57], [60]                       | 98  |

| Código 26: Sintaxis de la directiva "#pragma HLS array_partition" [57]                    | 100 |

| Código 27: Función de la descripción HLS con inlining                                     | 105 |

| Código 28: Función de la descripción HLS con inlining anulado                             | 105 |

| Código 29: Sintaxis de la directiva "#pragma HLS function_instantiate" [57], [60]         | 106 |

| Código 30: Ejemplo de la directiva "#pragma HLS function_instantiate" [57], [60]          | 106 |

| Código 31: Sintaxis de la directiva "#pragma HLS dependence" [57], [60]                   | 107 |

| Código 32: Función "getSpecifications"                                                    | 115 |

| Código 33: Contenido de ejemplo de un archivo de cabecera                                 | 115 |

| Código 34: Función "getHDRSpecifications"                                                 | 117 |

| Código 35: Función "getspecifiedFormat"                                                   | 118 |

| Código 36: Declaración de nombres identificativos de los criterios de ordenación          | 119 |

| Código 37: Especificación de las dimensiones por defecto de las imágenes hiperespectrales | 120 |

| Código 38: Bandas espectrales extremas residuales de las imágenes hiperespectrales        | 121 |

| Código 39: Declaración del tipo de variable "unsized_d"                                   | 124 |

| Código 40: Declaración del atributo "Value" de la clase "UnsignedBitWidth"                | 125 |

| Código 41: Función macro "_AP_UINT_FOR_MAX_VAL"                                           | 126 |

| Código 42: Utilización de función macro "_SUM_AP_UFIXED"                                  | 127 |

|                                                                                           |     |

| Código 43: Declaración de la función macro "_MULT_NORM_AP_UFIXED"                            | 127 |

|----------------------------------------------------------------------------------------------|-----|

| Código 44: Subtipos de variables para la conversión de datos "unsized_d"                     | 128 |

| Código 45: Función "init"                                                                    | 129 |

| Código 46: Función de inicialización de la etapa de filtrado                                 | 131 |

| Código 47: Función HLS para introducir los datos a filtrar en el kernel de filtrado          | 133 |

| Código 48: Funcion HLS para preparar los datos filtrados para su envío al host               | 133 |

| Código 49: Configuración del tamaño de los arrays de transferencia entre el host y el kernel | 135 |

| Código 50: Configuración del burst para una interfaz "m_axi"                                 | 136 |

| Código 51: Constante HLS de precisión arbitraria para la macro "_TRANFER_N_DATA"             | 137 |

| Código 52: Generación de la constante de C para la macro "_FILTER_II"                        | 138 |

| Código 53: Ejemplo de función callback asignada a evento de OpenCL cl::Event                 | 139 |

| Código 54: Función "transfer"                                                                | 142 |

| Código 55: Función "transfer_BSQ_Preproc"                                                    | 143 |

| Código 56: Función "filter"                                                                  | 145 |

| Código 57: Constructor de la clase "Filter"                                                  | 146 |

| Código 58: Función "filterRun"                                                               | 147 |

| Código 59: Función "shift_concurrente"                                                       | 147 |

| Código 60: Función "filterToStr"                                                             | 149 |

| Código 61: Función "filterFromStr"                                                           | 150 |

| Código 62: Función "loadToOutput"                                                            | 151 |

| Código 63: Función "coreFilterExchange"                                                      | 152 |

| Código 64: Función "lastBandsFromPx"                                                         | 153 |

| Código 65: Función "normalizer"                                                              | 154 |

| Código 66: Función "normToStr"                                                               | 155 |

| Código 67: Función "loadToReg"                                                               | 156 |

| Código 68: Función "normFromStr"                                                             | 156 |

| Código 69: Función "ToNormalizers"                                                           | 157 |

| Código 70: Función "sendMinAndScales"                                                        | 158 |

| Código 71: Función "exeNorm"                                                                 | 158 |

| Código 72: Kernel "top_kmeans"                                                               | 160 |

| Código 73: Función "initCentroids"                                                           | 163 |

| Código 74: Función "assessDistance"                                                          | 164 |

| Código 75: Función "coorddiff"                                                               | 164 |

| Código 76: Función "Kmeans_Adder::run"                                                       | 166 |

| Código 77: Función Min_ctr::run                                                              | 167 |

| Código 78: Función "uptCtrs"                                                                 | 169 |

| Código 79: Función "kmeansFromStrToDat"                                                      | 170 |

| Código 80: Función "uptRawCtrCoord"                                                          | 170 |

| Código 81: Función "uptCtrCoord"                                                             | 171 |

| Código 82: Evaluación del criterio de terminación de k-means                                 | 173 |

| Código 83: Declaración de "_REL_MIN_PX_CHANGES"                                              | 173 |

| Código 84: Declaración de "_MAX_ITER"                                                        | 173 |

| Código 85: Función "sendCentroids"                                                           | 174 |

| Código 86: Función "kmeansToStr"                                                             | 175 |

| Código 87: Función "kmeansFromStr"                                                    | 176 |

|---------------------------------------------------------------------------------------|-----|

| Código 88: Función coreSAM                                                            | 179 |

| Código 89: Función "getVectorDotProduct"                                              | 179 |

| Código 90: Función "AdderReg" para la hoja de cálculo                                 | 197 |

| Código 91: Comando "fdisk" [72]                                                       | 197 |

| Código 92: Especificación del formato de cada partición [72]                          | 198 |

| Código 93: Introducción de la aplicación en la tarjeta SD                             | 198 |

| Código 94: Establecimiento de conexión SSH entre el PC y la placa de prototipado      | 200 |

| Código 95: Comando "scp" para la transferencia de archivos                            | 200 |

| Código 96: Función "crearlmagen"                                                      | 207 |

| Código 97: Función "escribeKmeans"                                                    | 207 |

| Código 98: Función "kmeansImagen"                                                     | 210 |

| Código 99: Función para la visualización del clustering de la aplicación desarrollada | 211 |

#### **Acrónimos**

ACE AXI Coherency Extension

ACP Accelerator Coherency Port

AES Advanced Encryption Standard

ALU Arithmetic-Logic Unit

AMBA Advanced Microcontroller Bus Architecture

AMD Advanced Micro Devices

API Application Programming Interface

APU Application Processor Unit ARM Advanced RISC Machine

AXI Advanced eXtensible Interface

BRAM Block RAM

BIL Bands Interleaved by Line

BIP Bands Interleaved by Pixel

BSQ Band Sequential

CCD Charge-Coupled Device

CCI Cache-Coherent Interconnect

CMOS Complementary Metal Oxide Semiconductor

CLB Configurable Logic Block

CPU Central Processing Unit

CRC Cyclic Redundancy Checking

CSU Configuration and Security Unit

DDR Double Data Rate

DMA Direct Memory Access

DNS Domain Name System

DRAM Distributed RAM

DSP Digital Signal Processing ECC Error Correcting Code

EMIO Extended Multiplexed Input Output

EXT4 Fourth Extended File System FEC Forward Error Correction

FF Flip-Flop

FinFET Fin-shaped Field Effect Transistor

FIFO First In – First Out FPD Full-Power Domain

FPGA Field Programmable Gate Array

FPU Floating Point Unit

GIC Generic Interrupt Controller

GNU's Not Unix

GPU Graphics Processing Unit GTH Gigabit Transceiver H HLS High-Level Synthesis

HPCP High Performance Coherent Port

II Initiation Interval IP Internet Protocol

IRQ Interrupt Request

MOESI Modified Owned Exclusive Shared Invalid

MPSoC MultiProcessor System on Chip MMU Memory Management Unit

LED Light-Emitting Diode LPD Low-Power Domain

LPDDR Low Power Double Data Rate

LUT Look-Up Table

NMSC Non-Melanoma Skin Cancer

OCM On-Chip Memory

OTG On The Go

OpenCL Open Computing Language

PC Personal Computer

PCIe Peripheral Component Interconnect express

PL Programmable Logic

PS Processing System

PMU Platform Management Unit RAM Random Access Memory RGB Red, Green, and Blue ROM Read-Only Memory

RPU Real-Time Processing Unit

RSA Rivest Shamir and Adleman

RTL Register-Transfer Level

SAM Spectral Angle Mapper

SATA Serial Advanced Technology Attachment

SCU Snoop Control Unit SD Summed Distances SD Secure Digital

SEOM Sociedad Española de Oncología Médica

SFF Spectral Feature Fitting SHA Secure Hash Algorithm

SIMD Single Instruction Multiple Data

SMMU System Memory Management Unit

SoC System on Chip SRAM Static RAM SSH Secure Shell

SVM Support Vector Machine

TCF Target Communications Framework

TCM Tightly Coupled Memory

TFM Trabajo Fin Máster

TSMC Taiwan Semiconductor Manufacturing Company

XOR eXclusively-OR XRT Xilinx Runtime

XSCT Xilinx Software Command-line Tool

ULPI UTMI+ Low Pin Interface

USB Universal Serial Bus

UTMI+ USB 2.0 Transceiver Macrocell Interface

VCU Video Codec Unit

VFAT Virtual File Allocation Table

VNIR Visible and Near Infrared

### Capítulo 1. Introducción

#### 1.1. Introducción

Las imágenes hiperespectrales constituyen una herramienta de gran utilidad para su aplicación con fines analíticos. Entre sus ventajas se encuentra que constituye una operación de análisis no invasivo que no requiere la destrucción de las muestras captadas para efectuarse. Además, constituye una técnica no ionizante que no requiere de contacto físico. Estas cualidades ocasionan que las imágenes hiperespectrales se apliquen en múltiples ámbitos y disciplinas, tales como la medicina, el análisis de productos alimentarios, la agricultura o la astronomía [1], [2], [3].

Cada imagen hiperespectral constituye una matriz de datos tridimensional, también denominada hipercubo. Cabe destacar que dos de estas dimensiones se corresponden al largo y ancho espacial de la imagen. Asimismo, la otra dimensión se corresponde al dominio espectral, es decir, a las longitudes de onda electromagnética a considerar en la "visualización" y análisis por parte de la aplicación de la imagen. Esta tridimensionalidad constituye una característica que las imágenes hiperespectrales comparten con las imágenes RGB (*Red, Green and Blue*) y las imágenes multiespectrales. No obstante, las imágenes hiperespectrales se distinguen de las otras dos categorías al considerar una mayor cantidad de longitudes de ondas o bandas espectrales. Dicho aspecto se traduce en un dimensionado espectral de mayor longitud como se representa en la Figura 1. De esta manera, las imágenes hiperespectrales constituyen un recurso que permite aunar información espacial, obtenida en una imagen estándar, con la información espectral,

obtenida mediante espectroscopio, consiguiendo para ambos un nivel de resolución intermedio [1], [4].

Figura 1: Comparativa imágenes RGB, multiespectrales e hiperespectrales [5]

Mediante la combinación de información espacial y espectral, las imágenes hiperespectrales permiten determinar no solo la naturaleza de los elementos materiales observados, sino que también la distribución de estos. Para que esta información resulte útil, es necesario eliminar la influencia de factores ajenos a la composición de los materiales captados en la imagen hiperespectral. Entre estos factores se encuentra la iluminación desigual a lo largo tanto del rango espacial como espectral de la imagen, la sensibilidad no uniforme de la cámara de captación y el ruido eléctrico introducido por la cámara. Al eliminar estas influencias, se obtiene la firma espectral de cada píxel, la cual se debe al espectro de reflexión y absorción en las distintas bandas espectrales que caracterizan y distinguen entre sí a los elementos materiales observados [2], [3], [6], [7].

El caso de utilización de las imágenes hiperespectrales de este Trabajo Fin de Máster (TFM) se engloba en el ámbito de la medicina, más concretamente, en la detección de cáncer de piel. Esta enfermedad constituye uno de los tipos de cáncer más comunes a nivel mundial, distinguiéndose entre la categoría no melanoma o NMSC (*Non-Melanoma Skin Cancer*) y el melanoma [2]. De acuerdo con los datos de la Sociedad Española de Oncología Médica (SEOM), en el año 2020 se han diagnosticado en España 6.179 casos de melanoma [8]. Sin embargo, la situación de los cánceres de piel no melanoma resulta más grave, puesto que constituyen la tipología de cáncer más frecuente a nivel mundial, superando a la suma de los restos de casos de cáncer existentes. Dentro de los NMSC existen a su vez

diversas tipologías, algunas de las cuales resultan benignas mientras que otras resultan malignas [9].

Para que el tratamiento de estas patologías resulte eficaz, es necesario que la afección se detecte precozmente. Sin embargo, la distinción de cáncer piel, así como de su tipología, mediante inspección visual directa presenta bastante incertidumbre. En consecuencia, es frecuente que el médico, incluso siendo un dermatólogo experimentado, se vea obligado a recurrir a métodos invasivos como la biopsia para aseverar si el tipo de afección cutánea del paciente pertenece a una tipología benigna o maligna [2]. Ante esta situación, la utilización de imágenes hiperespectrales resulta de gran idoneidad, ya que permiten visualizar un espectro electromagnético de la imagen más amplio y preciso que el del ojo humano. De esta manera, se logra que las diferencias entre el tejido cutáneo en función de su afección resulten más evidentes. Dichas diferencias se deben a cómo los cambios bioquímicos y morfológicos que definen a las distintas lesiones se manifiestan ópticamente. Por otra parte, al ser la utilización de imágenes hiperespectrales un método no invasivo y no ionizante, se garantiza de manera absoluta que su aplicación no perjudica al tejido objeto de la evaluación [2].

Aunque la información contenida en la imagen hiperespectral facilita determinar con mayor certeza la naturaleza y la distribución de lo observado, sigue requiriéndose el análisis de los datos de la imagen hiperespectral para determinar conclusiones correctas y útiles para el problema. Dicho proceso de análisis puede automatizarse mediante algoritmos de *machine learning*, minimizándose con ello el tiempo de diagnóstico y la carga de trabajo del usuario [2], [6], [7]. En el caso de la identificación de afecciones cutáneas, la aplicación de *machine learning* resulta especialmente útil, debido a que la evaluación es fácilmente "matematizable", aunque se requiere para ello de una cantidad de datos elevada.

Para la clasificación de los píxeles, en este trabajo se ha optado por emplear un algoritmo de *machine learning* de *clustering* denominado "k-means". Dicho algoritmo subdivide las muestras, correspondientes a los píxeles de la imagen, en un conjunto de agrupaciones o *clústeres*. Esta subdivisión se efectúa a partir de la semejanza relativa presente entre las muestras en función de los atributos que se evalúen. Estos atributos se

corresponden con las bandas espectrales de la imagen hiperespectral utilizadas. El objetivo de esta segmentación consiste en que los píxeles más similares entre sí se agrupen en un mismo *clúster*, maximizando al mismo tiempo las diferencias en la firma espectral de los píxeles ubicados en *clústeres* distintos [2], [10].

Idealmente, los píxeles pertenecientes a un mismo *clúster* identifican un estado de afección de la piel similar a lo largo de la región de la piel en la que se distribuyen. Para que esta situación ocurra, deben escogerse bandas espectrales representativas, es decir, aquellas en las que el coeficiente de absorción del tejido varíe más significativamente entre los diferentes estados de afección. Además, los estados de afección deben poseer una influencia predominante con respecto a los demás factores en la variación de la firma espectral de los píxeles [2], [10]. La aplicación desarrollada permite configurar durante la compilación la cantidad de *clústeres* que el algoritmo "k-means" debe determinar. Sin embargo, los resultados y el estudio mostrados en [2] determinaron que los mejores resultados de *clustering* para este ámbito de uso se obtienen para una segmentación en 3 *clústeres*.

Desde la perspectiva de la implementación, las imágenes hiperespectrales presentan como inconveniente la inmensidad de datos que estas contienen y que deben evaluarse en la aplicación para lograr un nivel de resolución tanto espacial como espectral de la imagen que resulte suficiente. En consecuencia, la ejecución de los algoritmos de utilización y evaluación de imágenes hiperespectrales en un único hilo de ejecución requieren de un consumo de tiempo y energía elevados. Esta situación se empeora al aplicar algoritmos de *machine learning* para la clasificación de los píxeles de la imagen hiperespectral. Esto último se debe a la elevada cantidad de reevaluaciones de las muestras a clasificar que estos algoritmos precisan. Para sobrellevar estas circunstancias, resulta idóneo explorar la explotación de la computación en paralelo mediante aceleradores *hardware* que permitan un elevado grado de paralelismo del procesamiento [11]. Como recursos *hardware* que posibiliten esta función de aceleración se encuentran las GPUs (*Graphics Processing Unit*) y las FPGAs (*Field Programmable Gate Array*), utilizándose esta última tipología para esta aplicación.

La aplicación desarrollada con este trabajo está orientada a ser implementada en una placa de prototipado ZCU102 desarrollada por la empresa Xilinx. El elemento central de esta placa de prototipado consiste en un MPSoC (*MultiProcessor System on Chip*) entre cuyos recursos *hardware* se encuentran una APU (*Application Processor Unit*) de 4 núcleos y una FPGA. Este último recurso está constituido por varios tipos de módulos *hardware* de funcionalidad simple que son replicados intensivamente a lo largo de la FPGA. Se utiliza la APU como *host* de la aplicación con aceleración *hardware* a implementar. Por otra parte, la FPGA es responsable de implementar los aceleradores *hardware* de la aplicación.

Aunque la placa de prototipado de referencia sea la ZCU102, en el desarrollo de este TFM se ha procurado que la aplicación sea lo más fácilmente adaptable posible a otras circunstancias de funcionamiento. En este sentido, se han establecido una serie de parámetros de configuración, así como un procedimiento, que permite ajustar la configuración de los aceleradores *hardware* a cualquier placa de prototipado que disponga de FPGA para la función de aceleración. Estos ajustes requieren modificaciones mínimas del código fuente del usuario, y permiten optimizar el aprovechamiento de los módulos *hardware* que disponga la FPGA para conseguir el máximo rendimiento temporal. Además, se disponen de otros aspectos configurables tales como el formato de los datos de la imagen hiperespectral de entrada, las dimensiones de la imagen hiperespectral y el formato de entrada de la imagen hiperespectral. Estos dos últimos parámetros son dinámicamente ajustables, es decir, pueden cambiarse de una ejecución de la aplicación a la siguiente sin necesidad de recompilar.

#### 1.2. Objetivos

El objetivo de este Trabajo Fin Máster consiste en el análisis y diseño de una aplicación de *machine learning* para el análisis de imágenes hiperespectrales, incluyendo el preprocesamiento de las imágenes y recurriendo a la aceleración *hardware* mediante FPGA para optimizar su rendimiento. En dicho desarrollo se utiliza como referencia una aplicación análoga basada en aceleración *hardware* mediante GPUs. La programación de la aceleración *hardware* en FPGA se efectúa siguiendo la metodología HLS (*High-Level Synthesis*). Este objetivo principal se subdivide en los siguientes objetivos operacionales:

- O1. Estudiar la aplicación.

- O2. Definir la arquitectura de la aplicación, incluyendo partición hardware/software.

- O3. Modelar en alto nivel del sistema y verificación funcional.

- O4. Implementar la arquitectura sobre plataforma MPSoC.

- O5. Evaluar los resultados obtenidos

- O6. Documentar el trabajo realizado

#### 1.3. Estructura del documento

El contenido de este documento se estructura en diez capítulos, tal como se describe a continuación. En el capítulo 1. se contextualiza e introduce el trabajo abordado, definiendo los objetivos a cumplir. En el capítulo 2 se describen algunos algoritmos de *machine learning*, fundamentalmente algoritmos de *clustering*, puesto que la funcionalidad de *machine learning* implementada está englobada en esta categoría.

En el capítulo 3 se exponen diferentes aspectos acerca de las imágenes hiperespectrales y del tratamiento de la información que incluyen, clave para programar la utilización de estas imágenes. En el capítulo 4 se describe la aplicación basada en aceleración *hardware* mediante GPUs que se toma como referencia para el desarrollo de esta aplicación.

Los capítulos siguientes están orientados a la metodología de diseño e implementación. Así en el capítulo 5. se describe brevemente la placa de prototipado ZCU102 utilizada para ejecutar la aplicación sobre el MPSoC disponible. En el capítulo 6 se presentan los recursos de programación en OpenCL utilizados para la transferencia de datos y sincronización entre el *host* y los *kernels* FPGA. Para completar esta sección, en el Capítulo 7 se explica la metodología de diseño. Esta última explicación incluye la forma de emplear las directivas de compilación requeridas para controlar la síntesis de los distintos *kernels* implementados en la FPGA, así como su impacto en los resultados obtenidos.

Para concluir el trabajo, en el capítulo 8. se describe el sistema en chip desarrollado, así como los procedimientos efectuados para facilitar su depuración, su ajuste y su ejecución en la placa de prototipado. En el capítulo 9 se exponen y discuten los resultados obtenidos, tanto en términos de utilización de recursos *hardware*, como en términos de rendimiento temporal y de los resultados de salida que genera su ejecución. Finalmente, en el capítulo 10 se exponen las conclusiones de este trabajo y se indican líneas futuras propuestas como resultado de la experiencia adquirida durante el desarrollo de este trabajo.

## Capítulo 2. Machine learning

#### 2.1. Introducción

De acuerdo con Arthur Samuel, un algoritmo de *machine learning* se define como aquel que aprende y mejora su efectividad de manera autónoma evaluando los datos recibidos. Para ello, recurren al análisis estadístico con el fin de establecer predicciones lo más certeras posible. Estos algoritmos pueden subdividirse en tres clases [12]:

a. Aprendizaje supervisado. Estos algoritmos precisan, en primer lugar, tomar múltiples muestras de datos que poseen un valor de salida predefinido. Una parte de estas muestras se emplean en el entrenamiento del algoritmo. Dicho proceso consiste en ajustar la funcionalidad y los parámetros de las operaciones internas del algoritmo con el objetivo de maximizar que los datos salientes se asemejen a los valores de salida preestablecidos para cada muestra. Posteriormente, se utilizan el resto de las muestras de salida predefinida para verificar que las operaciones del algoritmo estén bien ajustadas. Estos procesos posibilitan que el algoritmo sea capaz de determinar qué salida le corresponde a cada muestra de entrada posterior sin necesidad de que se le especifique explícitamente cuál es la salida esperable.

Este tipo de algoritmos se utilizan, por ejemplo, en la detección de *spam* en los mensajes de correo electrónico. El valor saliente puede ser la pertenencia de la muestra a alguna categoría preestablecida o algún valor cuantitativo. En la primera situación, se considera que el algoritmo de *machine learning* es de clasificación. En el otro caso, se considera como un algoritmo de regresión [12], [13], [14].

- b. Aprendizaje sin supervisión. Estos algoritmos comienzan directamente con la evaluación de muestras no preclasificadas, sin ningún entrenamiento previo. El objetivo de estos algoritmos puede consistir en establecer agrupaciones basándose en las similitudes entre las muestras entrantes. Los algoritmos de estas características se denominan algoritmos de clustering.

- Por otra parte, se encuentran los algoritmos cuyo propósito consiste en identificar correlaciones entre los atributos o características de las muestras evaluadas. Dichos algoritmos se categorizan como algoritmos de asociación, [12], [13], [14].

- c. Aprendizaje mediante refuerzo. El algoritmo, también definido como agente en esta categoría, aprende al interactuar con el entorno considerado. Este aprendizaje puede entenderse desde la dinámica de premio y castigo. Asimismo, cada acción ejecutada por el algoritmo conlleva una valoración. Esta valoración puede resultar negativa (castigo) o positiva (recompensa) en función de las consecuencias que originan y de cómo estas se ajustan a lo deseable. El objetivo del algoritmo consiste en maximizar la recompensa. Por consiguiente, dicho algoritmo reiterará aquellas acciones que otorgaron una mayor valoración positiva. Simultáneamente, el algoritmo evitará las acciones que conllevaron una valoración negativa [12], [13], [14].

#### 2.2. Información de entrenamiento

La fiabilidad y calidad de los datos de entrada constituyen aspectos claves para la veracidad de los resultados de *machine learning*. Esto es relevante en las muestras de entrenamiento supervisadas. No obstante, las muestras pueden contener errores o defectos de información. Se necesita, por tanto, que el sistema presente cierta capacidad tratar estos defectos sin que se modifiquen los resultados obtenidos.

Los defectos más relevantes identificados son los siguientes [10], [14]:

a. **Atributos irrelevantes**. Es posible que algunos de los atributos considerados para las muestras resulten inútiles, puesto que carezcan de influencia y correlación con la categoría a la que cada muestra pertenezca. Este hecho implica una carga

- computacional innecesaria, aunque inevitable en aquellos algoritmos en los que el establecimiento de los atributos esté automatizado, sin ser el usuario o programador quien directamente los escoja [10], [14].

- b. Ausencia de atributos representativos. Contrariamente al caso anterior, otro defecto que puede ocurrir consiste en la desconsideración en el cómputo del algoritmo de atributos representativos, es decir, que poseen gran utilidad para discernir la pertenencia de las muestras a las categorías existentes. Este defecto puede ocasionar incongruencias en el criterio de clasificación determinado, e incluso impedir que las muestras sean clasificadas correctamente por el algoritmo [10], [14].

- c. Atributos redundantes. Ocurre cuando 2 o más atributos pueden inferirse mutuamente. Para ejemplificar este defecto, considérese un caso donde las muestras de entrenamiento son un conjunto de personas y 2 de los atributos son sus fechas de nacimiento y sus edades. En dicho caso, aunque la información de estos atributos fuera relevante para la clasificación, se puede escoger prescindir de uno cualquiera de ellos. Dicha decisión no afectaría significativamente a los resultados obtenidos de manera relevante y supondría un ahorro de carga computacional. No obstante, la importancia de este defecto en comparación con los comentados en los párrafos anteriores es muy minoritaria [10], [14].

- d. **Valor desconocido**. Puede suceder que el valor de algunos atributos se desconozca para algunas muestras [10], [14].

- e. Valores de atributos erróneos. Los valores de los atributos pueden presentar cierto margen de error. Entre las causas de este defecto podemos citar: recurrir a fuentes de información poco fiables, erratas, la inexactitud de los instrumentos de medida o la equivocación del usuario [10], [14].

- f. Categorías mal definidas. Esta condición puede causar que las muestras no se adecúen correctamente a las categorías definidas atendiendo a los valores de sus atributos. Consecuentemente, una mínima variación en los valores de los atributos de la muestra puede traducirse en una errónea clasificación de la misma [10], [14].

### 2.3. Clasificadores lineales y polinómicos

Los clasificadores lineales y polinómicos constituyen algoritmos de *machine learning* supervisados. Para entender estos clasificadores, deben entenderse las muestras de entrenamiento como puntos distribuidos en un espacio vectorial cuyas dimensiones se corresponden a los atributos de las muestras. Estas muestras de entrenamiento se emplean para determinar las regiones que se asocian a cada clase. Asimismo, las muestras posteriores se clasificarán dependiendo las regiones delimitadas [10], [14].

La correcta delimitación de las regiones recae en la correcta definición y determinación de sus fronteras. Dichas fronteras se describen matemáticamente mediante una o varias ecuaciones lineales o polinómicas. Cada una de estas ecuaciones permitirán establecer una separación binaria entre las muestras pertenecientes a una determinada clase y las demás. En el caso de las ecuaciones polinómicas, el grado deberá ser mayor cuanto más complejas resulte la frontera que describe. Con respecto a la ecuación lineal, esta se ajustará a la fórmula expuesta en la ecuación (1). En dicha ecuación, "x<sub>i</sub>" identifica a los atributos de las muestras a clasificar. Además, los parámetros "w<sub>i</sub>" indican la ponderación otorgada al atributo que multipliquen, pudiendo ser un valor positivo o negativo. Por último, "w<sub>0</sub>" representa el valor umbral [10], [14].

$$w_0 + \sum_{i=1}^n w_i x_i = 0 (1)$$

El propósito del entrenamiento de los clasificadores lineales consistirá en establecer el valor de los parámetros de ponderación ("w<sub>i</sub>" y "w<sub>0</sub>"). Asimismo, la categorización de la muestra a clasificar depende del resultado obtenido al considerar el valor de sus atributos. En este aspecto, la muestra se clasificará como perteneciente a una clase o a otra según esta tome un valor positivo o negativo. Si el resultado es 0, significa que la muestra se localiza exactamente en la frontera entre clases que establece la ecuación. En este caso excepcional, la clasificación de la muestra puede asignarse de manera aleatoria, o bien a la clase mayoritaria entre las muestras de entrenamiento.

Existen varios algoritmos para determinar los coeficientes w consistentes en el ajuste progresivo de los mismos mediante estrategias de ensayo-error. Entre estos

algoritmos se encuentra el de *Perceptron*, que actualiza los coeficientes mediante sumas y restas, y el de *WINNOW*, que recurre a la multiplicación y a la división para dicha actualización. Otro caso de algoritmo de clasificación lineal o polinómica relevante se corresponde al algoritmo SVM (*Support Vector Machine*) [10], [14].

#### 2.3.1. Support Vector Machine (SVM)

En clasificadores polinómicos, el *Support Vector Machine* (SVM) constituye un procedimiento que, aparte de determinar una ecuación que separe un conjunto de muestras preclasificadas en función de 2 clases preexistentes, pretende maximizar la distancia de separación entre la representación de esta ecuación en el espacio vectorial y las muestras. Para ello, se establecen como referencia dos muestras, una en cada región delimitada por la ecuación. Dichas muestras deben pertenecer a la clase correspondiente a dicha región y ser las más próximas en sus respectivas clases al hiperplano definido. Las dos muestras que cumplan estos requisitos se denominan vectores de soporte o *support vectors* [10]. Para su determinación, se ajusta la ecuación de clasificación expuesta en la ecuación (2) para los vectores de soporte.

$$\left| w_0 + \sum_{i=1}^n w_i x_i \right| = 1 \tag{2}$$

De esta manera, si el clasificador polinómico es correcto, todas las muestras de entrenamiento deberán originar un resultado igual o superior a la unidad. Los coeficientes "w<sub>i</sub>" que ponderan la influencia de un determinado atributo "x<sub>i</sub>" se determinan como la diferencia de valor en dicho atributo entre los vectores de soporte. La ecuación (2) presenta 2 vertientes, una correspondiente a las muestras que presentan una clasificación negativa (y=-1) y otra para las que presentan una clasificación positiva (y=1). Asimismo, en el caso de las muestras clasificadas como negativas el resultado del argumento de la función de extracción del valor absoluto debe resultar menor o igual a -1, mientras que las otras muestras deberán dar un resultado igual o superior a 1. Considerando "y-" la clasificación de las muestras pertenecientes a las clases negativas e "y+" la de las muestras de la clase positiva, las muestras de entrenamiento deben ajustarse a las inecuaciones expuestas en la ecuación (3) [13].

$$y_{+}\left(w_{0} + \sum_{i=1}^{n} w_{i} x_{i}\right) \ge 1$$

$$y_{-}\left(w_{0} + \sum_{i=1}^{n} w_{i} x_{i}\right) \ge 1$$

$$(3)$$

Dependiendo de la exigencia de la aplicación con respecto a las clasificaciones erróneas, el SVM se subdivide en dos modalidades denominadas *hard-margin* y *soft-margin*. La modalidad *hard-margin* constituye la opción que establece que el clasificador SVM desarrollado debe categorizar correctamente cada una de las muestras de entrenamiento. Este hecho implica que, al menos en el espacio vectorial creado por los atributos de las muestras, las clases deben ser linealmente separables. Por otro lado, la *soft-margin* consiente una cierta cantidad de errores como aceptables [15].

Estas versiones básicas del clasificador solo resultan útiles para problemas de clasificación lineales. Sin embargo, es posible extender la funcionalidad a problemas de clasificación no lineales mediante la incorporación de *kernels*. En este contexto, un *kernel* se define como una función matemática cuyas variables independientes se corresponden a atributos de las muestras. Como resultado, se obtienen una serie de nuevos atributos derivados matemáticamente de los atributos originales.

La inclusión de nuevos atributos para la descripción de las muestras introduce nuevas variables para expresar la ecuación lineal del clasificador. De esta manera, se facilita la posibilidad de que las muestras sean linealmente separables, reinterpretando la ecuación lineal resultante como una ecuación no lineal desde la perspectiva de los atributos originales. Para ello, es suficiente con invertir la operación de los *kernels* sobre la determinación de los atributos derivados de la ecuación lineal [15].

Las funciones *kernel* pueden ser de diversa índole. Sin embargo, dependiendo de la distribución de las muestras a lo largo del espacio vectorial, la utilidad de la función escogida para posibilitar una separación lineal entre las clases varía notablemente [15].

Algunos de los kernels más comúnmente usados son los siguientes:

*Kernels* radiales. Estos *kernels* se ajustan a la ecuación expuesta en (4). En dicha ecuación, "x" representa un conjunto de los atributos iniciales de la muestra, mientras "x"

constituye los valores para cada atributo en los que se maximiza el valor del atributo derivado, es decir, el resultado de la ecuación [15].

$$K(x, x') = e^{-\gamma ||x - x'||^2}$$

(4)

La denominación de este *kernel* como radial se debe a que, considerando "x" y "x" vectores con una cantidad de dimensiones cualquiera, el valor de salida del *kernel* para cualquier muestra disminuirá cuanto más se aleje del punto de referencia "x" dentro del espacio vectorial. Asimismo, la dirección en la que se oriente dicho distanciamiento carecerá de efecto sobre el resultado del *kernel*. En la Figura 2 se representa la utilización de los *kernels* para establecer la separación lineal entre clases [15].

Figura 2: Aplicación de kernel radial para separar clases linealmente [16]

Otro parámetro relevante es " $\gamma$ ", el cual establece cuán significativo es el decaimiento del resultado del *kernel* para un mismo grado de divergencia entre "x" y "x'". Desde el punto de vista gráfico, este hecho implica que cuanto mayor sea el valor de " $\gamma$ " más estrecha será la concavidad de la representación del *kernel* en función del parámetro "x". Debido a ello, la utilización de *kernels* con mayor " $\gamma$ " permite dibujar, desde la perspectiva del espacio vectorial formado por los atributos originales, fronteras más complicadas y con mayores grados de curvaturas. Un ejemplo de este caso se presenta en la Figura 3 [15].

Figura 3: Caso de "\gamma" reducida (parte izquierda) y elevada (parte derecha) [17]

Cabe destacar que un mayor " $\gamma$ " reduce la probabilidad de que el clasificador inferido coloque las muestras de entrenamiento preclasificadas en regiones no correspondientes a sus clases. Sin embargo, un valor excesivo de " $\gamma$ " conduce al sobreajuste u *overfitting*, es decir, que el clasificador desarrollado esté demasiado particularizado para el conjunto de muestras de entrenamiento utilizado, siendo incapaz de categorizar correctamente otros conjuntos de muestras con un grado de acierto razonable [15].

#### 2.3.2. Clasificadores binarios múltiples

En los algoritmos de clasificación lineal y polinómica, cada ecuación constituye un clasificador binario, puesto que solo distingue en dos categorías según el resultado que devuelva la muestra. Por ello, si se desea clasificar las muestras en más de dos clases, la manera más habitual de proceder consiste en aplicar múltiples ecuaciones. Cada una de las ecuaciones se asigna unívocamente a una de las clases definidas para la clasificación. De esta manera, el cometido de cada ecuación consiste en separar las muestras pertenecientes a la clase asignada de las demás. Cada una de estas ecuaciones se extrae utilizando un algoritmo de clasificación binario, como los algoritmos de *Perceptron*, *WINNOW* y SVM indicados anteriormente [10], [14].

Considerando que cada muestra debe pertenecer solamente a una clase, debe suceder, desde la perspectiva aritmética, que cada muestra retorne un resultado positivo para una de las ecuaciones y un resultado negativo para las ecuaciones restantes, considerando el resultado positivo como la asignación a la clase asociada a la ecuación.

Desde la perspectiva gráfica, esto implicaría que las regiones delimitadas por las ecuaciones no se intercepten. No obstante, esta situación puede no suceder debido a que las muestras de entrenamiento resulten demasiado escasas o poco adecuadas para ajustar la ecuación con la precisión adecuada a la región del espacio vectorial en la que se encuentran las muestras pertenecientes a la categoría que distinga.

Por otra parte, puede ocurrir que las regiones sean demasiado complejas para el grado de ecuación considerado, en el caso de los algoritmos de *Perceptron* y *WINNOW*, o para la capacidad de complejidad de las ecuaciones que posibilitan los *kernels* en el caso del SVM. En estos casos, las regiones de las clases no podrían acotarse con suficiente precisión, siendo posible que las aproximaciones a estas regiones que efectúen las ecuaciones se entrecorten. Para solventar esta circunstancia, suele considerarse que la muestra pertenece a la clase cuya ecuación devuelve un resultado más elevado [10], [14].

Este procedimiento para la clasificación de las muestras en más de dos clases solo es fiable si la cantidad de clases definidas es relativamente pequeña, en torno a 3 y 5. El motivo de ello se encuentra en que considerar más clases ocasionaría una relación demasiado desproporcionada entre las muestras de entrenamiento preclasificadas como positivas y las de valor negativo en cada ecuación, siendo los casos de clasificación negativa mayoritarios. En consecuencia, sería difícil la correcta clasificación de las muestras en aquellos casos en los que los valores de los atributos posean cierto grado de error en las muestras [10], [14].

### 2.4. Clustering

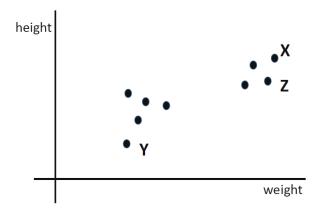

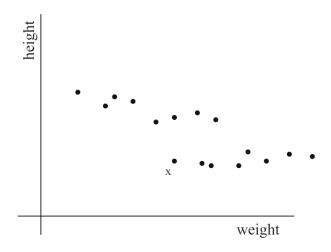

Un algoritmo de *clustering* se define como aquel que divide un conjunto de muestras no preclasificadas en varias agrupaciones o *clústeres*. Asimismo, los valores que los atributos de una muestra deben poseer para que esta se asigne a un determinado *clúster* no se encuentran predefinidos. En su lugar, cada muestra se asignará al *clúster* que contenga las muestras con el mayor grado de semejanza promedio. En consecuencia, cada *clúster* agrupará las muestras que presenten una mayor similitud entre ellas y, simultáneamente, una mayor diferenciación en promedio a las muestras asignadas a otros *clústeres*. En la Figura 4 se presenta un ejemplo con un conjunto de muestras distribuidas,

en función del valor de sus atributos "height" y "weight", en un espacio vectorial bidimensional. En dicho ejemplo, los clústeres a establecer resultan evidentes, pudiendo seguir las subdivisiones redondeadas [10], [14].

Figura 4: Ejemplo de detección de clústeres [10]

Durante el trascurso del algoritmo, los *clústeres* deben designarse según su ubicación en el espacio vectorial, su tamaño o su distribución. Para esta identificación, puede recurrirse a los centroides. El centroide de un *clúster* indica la posición obtenida al promediar los valores para cada coordenada o atributo de las muestras pertenecientes al *clúster*. De esta manera, el criterio de asignación de *clúster* más habitual se basa en calcular, para cada agrupación existente, la distancia vectorial que separa la muestra a clasificar del centroide. Consecuentemente, la muestra se asocia al *clúster* cuyo centroide se halle más próximo y, por tanto, similar [10], [14].

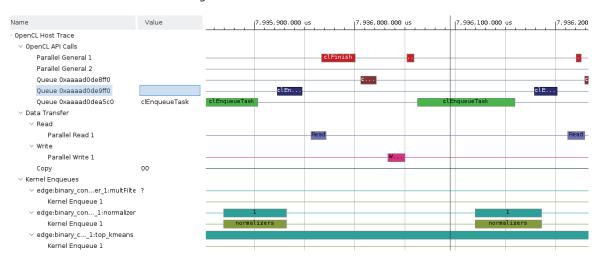

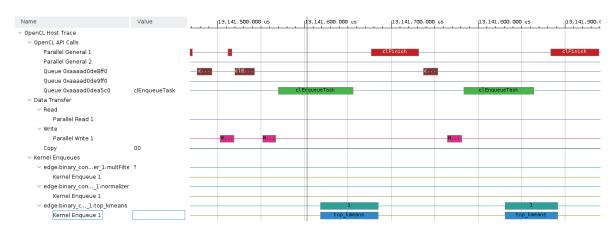

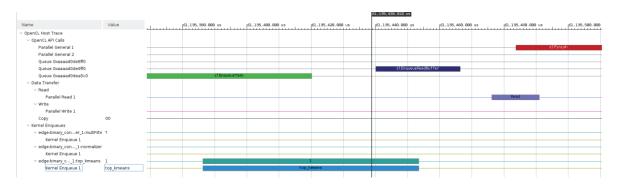

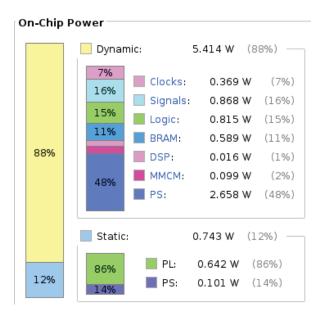

Una misma muestra no debe pertenecer a varios *clústeres*. No obstante, las muestras pueden reclasificarse durante la ejecución del algoritmo. La cantidad de *clústeres* a considerar es variable. Las restricciones en esta cantidad se corresponden, en el límite inferior, a un solo *clúster* que agruparía la totalidad de las muestras evaluadas. El límite superior se corresponde a tantos *clústeres* como muestras. En este último caso, cada *clúster* abarcaría una sola muestra. La cantidad de *clústeres* puede ser preestablecida por el usuario, o ser estimada por el algoritmo. Los algoritmos de *clustering* resultan de gran utilidad, y en muchos casos, estos algoritmos se utilizan para complementar aplicaciones de *machine learning* de aprendizaje supervisado [10], [14].