# Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

## Trabajo Fin de Máster

Diseño de un amplificador de bajo ruido en la banda K/Ka para receptores de 5G usando tecnología SOI

Néstor Cecilio García Vélez Autor:

Tutor(es): Dr. Francisco Javier del Pino Suárez

D. David Galante Sempere

Fecha: Diciembre de 2023

### Instituto Universitario de Microelectrónica Aplicada

# Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

## Trabajo Fin de Máster

Diseño de un amplificador de bajo ruido en la banda K/Ka para receptores de 5G usando tecnología SOI

### **HOJA DE FIRMAS**

Néstor Cecilio García Vélez Fdo.: Alumno/a:

Tutor/a: Dr. Francisco Javier del Pino Suárez Fdo.:

Tutor/a: Fdo.: D. David Galante Sempere

Fecha: Diciembre de 2023

## Instituto Universitario de Gran Canaria Microelectrónica Aplicada

# Máster Universitario en Electrónica y Telecomunicación Aplicadas (META)

# Trabajo Fin de Máster

## Diseño de un amplificador de bajo ruido en la banda K/Ka para receptores de 5G usando tecnología SOI

## HOJA DE EVALUACIÓN

| Calificación:            |       |

|--------------------------|-------|

| Presidente               | Fdo.: |

| Secretario               | Fdo.: |

| Vocal                    | Fdo.: |

| Fecha: Diciembre de 2023 |       |

## Agradecimientos

A David Galante, por tu apoyo incondicional, empatía, paciencia y por enseñarme el maravilloso mundo de la microelectrónica de esa forma tan cercana y con esa gran capacidad de enseñar que tienes. Ha sido un placer para mí trabajar durante estos años contigo.

A Javier del Pino por transmitirme los conocimientos de los circuitos integrados y la radiofrecuencia, así como por su dedicación.

A mi familia y a Leticia, por apoyarme en cada pequeño paso y alentarme en los momentos más difíciles.

Pero en especial a mi Abuela, sé que allá donde estés seguirás acompañándome y estando orgullosa de mí.

### Resumen

En este Trabajo Fin de Máster se realiza el diseño de un amplificador de bajo ruido (LNA) a una frecuencia de trabajo de 30 GHz en una tecnología de 45RFSOI. Dado que el estándar de comunicaciones 5G opera sobre la banda K, alrededor de 28 GHz, el diseño de un LNA de reducido consumo y elevadas prestaciones a esta frecuencia es de especial interés.

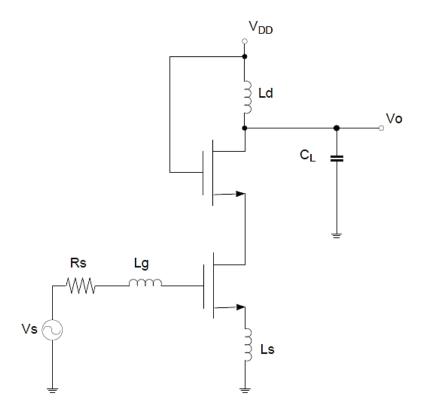

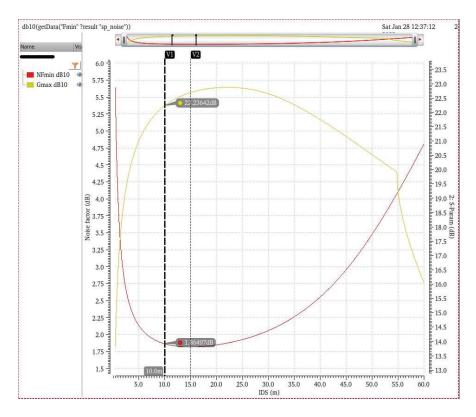

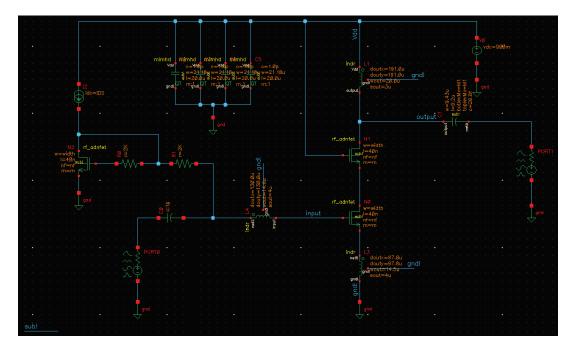

El proceso de diseño seguido es, en primer lugar, realizar una fase de estudio para contextualizar las tecnologías 5G y 45RFSOI, la teoría de los LNAs, así como otros trabajos para tener una estimación sobre las prestaciones obtenidas. A raíz de dicha investigación, se comienza la fase de diseño del LNA a nivel de esquemático de un cascodo con dos transistores nMOS apilados, en configuración de *Common-Gate* (CG) y *Common-Source* (CS) respectivamente. Además, se emplea una bobina en la puerta del transistor en CS para conseguir una adaptación de entrada óptima y una bobina de degeneración inductiva en el terminal de fuente de dicho transistor para reducir la figura de ruido (NF), mejorar la estabilidad y aproximar la impedancia de entrada a la impedancia óptima para mínimo ruido. A su vez, el transistor en CG está conectado en el terminal de drenador a una bobina, cuya función es maximizar la ganancia del dispositivo.

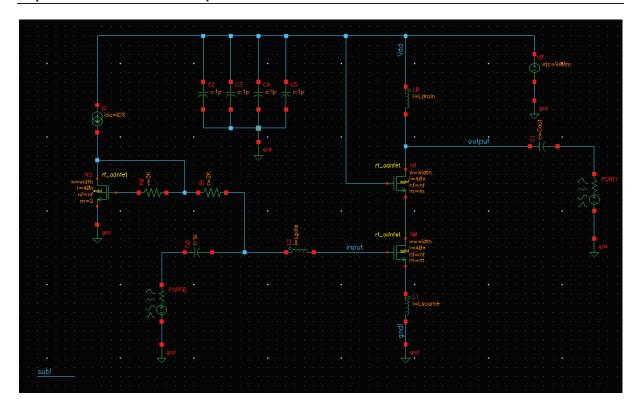

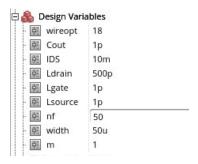

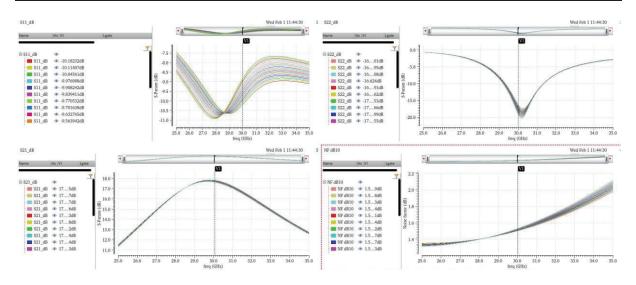

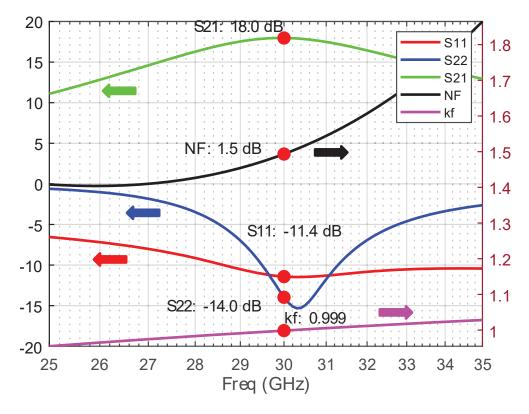

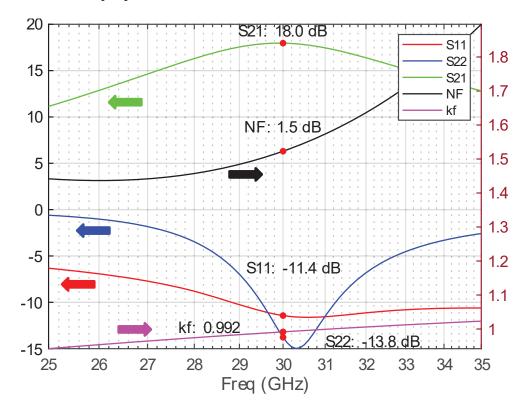

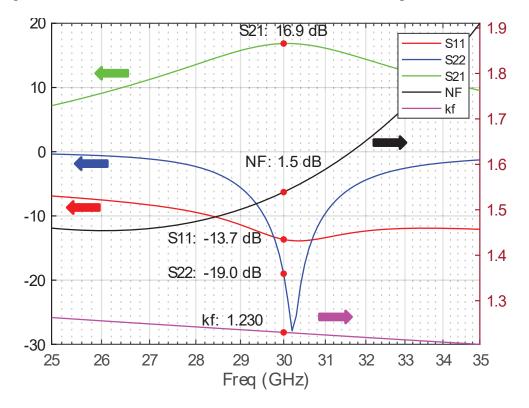

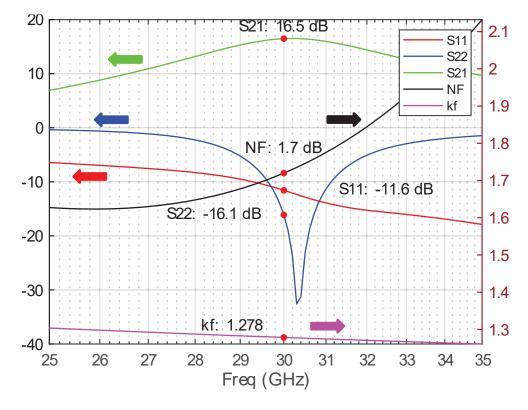

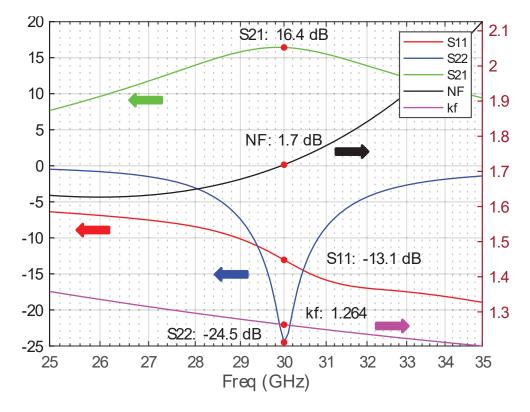

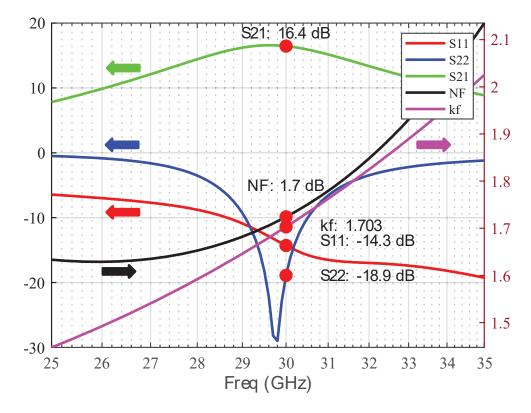

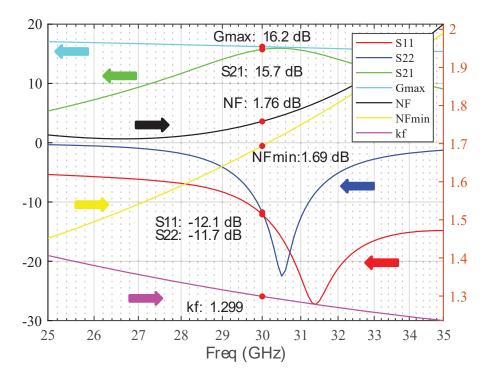

Para diseñar el amplificador a nivel de esquemático, se estudia la densidad de corriente y geometría óptimas para alcanzar el mejor compromiso entre prestaciones y consumo, obteniendo una ganancia equivalente a 18 dB y una figura de ruido de 1.5 dB. El siguiente paso consiste en la sustitución de componentes por los de la tecnología, consiguiendo una ganancia de 16.5 dB y una figura de ruido de 1.7 dB.

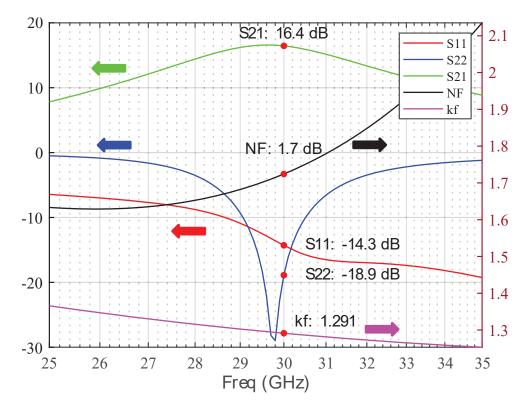

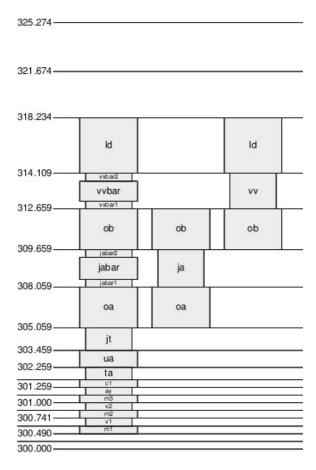

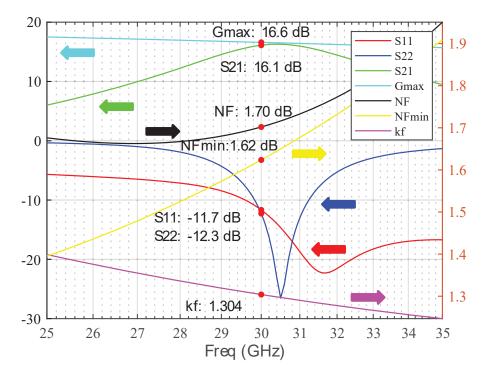

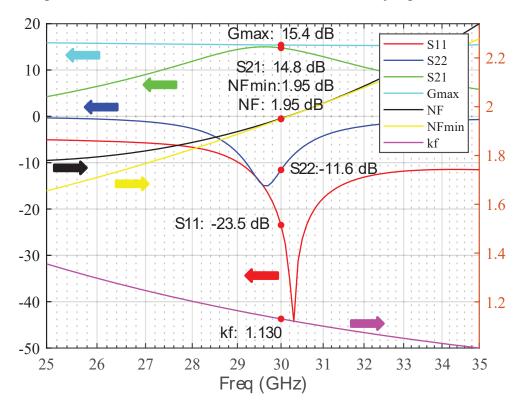

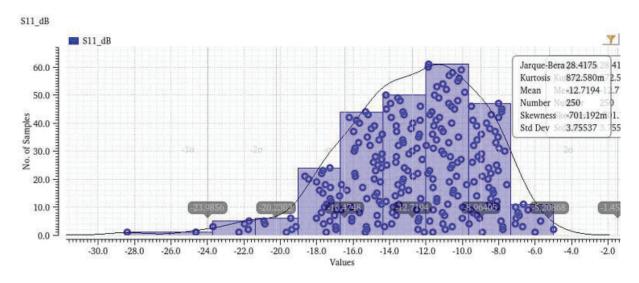

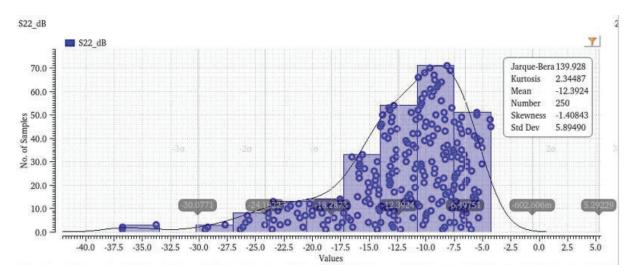

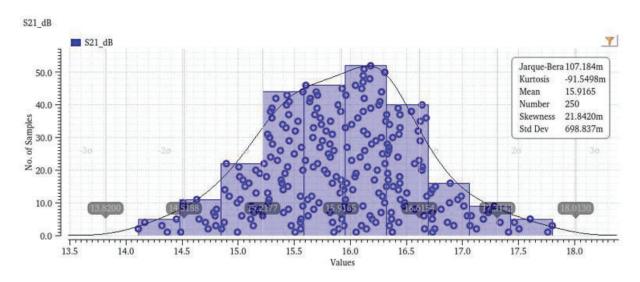

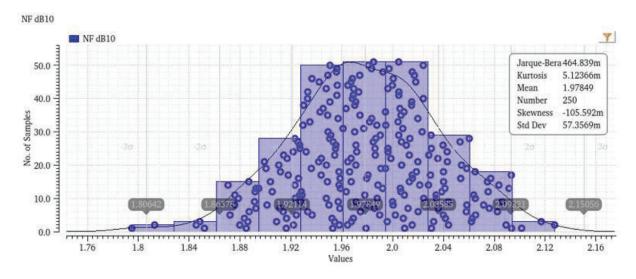

Tras concluir el diseño de los esquemáticos, se pasa a implementar el circuito a nivel de *layout*. Para ello, se obtiene primero un modelo del transistor teniendo en cuenta los componentes parásitos del *layout*, así se incluyen estas desviaciones desde el inicio del proceso de diseño. Posteriormente, se reajustan los componentes empleados y se pasan las reglas de diseño, así como se verifica que el esquemático y el *layout* coinciden. Asimismo, se realizan extracciones de capacidades parásitas y simulaciones electromagnéticas de los componentes, y se incluyen en el diseño para comprobar cómo afectan a las prestaciones. Para finalizar el flujo de diseño, se realizan las simulaciones *post-layout*, dónde se aplica un análisis de Monte Carlo de 250 ensayos, obteniendo una ganancia media de 15.9 dB y una figura de ruido media de 2 dB.

### **Abstract**

In this Final Master's Thesis, a low noise amplifier (LNA) at a working frequency of 30 GHz in a 45RFSOI technology is designed. As the 5G communications standard operates in the K-band, around 28 GHz, the design of a low-power LNA with high performance at this frequency is interesting.

The design process followed is, firstly, to make a study phase to contextualise the 5G and 45RFSOI technologies, the theory of LNAs, as well as other works to have an estimate of the performance obtained. As a result of this research, the design phase of the LNA begins at the schematic level of a cascode with two stacked nMOS transistors, in Common-Gate (CG) and Common-Source (CS) configuration respectively. In addition, an inductor at the gate of the CS transistor is used to achieve optimal input matching and an inductive degeneration inductor is used at the source terminal of the CS transistor to reduce the noise figure (NF), improve stability and approximate the input impedance to the optimal impedance for minimum noise. In turn, the transistor in CG is connected at the drain terminal to a inductor, whose function is to maximise the gain of the device.

To design the amplifier at the schematic level, the optimum current density and geometry are studied to achieve the best compromise between performance and consumption, obtaining a gain equivalent to 18 dB and a noise figure of 1.5 dB. The next step consists of replacing components with those of the technology, achieving a gain of 16.5 dB and a noise figure of 1.7 dB.

Once the schematic design has been completed, the circuit is implemented at the layout level. For this purpose, a complex model of the transistor is obtained, considering the parasitic components of the layout, so that these deviations are included from the beginning of the design process. Then, the components used are readjusted and the design rules are passed on, as well as verifying that the schematic and the layout match. Parasitic capacitance extractions and electromagnetic simulations of the components are also performed and included in the design to check how they affect performance. To finalise the design flow, post-layout simulations are executed, where a Monte Carlo analysis of 250 trials is applied, obtaining an average gain of 15.9 dB and an average noise figure of 2 dB.

# Índice de contenido

| Capítulo 1. Introducción                       | 1  |

|------------------------------------------------|----|

| 1. Antecedentes                                | 2  |

| 2. Tecnologías 5G                              | 3  |

| 3. Objetivos                                   | 6  |

| 4. Estructura del documento                    | 7  |

| Capítulo 2. Estado del Arte                    | 9  |

| 1. Teoría Básica LNAs                          | 9  |

| I. Parámetros S y Carta de Smith               | 9  |

| II. Figura de ruido                            | 11 |

| III. Ganancia                                  | 12 |

| IV. Linealidad                                 | 12 |

| V. Estabilidad                                 | 11 |

| 2. Estado del arte de LNAs para tecnologías 5G | 13 |

| 3. Conclusiones                                | 23 |

| Capítulo 3. Estudio de la Tecnología 45RFSOI   | 25 |

| 1. Introducción a la tecnología                | 25 |

| 2. Elementos Pasivos                           | 25 |

| I. Resistencias                                | 25 |

| II. Condensadores                              | 26 |

| III. Bobinas                                   | 28 |

| 3. Elementos Activos                           | 31 |

| I. Transistores                                | 31 |

| 4. Conclusiones                                | 33 |

| Capítulo 4. Diseño a Nivel de Esquemático      | 35 |

| 1. LNA en cascodo                              | 35 |

| 2. Diseño con componentes ideales              | 36 |

| I. Proceso de diseño                           |    |

| 3. Diseño con componentes reales               | 45 |

|                                                |    |

| marce de contemao                                       |      |

|---------------------------------------------------------|------|

| 4. Conclusiones                                         |      |

| Capítulo 5. Diseño a Nivel de Layout                    | . 55 |

| 1. Proceso de Diseño                                    | . 55 |

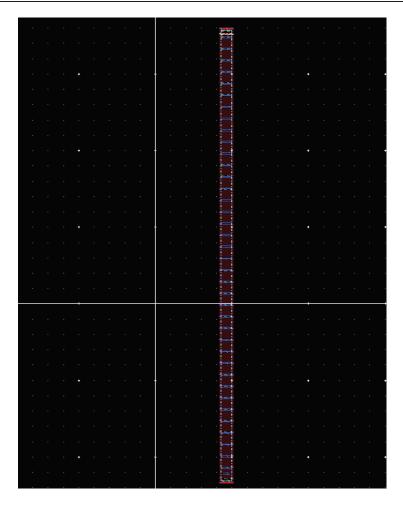

| 2. Layout del transistor                                | . 58 |

| I. Layout del cascodo                                   | . 62 |

| II. Modelo complejo del cascodo                         | . 64 |

| 3. Layout de las bobinas                                | . 72 |

| I. Bobina de drenador                                   | . 73 |

| II. Bobina de puerta                                    | . 74 |

| III. Bobina de fuente                                   | . 75 |

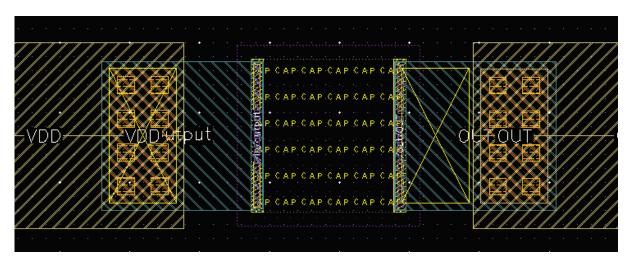

| 4. Layout de los condensadores                          | . 80 |

| 5. Layout completo sin <i>pads</i>                      | . 81 |

| 6. Layout completo con pads                             | . 82 |

| 7. Conclusiones                                         | . 86 |

| Capítulo 6. Resultados de Simulación <i>Post-Layout</i> | . 89 |

| 1. LNA con modelo EM de los pasivos                     | . 89 |

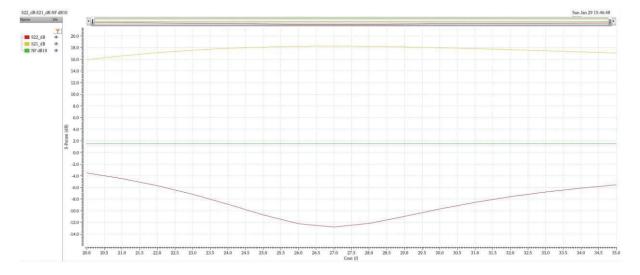

| 2. Monte Carlo                                          | . 95 |

| 3. Conclusiones                                         | . 98 |

| Capítulo 7. Conclusiones                                | . 99 |

| 1. Resumen del trabajo realizado                        | . 99 |

| 2. Recopilación de resultados                           | . 99 |

| 3. Líneas de trabajo futuro                             | 102  |

| Bibliografia                                            | 105  |

# Índice de figuras

| Figura 1. Diagrama de bloques de un transceptor convencional                               | 2     |

|--------------------------------------------------------------------------------------------|-------|

| Figura 2. Aplicaciones de la pirámide 5G.                                                  |       |

| Figura 3. Cuadripolo con las ondas incidentes y reflejadas en cada puerto y los parámet    |       |

| [13]                                                                                       | 10    |

| Figura 4. Ejemplo de una Carta Smith [13]                                                  |       |

| Figura 5. Representación gráfica de los productos de intermodulación de segundo y tercer o | orden |

| y el cálculo del IP3 para una determinada potencia de entrada [16]                         | 13    |

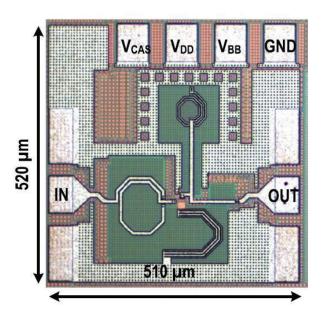

| Figura 6. LNA a 28 GHz diseñado con 45RFSOI [17].                                          | 14    |

| Figura 7. Esquemático del LNA de banda ultra ancha entre 24 y 44 GHz [17]                  | 15    |

| Figura 8. Parámetros S del LNA de banda ancha (a) y del LNA de banda ancha a 28 GH         |       |

| [17]                                                                                       | 15    |

| Figura 9. Esquemático del LNA a 28 GHz bajo una tecnología de 28 nm CMOS [18]              | 17    |

| Figura 10. Layout del LNA a 33 GHz para el receptor 5G.                                    | 18    |

| Figura 11. Comparativa de los parámetros S medidos frente a los simulados                  | 18    |

| Figura 12. Esquemático del cascodo en configuración CG-CS [19]                             | 19    |

| Figura 13. Resultados de la figura de ruido mínima y la ganancia frente a la densida       | ad de |

| corriente [19].                                                                            | 20    |

| Figura 14. Implementación a nivel físico del LNA [19].                                     | 21    |

| Figura 15. Esquemático del LNA implementado con los valores de los componentes [20]        | 22    |

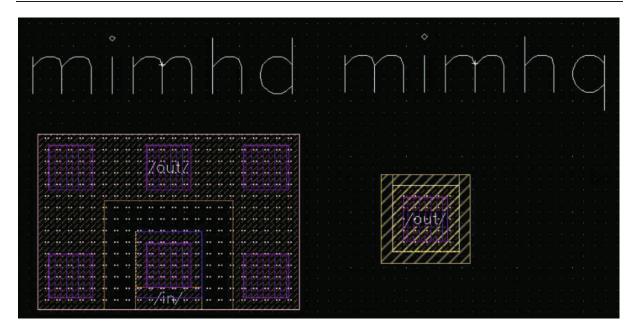

| Figura 16. Implementación del chip con las medidas y los terminales [20]                   | 22    |

| Figura 17. Modelo simplificado de una resistencia [21].                                    | 26    |

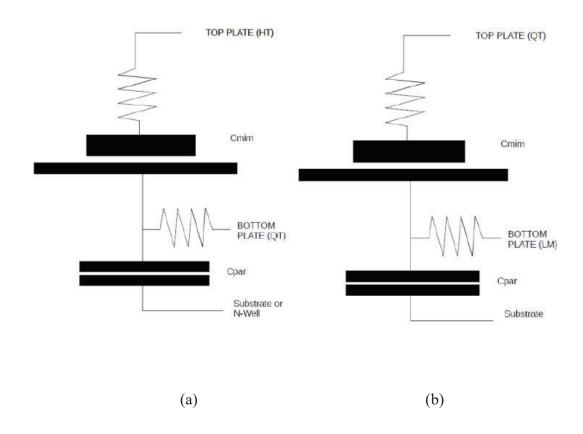

| Figura 18. Esquemático del condensador mimhd (a) y mimhq (b)                               | 27    |

| Figura 19. Layout de las condensadores mimhd y mimhq [16]                                  | 28    |

| Figura 20. Estructura de una inductancia cuadrada en espiral simple [21]                   | 29    |

| Figura 21. Inductancia en espiral rectangular con los parámetros de diseño [25]            | 29    |

| Figura 22. Layout de una bobina asimétrica sin apilar (INDR).                              | 30    |

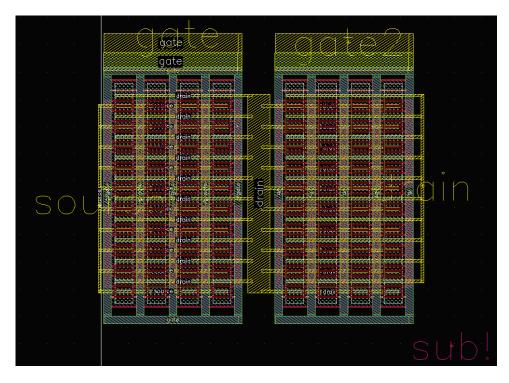

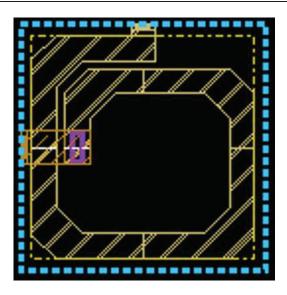

| Figura 23. Layout del transistor ADNFET empleado.                                          | 32    |

| Figura 24. Esquemático de un cascodo sencillo [16].                                        | 36    |

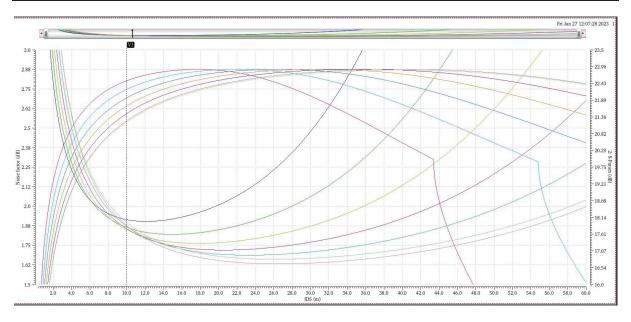

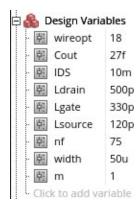

| Figura 25. Esquemático inicial para dimensionar el transistor                              | 38    |

| Figura 26. Configuración inicial sobre la que se dimensionan los transistores              | 38    |

| Figura 27. Resultados de la corriente de polarización en función de la ganancia y la figu  | ra de |

| ruido                                                                                      | 39    |

| Figura 28. Resultados de la ganancia y la figura de ruido en función de la corrient        | te de |

| polarización variando los valores del ancho del transistor desde 40 μm a 100 μm            | 40    |

| Figura 29. Barridos de nf desde 25 fingers hasta 100 fingers para determinar las dimensione   | 38 |

|-----------------------------------------------------------------------------------------------|----|

| del transistor                                                                                | -1 |

| Figura 30. Barrido de Lsource desde 25 pH hasta 150 pH en pasos de 5 pH 4                     | 1  |

| Figura 31. Barrido de Lgate desde 50 pH hasta 550 pH en pasos de 5 pH 4                       | -2 |

| Figura 32. Ajuste del valor de Lgate en función de la Carta Smith para obtener una adaptació  | n  |

| de entrada próxima a 50 $\Omega$                                                              | -2 |

| Figura 33. Valores de los distintos parámetros en la frecuencia de trabajo                    | .3 |

| Figura 34. Barrido desde 20 fF hasta 35 fF en pasos de 1 fF para ajustar Cout                 | .3 |

| Figura 35. Reajuste de Lgate para mantener un compromiso entre los parámetros del diseño      | 0. |

| 4                                                                                             | 4  |

| Figura 36. Valores de los componentes ideales                                                 | 4  |

| Figura 37. Resultados finales del diseño basado en componentes ideales                        | -5 |

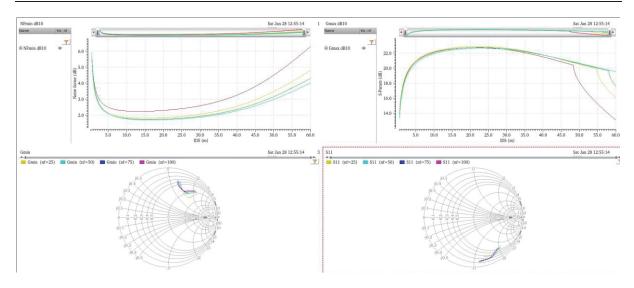

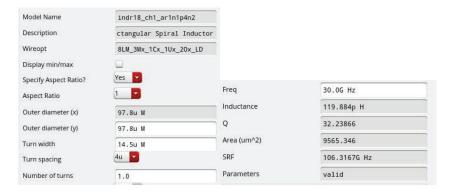

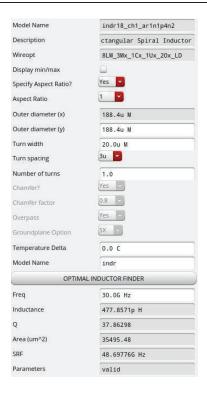

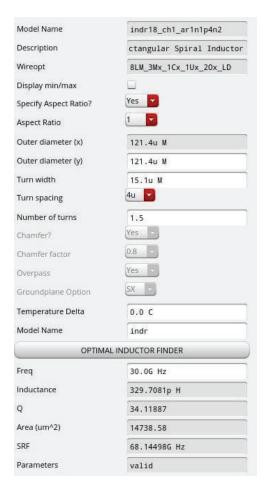

| Figura 38. Valores de inductancia y dimensiones de L <sub>source</sub>                        | -6 |

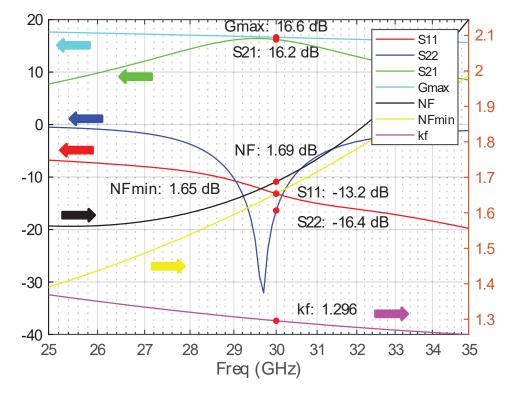

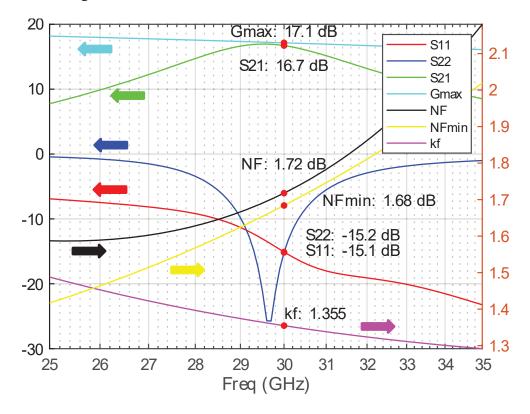

| Figura 39. Resultados tras añadir $L_{source}$ desde el PDK                                   | -6 |

| Figura 40. Valores de inductancia y dimensiones de L <sub>drain</sub>                         | .7 |

| Figura 41. Resultados del esquemático con componentes del PDK tras añadir $L_{drain}$         | .7 |

| Figura 42. Valores de inductancia y dimensiones de L <sub>gate</sub>                          | -8 |

| Figura 43. Resultados del esquemático con componentes del PDK tras añadir $L_{\text{gate}}$   | .9 |

| Figura 44. Valores de capacitancia y dimensiones de C <sub>out</sub>                          | .9 |

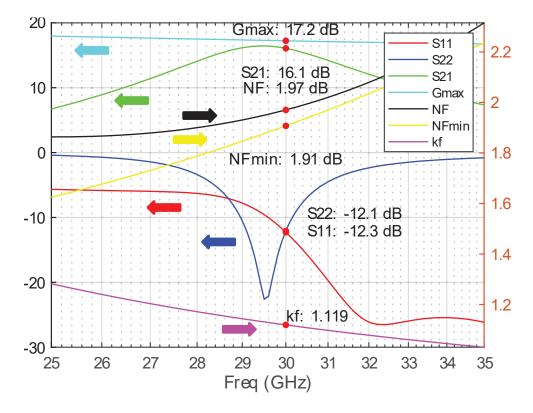

| Figura 45. Resultados del esquemático con los componentes del PDK tras añadir Cout 5          | 0  |

| Figura 46. Valores de capacitancia y dimensiones de los condensadores de Bypass 5             | 0  |

| Figura 47. Resultados del esquemático con componentes del PDK tras añadir los condensadores   | es |

| de Bypass                                                                                     | 1  |

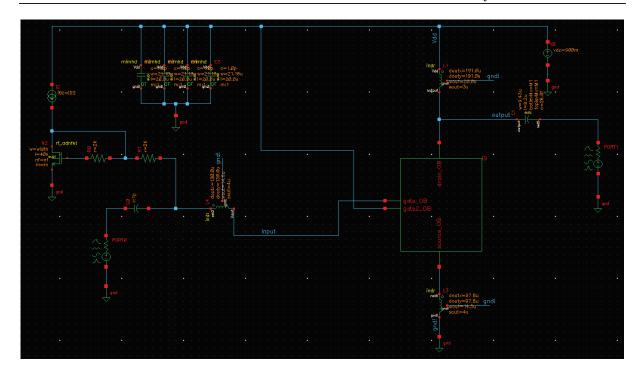

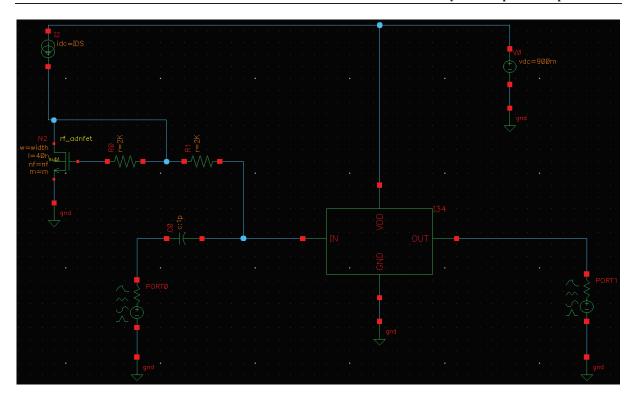

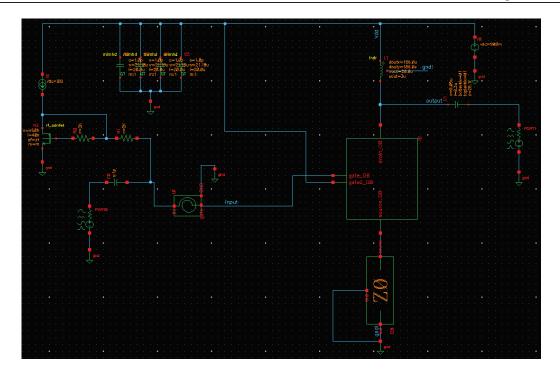

| Figura 48. Esquemático del diseño con componentes del PDK.                                    | 1  |

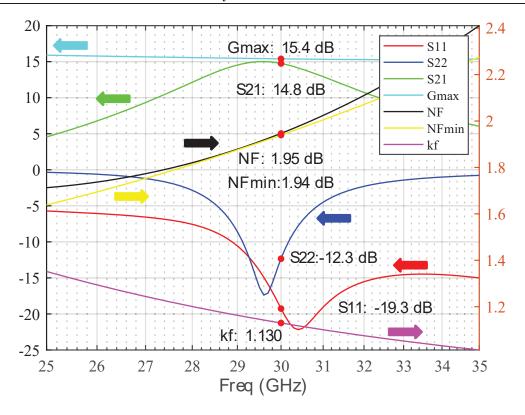

| Figura 49. Resultados finales obtenidos con el diseño con componentes del PDK 5               | 2  |

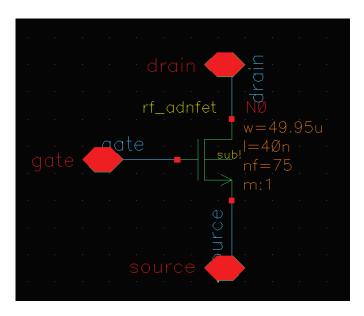

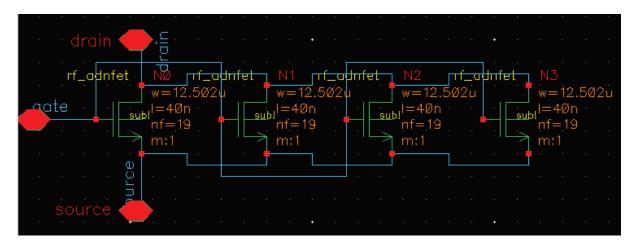

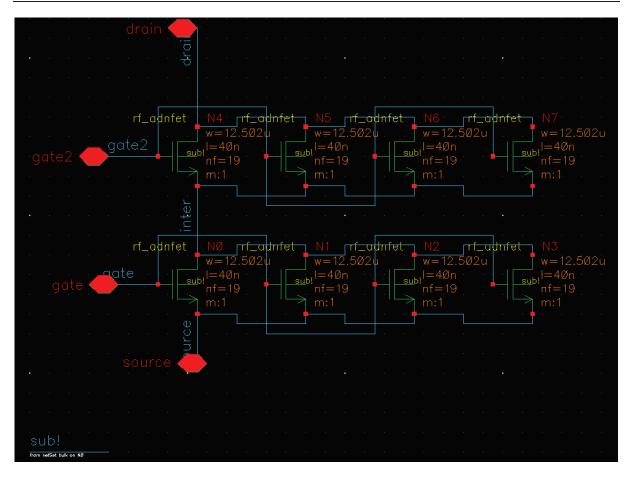

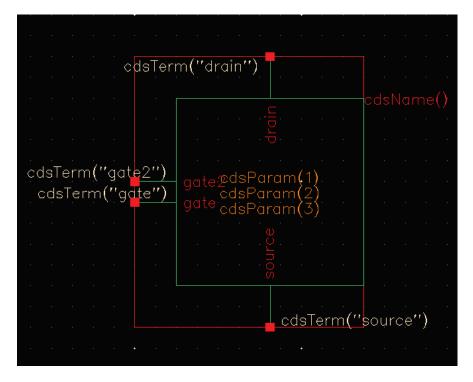

| Figura 50. Esquemático del transistor con los pines y las dimensiones                         | 8  |

| Figura 51. Incorporación del transistor al layout.                                            | 9  |

| Figura 52. Esquemático con los cuatro transistores para reducir el ancho del transistor 5     | 9  |

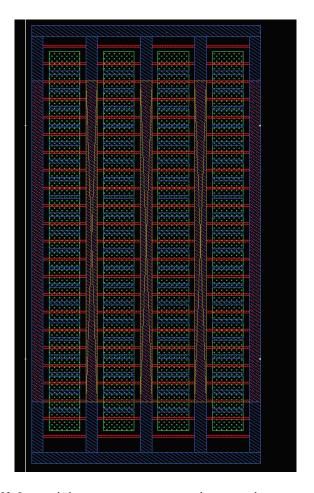

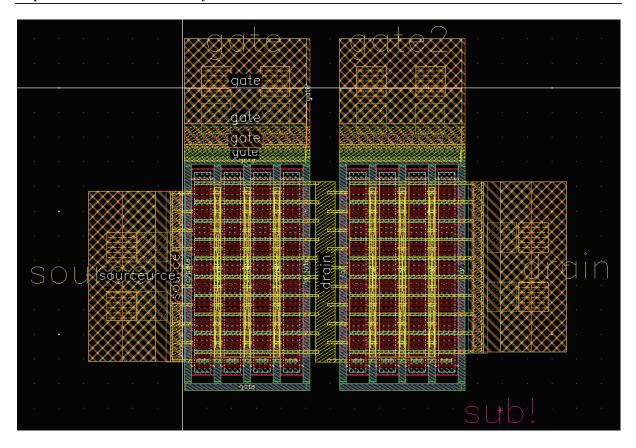

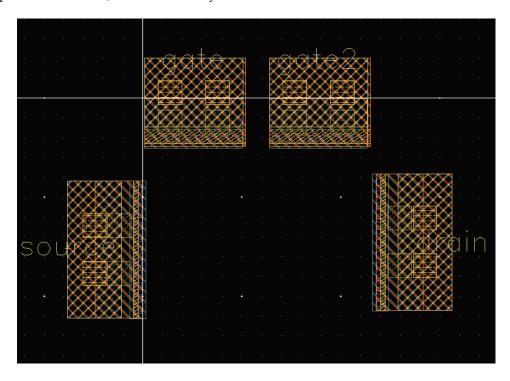

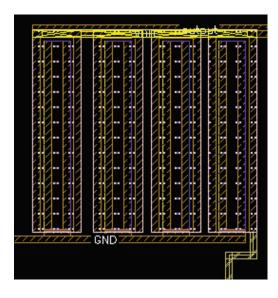

| Figura 53. Layout de los cuatro transistores con los terminales interconectados               | 0  |

| Figura 54. Implementación del layout del primer transistor completo con los terminales 6      | 1  |

| Figura 55. Implementación final del primer transistor con los terminales en la capa LD para s | ίu |

| conexión con otros componentes                                                                | 2  |

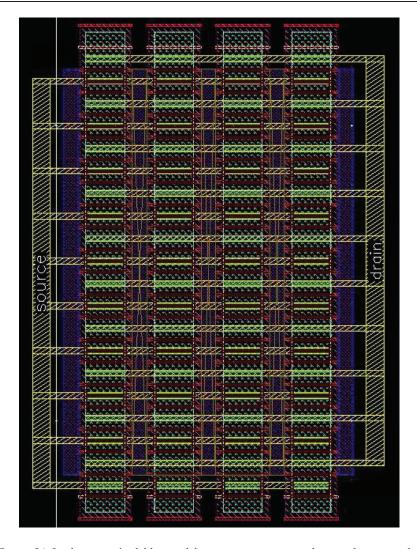

| Figura 56. Esquemático para implementar el cascodo, dividiendo los transistores para reduc    | iı |

| el ancho total                                                                                | 3  |

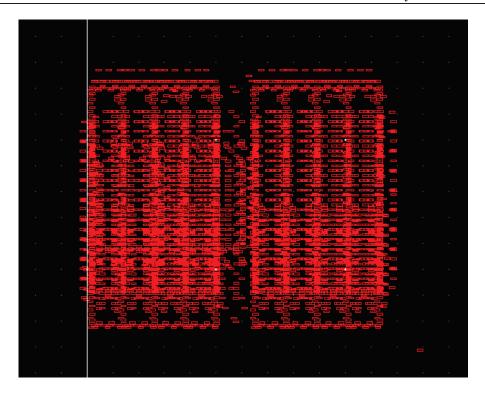

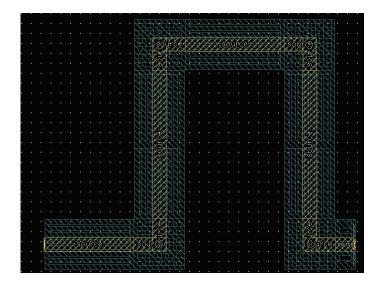

| Figura 57. Implementación del layout del cascodo hasta el nivel LD                            | 4  |

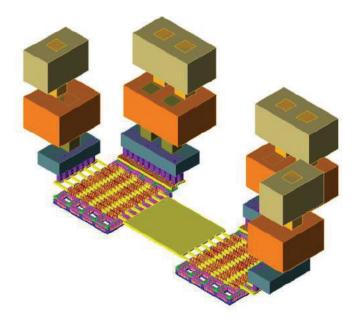

| Figura 58. Modelo en 3D del cascodo donde se observan los distintos niveles de metal y las   |

|----------------------------------------------------------------------------------------------|

| vías64                                                                                       |

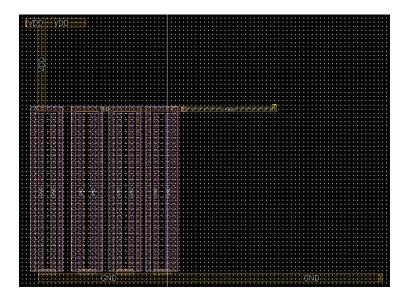

| Figura 59. Elementos del cascodo sometidos a la simulación EMX                               |

| Figura 60. Elementos del cascodo sometidos a la extracción de capacidades parásitas66        |

| Figura 61. Resultados de la extracción de parásitas del modelo RCC                           |

| Figura 62. Creación del símbolo que contiene los resultados de la extracción de capacidades  |

| parásitas67                                                                                  |

| Figura 63. Sección vertical de la tecnología que indica las capas empleadas en el diseño del |

| cascodo                                                                                      |

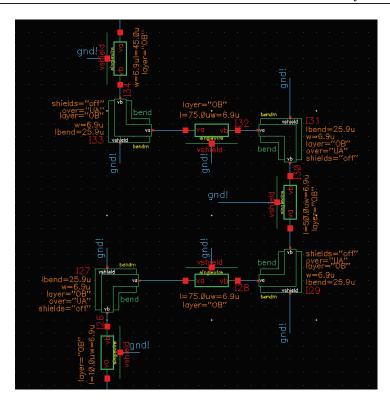

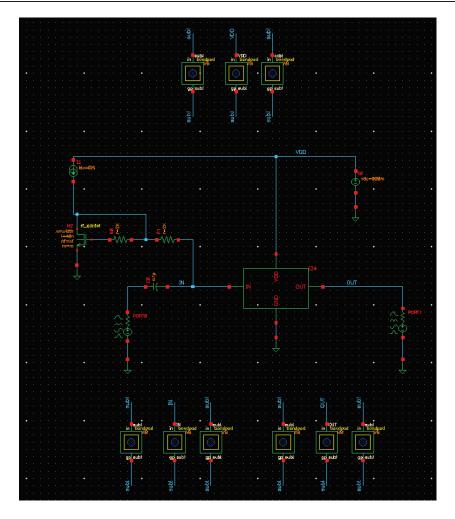

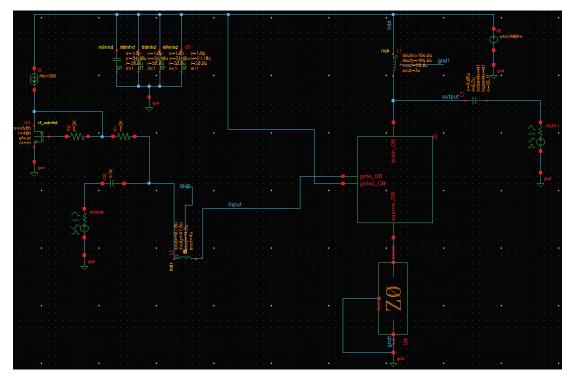

| Figura 64. Esquemático que contiene el símbolo con el modelo del cascodo para realizar       |

| simulaciones                                                                                 |

| Figura 65. Resultados de la simulación con las vistas de esquemático seleccionadas en el     |

| fichero de tipo config69                                                                     |

| Figura 66. Resultados de la simulación del LNA con la vista "Schematic N-Port" del modelo    |

| EM                                                                                           |

| Figura 67. Resultados finales del esquemático con las vistas de las simulaciones EM y RCC.   |

| 71                                                                                           |

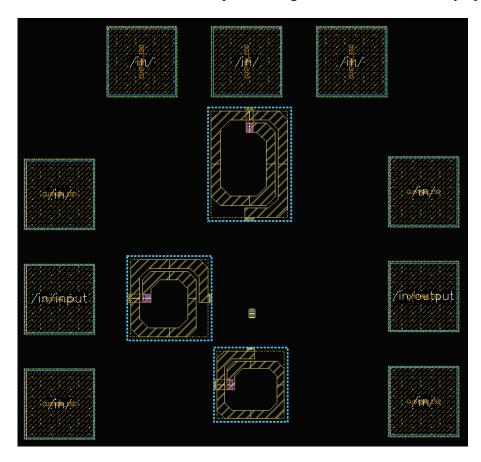

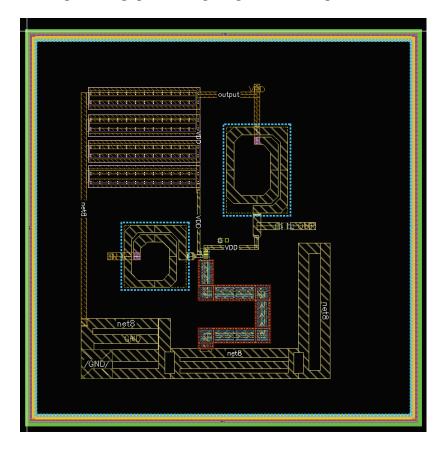

| Figura 68. Floor plan del layout del LNA.                                                    |

| Figura 69. Layout con la topología a seguir en el presente TFM [20]73                        |

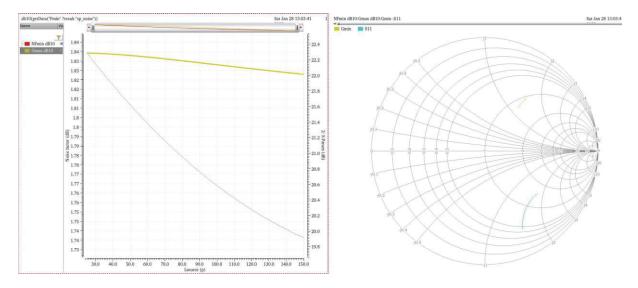

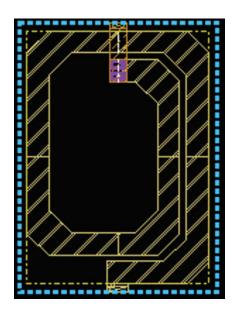

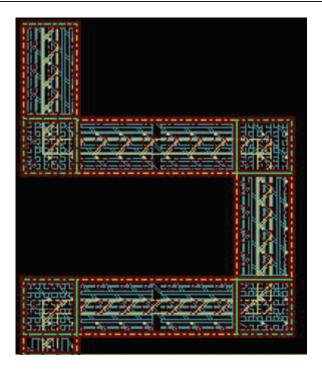

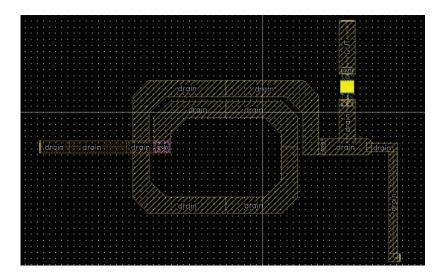

| Figura 70. Diseño a nivel de layout de L <sub>drain</sub>                                    |

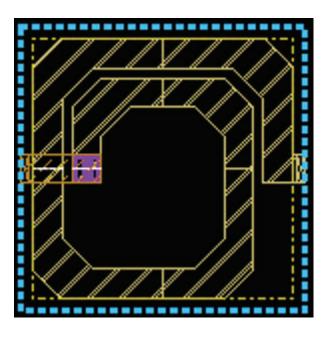

| Figura 71. Diseño a nivel de layout de L <sub>gate</sub>                                     |

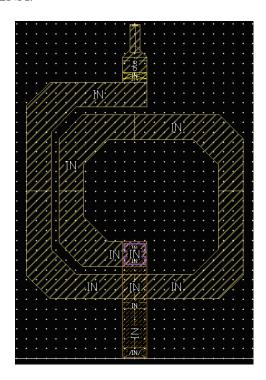

| Figura 72. Diseño a nivel de layout de L <sub>source</sub>                                   |

| Figura 73. Líneas de transmisión para implementar L <sub>source</sub>                        |

| Figura 74. Diseño a nivel de layout de las líneas de transmisión                             |

| Figura 75. Esquemático con las líneas de transmisión para realizar simulaciones              |

| Figura 76. Resultados de la simulación antes de incluir las líneas de transmisión79          |

| Figura 77. Resultados de la simulación tras incluir las líneas de transmisión                |

| Figura 78. Diseño a nivel de layout de los condensadores de grounding                        |

| Figura 79. Diseño a nivel de layout de C <sub>out</sub>                                      |

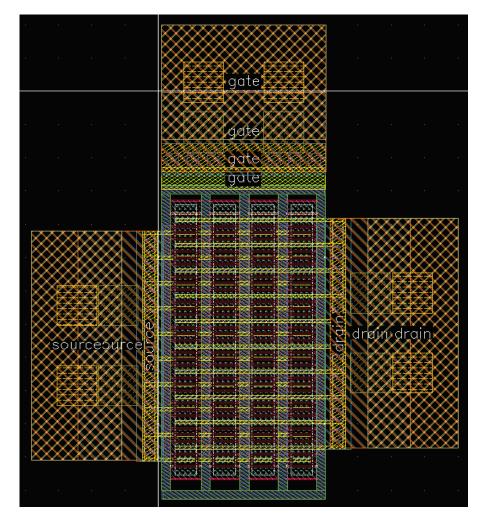

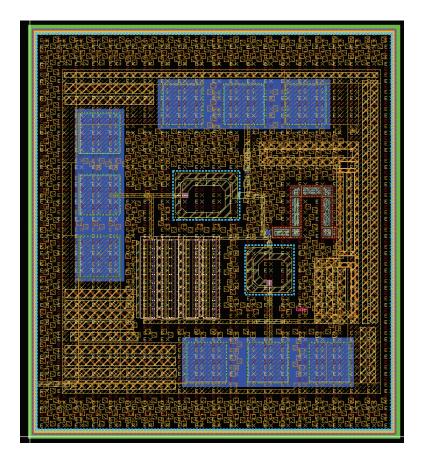

| Figura 80. Layout completo sin pads y con el guardring                                       |

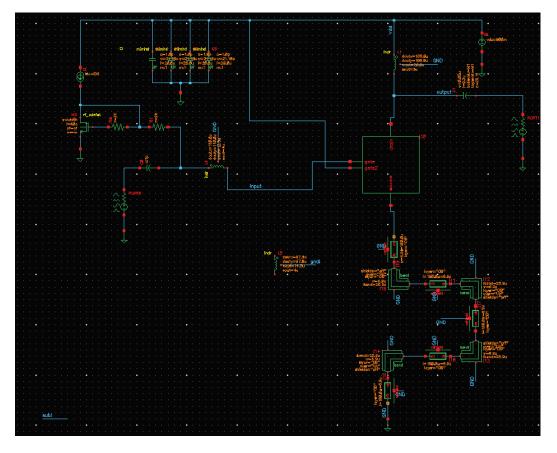

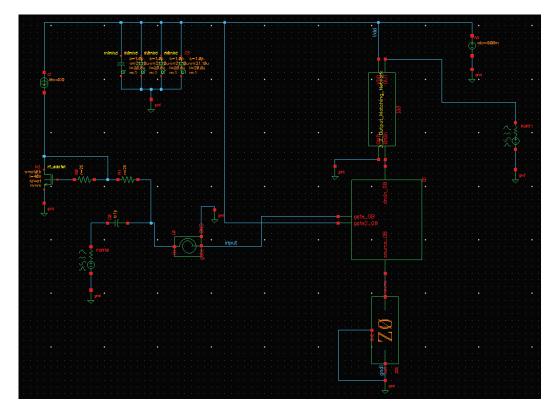

| Figura 81. Esquemático con el símbolo del LNA completo.                                      |

| Figura 82. Esquemático con los pads añadidos y configurados en función del tipo de punta. 84 |

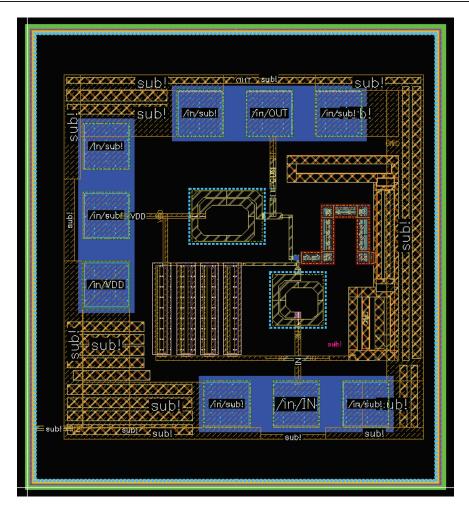

| Figura 83. Layout con los pads añadidos y los planos de masa en LD, OB y OA85                |

| Figura 84. Layout final con los fillers como paso previo al envío a fabricación              |

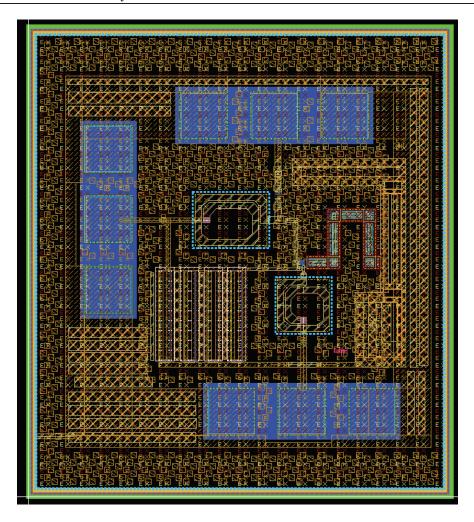

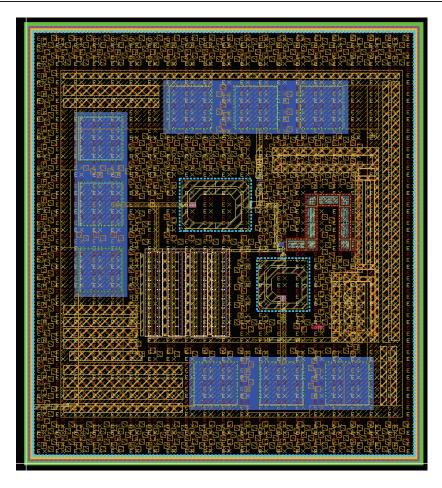

| Figura 85. Diseño a nivel de layout completo                                                 |

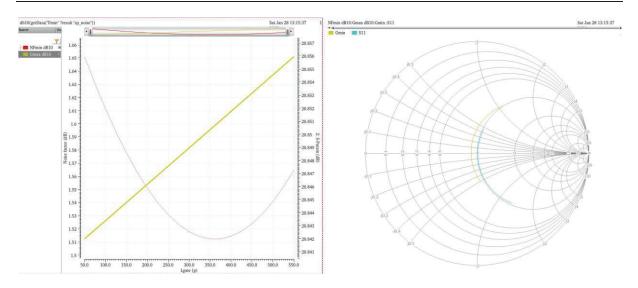

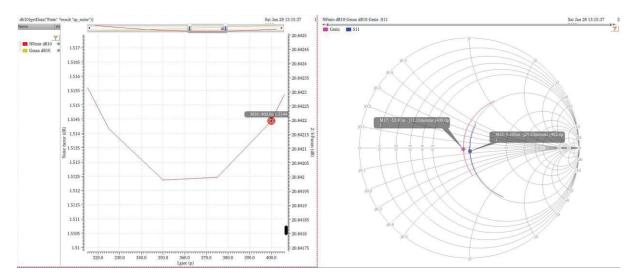

| Figura 86. Adaptación de entrada del LNA a nivel de layout                                   |

| Figura 87. Adaptación de salida del LNA a nivel de layout                                       |

|-------------------------------------------------------------------------------------------------|

| Figura 88. Degeneración de fuente del LNA a nivel de layout                                     |

| Figura 89. Red de puerta del cascodo del LNA a nivel de layout                                  |

| Figura 90. Esquemático con el modelo del cascodo para realizar las simulaciones con el modelo   |

| EM de la degeneración de fuente. 91                                                             |

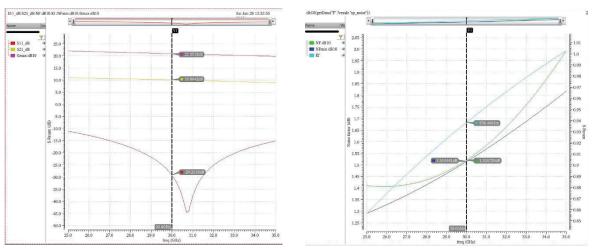

| Figura 91. Resultados de las simulaciones tras añadir el modelo EM de la degeneración de        |

| fuente. 92                                                                                      |

| Figura 92. Esquemático con el modelo del cascodo para realizar las simulaciones con el modelo   |

| EM de la adaptación de entrada                                                                  |

| Figura 93. Resultados de las simulaciones tras añadir el modelo EM de la adaptación de entrada. |

| 94                                                                                              |

| Figura 94. Esquemático con el modelo del cascodo para las simulaciones con el modelo EM de      |

| la adaptación de salida                                                                         |

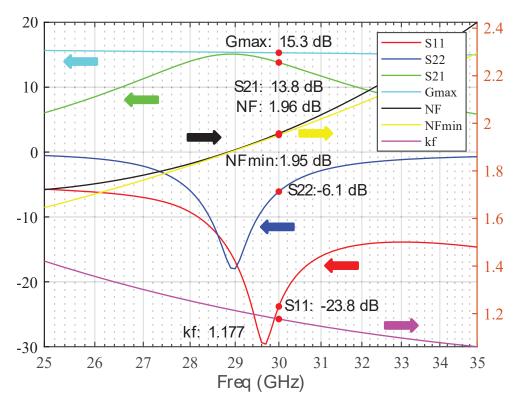

| Figura 95. Resultados de las simulaciones tras añadir el modelo EM de la adaptación de salida.  |

| 95                                                                                              |

| Figura 96. Resultados del análisis de Monte Carlo del parámetro S <sub>11</sub>                 |

| Figura 97. Resultados del análisis de Monte Carlo del parámetro S <sub>22</sub>                 |

| Figura 98. Resultados del análisis de Monte Carlo del parámetro S <sub>21</sub>                 |

| Figura 99. Resultados del análisis de Monte Carlo del parámetro NF                              |

| Figura 100. Estadísticas de los parámetros analizados con Monte Carlo                           |

| Figura 101. Recopilación del diseño completo del LNA a nivel de layout con los pads y los       |

| fillers incluidos.                                                                              |

# Índice de tablas

| Tabla 1. Comparación de aspectos técnicos entre 4G vs 5G                              | 5        |

|---------------------------------------------------------------------------------------|----------|

| Tabla 2. Comparación de los resultados de ambos LNAs                                  | 16       |

| Tabla 3. Resumen de las prestaciones del LNA estudiado                                | 17       |

| Tabla 4. Resultados de las diferentes implementaciones en función de la topología     | 23       |

| Tabla 5. Posibles valores de los parámetros de los condensadores MIM                  | 28       |

| Tabla 6. Posibles valores de los parámetros de la bobina INDR                         | 31       |

| Tabla 7. Comparación de los resultados del diseño con componentes ideales frente al   | l diseño |

| con componentes de la tecnología                                                      | 53       |

| Tabla 8. Siglas, nomenclaturas y códigos de colores de los niveles de diseño de 45RFS | OI [27]  |

|                                                                                       | 57       |

| Tabla 9. Resultados de los parámetros del LNA con el modelado del cascodo             | 71       |

| Tabla 10. Parámetros de la bobina L <sub>drain</sub>                                  | 74       |

| Tabla 11. Parámetros de la bobina L <sub>gate</sub>                                   | 75       |

| Tabla 12. Medidas de las líneas de transmisión empleadas                              | 77       |

| Tabla 13. Valores de los condensadores de grounding                                   | 80       |

| Tabla 14. Valores de los parámetros de Cout                                           | 81       |

| Tabla 15. Principales valores de los componentes del diseño a nivel de layout         | 87       |

| Tabla 16. Resumen de las prestaciones del diseño del análisis de Monte Carlo          | 98       |

| Tabla 17 Reconilación de los resultados de los diseños en las distintas fases         | 101      |

### Acrónimos

**3GPP** Third Generation Partnership Project

**5G** Fifth Generation

**ADC** Analogic/Digital Converter

**BJT** Bipolar Junction Transistor

**CG** *Common-Gate*

**CMOS** *Complementary Metal-Oxide-Semiconductor*

**CS** Common-Source

**DRC** Design Rule Checking

**EM** Electromagnética

eMBB enhanced Mobile BroadBand

**EMX** *ElectroMagnetic eXtraction*

E/S Entrada/Salida

**FBB** Forward Body Bias

**FDSOI** Fully Depleted Silicon-On-Insulator

**FWA** Fixed Wireless Access

**GSG** Ground-Signal-Ground

**IEEE** Institute of Electrical and Electronics Engineers

**IoT** Internet of Things

**IP3** Punto de Intercepción de tercer orden

ITU International Telecommunications Union

K Kurz

**Ka** *K-above*

**Ku** *K-under*

**LMDS** Local Multipoint Distribution Service

**LNA** Low Noise Amplifier

LTE Long Term Evolution

LVS Layout Versus Schematic

Acrónimos

MAG Maximum Available Gain

M2M *Machine-to-Machine*

MIM Metal-Insulator-Metal

MIMHD MIM High Density

MIMHQ MIM High Quality

MIMO Multiple Input-Multiple Output

**mMTC** Masive Machine Type Communications

**MOM** *Metal-Oxide-Metal*

MSG Maximum Stable Gain

**NF** Noise Figure

NR New Radio

PDK Process Design Kit

**PEX** Parasitic Extraction

**S** Scattering

**SOI** Silicon On Insulator

**URLLC** *Ultra-Reliable and Low Latency Communications*

**VNCAP** Vertical Natural Capacitor

**VPP** Vertical Parallel Plate

**WB** Wire-Bonding

## Capítulo 1. Introducción

El transceptor es un elemento crucial en las comunicaciones inalámbricas, debido a que es el encargado de recibir y transmitir las señales. En estos sistemas de comunicaciones inalámbricas, los diseñadores de circuitos integrados deben satisfacer dos necesidades: la primera de ellas es reducir el coste de los productos, mientras que la segunda es reducir el consumo de los mismos. Por esta razón, en las últimas décadas ha crecido el interés en realizar diseños de transceptores que satisfagan el compromiso entre estos dos aspectos.

A la hora de realizar el diseño de un circuito integrado para comunicaciones inalámbricas, se debe tener en cuenta que estos consumen una gran parte de la potencia del dispositivo. De esta manera, los transceptores empleados para 5G (Fifth Generation) deben cumplir con esta especificación, es decir, se debe reducir el consumo de potencia de los dispositivos, puesto que un elevado porcentaje del consumo es debido a los transceptores. Cabe destacar que la quinta generación de tecnologías de telefonía móvil 5G es un campo que está en auge, y se espera que en los próximos años experimente un desarrollo transcendental. Una de las principales aplicaciones de 5G es el Internet de las Cosas (Internet of Things, IoT), donde se precisan infraestructuras que sean capaces de manejar elevados volúmenes de datos [1]. Por ejemplo, en una Smart City se concentra un elevado flujo de datos, como puede ser la información proveniente de redes de sensores, de coches de conducción autónoma, etc. Para procesar dicha información se necesitan elevadas tasas de datos, un gran ancho de banda y baja latencia, necesidades que pueden ser cubiertas gracias a la tecnología 5G. Otra posible aplicación son las comunicaciones máquina a máquina (Machine-to-Machine, M2M). Este tipo de comunicaciones permite la comunicación entre máquinas, enviando y recibiendo datos en ambos extremos. Se emplea en la industria en el mantenimiento automatizado de máquinas, en avisos de fin de proceso o en controles de stock, por ejemplo. La principal virtud de M2M es que habilita la posibilidad de que un número elevado de dispositivos puedan comunicarse entre ellos, pudiendo tomar decisiones sin necesidad de intervención humana, mejorando los tiempos de espera y reduciendo costes [2]. La tecnología 5G se postula como la mejor candidata para afrontar la nueva realidad, donde se espera una elevada cantidad de dispositivos interconectados, con una elevada tasa de datos, con un uso eficiente del espectro y baja latencia.

A lo largo de este capítulo se presenta una breve introducción al Trabajo Fin de Máster, donde se empieza analizando los antecedentes, se continúa explicando las tecnologías 5G y se finaliza exponiendo los objetivos del mismo y la estructura del presente documento.

#### 1. Antecedentes

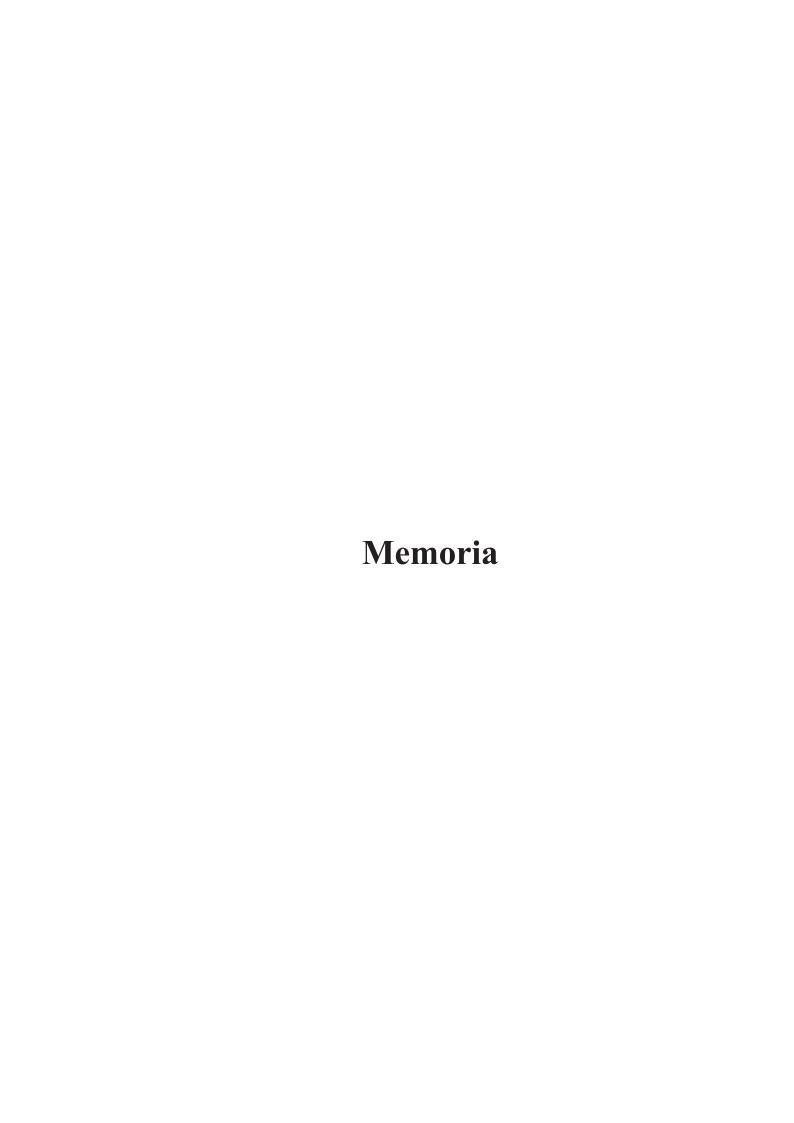

Para que un dispositivo se comunique con la estación base o con otros dispositivos, es fundamental la implementación de un sistema de comunicaciones inalámbricas. De dicha tarea se encarga un elemento denominado transceptor, el cual se divide en dos bloques fundamentales -uno de transmisión y otro de recepción- integrados en un mismo chip [3]. Cada bloque se subdivide en varios componentes que permiten aplicar un tratamiento determinado a la señal. En el caso del bloque de transmisión, es posible encontrar etapas de filtrado, mezcladores para elevar la frecuencia de la señal, amplificadores de potencia o conversores digitales/analógicos (Digital-to-Analog Converter, DAC), por ejemplo. Mientras, en el bloque de recepción se encuentra el amplificador de bajo ruido (Low Noise Amplifier, LNA), mezcladores para reducir la frecuencia de la señal, etapas de filtrado o conversores analógicos/digitales (Analogic-to-Digital Converter, ADC) como se muestra en la Figura 1. Nótese que también existe un elemento denominado oscilador local que genera la señal de mezcla para la conversión de frecuencias. Este elemento puede ser independiente para el transmisor y el receptor o puede emplearse de forma compartida, según la topología seleccionada. La función del transceptor es la conversión de frecuencias y maximizar la transferencia de potencia para asegurar que la transmisión y/o recepción de señales se realiza de forma adecuada agregando la mínima cantidad de pérdidas posible. En el transcurso de este procedimiento, la señal pasa por los bloques mencionados previamente, sufriendo cambios como amplificación, filtrado o la mezcla de la señal útil con un oscilador local para conseguir la modulación de la frecuencia.

Figura 1. Diagrama de bloques de un transceptor convencional.

El propósito principal del presente Trabajo Fin de Máster es realizar el diseño de uno de los bloques fundamentales del cabezal de recepción, concretamente el LNA. Este bloque es de vital importancia en el sistema porque es el primer elemento de la cadena. Una vez que la señal llega a la antena, se dirige al cabezal de recepción, encontrándose con el LNA. Este

elemento se encarga de realizar la adaptación de entrada de la señal, maximizando la transferencia de potencia, amplificando la señal e introduciendo la menor cantidad de ruido posible. Por lo tanto, se debe mantener un compromiso entre estos parámetros. Además, la figura de ruido (*Noise Figure*, NF) se debe minimizar, ya que ésta se suma directamente al total del ruido de la cadena de recepción, como bien indica la conocida fórmula de Friis. Del mismo modo, en la fórmula de Friis se indica que la ganancia del primer elemento tiene un peso notable en el cálculo de la NF<sub>total</sub>, consiguiendo atenuarla, por lo que es de especial interés maximizar la ganancia del LNA [4]. Por lo tanto, a la hora de realizar un diseño hay que tener en cuenta las prestaciones que el LNA debe ofrecer, al igual que otros aspectos como la topología del circuito, su consumo, la linealidad, la adaptación de impedancias o la estabilidad.

Para cumplir las restricciones de la aplicación a la que se destina el circuito, se debe seguir un flujo de diseño. Se parte de una fase de diseño sobre esquemático, donde se fijan unas especificaciones deseadas y se inicia el diseño a nivel circuital. En un inicio se emplean componentes ideales, pero una vez que se verifica el diseño inicial se sustituyen por los componentes de la tecnología. Tras realizar el esquemático del circuito, se simula y se comprueba que cumple con las restricciones iniciales. A partir de este punto, se realiza la descripción física del diseño, es decir, se determinan las máscaras del proceso de fabricación, dando lugar a la vista de *layout* del circuito. Una vez finalizado, se realizan verificaciones de cumplimiento de las reglas de diseño del proceso tecnológico seleccionado. Igualmente, se verifica que la vista de *layout* y de esquemático se corresponden. Una vez hecho esto, se extraen las parásitas del circuito, es decir, se obtienen parámetros como la capacidad, inductancia y resistencia de las interconexiones empleadas. El siguiente paso consiste en analizar el comportamiento del circuito y contrastar los resultados con las restricciones fijadas inicialmente. A continuación, se pasa a la fase de fabricación y por último, a la de medida, finalizando así el flujo de diseño del circuito [5] [6].

### 2. Tecnologías 5G

En la última década, el fuerte auge de las comunicaciones inalámbricas ha dado lugar a múltiples estándares de comunicación. A raíz de las comunicaciones inalámbricas, se definen nuevos estándares para aplicaciones determinadas como los servicios médicos o las *Smart Cities*. Por esta razón, los fabricantes y diseñadores adoptan técnicas de diseño específicas como la reducción del consumo de potencia de los dispositivos para mejorar su eficiencia. No obstante, el aumento del tráfico de datos, de dispositivos y la demanda de una mejor experiencia de usuario, precisa nuevas soluciones. Por esta razón, surge la tecnología 5G como

combinación de las tecnologías de comunicación inalámbricas predecesoras como son 2G, 3G, 4G o los estándares IEEE (*Institute of Electrical and Electronics Engineers*) 802.11 [7].

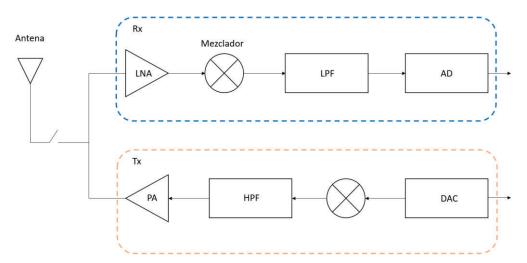

La compañía que se ha encargado de definir el estándar que rige la tecnología 5G es 3GPP (*Third Generation Partnership Project*), que es la organización internacional que define los estándares de comunicación móvil. Además, con la definición de 5G se marca el comienzo de la evolución del actual sistema LTE (*Long Term Evolution*). No obstante, la versión final de las redes móviles 5G se denomina NR (*New Radio*) que determina un sistema de redes independiente de los sistemas de redes actuales. Esta versión permite que 5G pueda actuar en tres escenarios fundamentales o lo que se define como "Pirámide 5G": banda ancha móvil mejorada (*enhanced Mobile BroadBand*, eMBB), las comunicaciones ultra-fiables y de baja latencia (*Ultra-Realiable and Low Latency Communications*, URLLC) y las comunicaciones masivas entre dispositivos (*Masive Machine Type Communications*, mMTC) [8]. Por lo tanto, gracias a estos pilares de 5G se pueden satisfacer múltiples necesidades como se muestra en la Figura 2, manifestando la importancia de este estándar en el futuro.

Figura 2. Aplicaciones de la pirámide 5G.

La tecnología 5G destaca por las prestaciones que ofrece, mejorando notablemente las de su predecesor 4G, como se puede ver en la Tabla 1. Se observa cómo se reduce la latencia a valores inferiores a 1 ms, con una tasa de datos máxima de 20 Gbps. Además, soporta un volumen de conexiones de más de un millón por km² [9]. Este tipo de tecnología se centra en poder gestionar una gran cantidad de usuarios, por lo que es crucial optimizar el espectro electromagnético. Para ello se emplean antenas MIMO (*Multiple Input–Multiple Output*) debido a que permiten a los dispositivos trabajar en distintas frecuencias de forma simultánea, optimizando la comunicación y las velocidades de transmisión y recepción de información [10]. Tal y como se muestra en la Tabla 1, esta tecnología usa dos bandas de frecuencias, una por

debajo de 6 GHz y otra por encima en la zona de ondas milimétricas. La banda de frecuencias por debajo de 6 GHz está compuesta a su vez por dos sub-bandas. En primer lugar, la banda baja corresponde a frecuencias UHF inferiores a 1 GHz, las cuales son adecuadas para comunicaciones de largo alcance y de alta velocidad de datos y para comunicaciones de baja velocidad y de ancho de banda de canal estrecho necesarias para aplicaciones de IoT y mMTC. Por otro lado, se distingue la banda media que va de 1 a 6 GHz para dar servicios de banda ancha avanzados eMBB donde se necesitan al menos 100 MHz de ancho de banda de canal. Por encima de 6 GHz se encuentra la banda alta, situada en torno a 30 GHz en ondas milimétricas. Esta banda es ideal para dar acceso inalámbrico fijo (Fixed Wireless Access, FWA) y para la densificación de servicios de banda ancha avanzados en zonas específicas como el centro de las ciudades o estadios de futbol. Además, se definen las bandas nº 257 (LMDS, Local Multipoint Distribution Service) y nº 258 (Banda K) que operan cerca de 28 GHz, las cuales están próximas a la frecuencia de trabajo elegida. Si bien existen numerosos trabajos que abordan el diseño de circuitos de comunicaciones para las bandas situadas por debajo de 6 GHz, son escasos los realizados para la banda de 30 GHz. Esta es la principal razón por la que en este Trabajo Fin de Máster se plantea el diseño de un LNA para receptores 5G a una frecuencia de trabajo de 30 GHz.

Tabla 1. Comparación de aspectos técnicos entre 4G vs 5G

| Parámetro                    | 4G                                   | 5G                                  |  |

|------------------------------|--------------------------------------|-------------------------------------|--|

| Latencia                     | 10 ms                                | Menos de 1 ms                       |  |

| Tasa de datos máxima         | 1 Gbps                               | 20 Gbps                             |  |

| Número de conexiones móviles | 100.000 usuarios por km <sup>2</sup> | Más de 1 millón por km <sup>2</sup> |  |

| Ancho de banda del canal     | 20 MHz                               | 100 MHz por debajo de 6 GHz         |  |

|                              | 20 MHZ                               | 400 MHz por encima de 6 GHz         |  |

|                              |                                      | 600 MHz a 6 GHz                     |  |

| Banda de frecuencia          | 600 MHz a 6 GHz                      | Ondas milimétricas (28 GHz, 39      |  |

|                              |                                      | GHz, +80 GHz)                       |  |

A la hora de desplegar las redes 5G, es determinante definir la banda empleada. Para ello hay que hacer referencia al término de microondas, que engloba todas aquellas señales cuya frecuencia se sitúa entre 300 MHz y 300 GHz, con un rango de longitud de onda entre 1 m y 1 mm. A pesar de que realizar diseños de circuitos que trabajen en este rango de frecuencias es complejo debido a las características de propagación de las microondas, presentan grandes ventajas que pueden ser empleadas en los circuitos. Por ejemplo, dado que a mayor frecuencia menor es la longitud de onda correspondiente, los elementos pasivos requeridos en circuitos de alta frecuencia presentan menor tamaño que los de frecuencias más reducidas. Considerando las bandas de frecuencias definidas por la ITU (*International Telecommunicatios Union*) en conjunto con IEEE, la banda de frecuencias elegida para realizar el diseño de un LNA para un

receptor 5G es la banda K/Ka [11]. La banda K (*Kurz*) abarca un rango de frecuencias de 18 GHz a 27 GHz y posee dos bandas contiguas, una por encima y otra por debajo: la banda Ka y la Ku. La banda Ka (*K-above*) comprende el rango de 27 GHz a 40 GHz, mientras que la banda Ku (*K-under band*) dispone del rango de 12 GHz a 18 GHz [12].

En la mayoría de los diseños de circuitos integrados actuales se emplean estructuras de materiales semiconductores como silicio, galio o germanio, entre otros. Este tipo de circuitos se clasifica en función del nivel de integración de componentes, desde una cantidad de diez transistores a cifras superiores al millón. Presentan ventajas como una elevada eficiencia energética, reducido tamaño o un coste de fabricación inferior debido a que en una misma oblea se pueden litografíar múltiples chips. A pesar de estas ventajas, los circuitos integrados presentan ciertas limitaciones como la disipación de potencia o las capacidades parásitas. Una posible solución para estos inconvenientes se encuentra en usar la tecnología CMOS (Complementary Metal-Oxide-Semiconductor). El funcionamiento de esta tecnología se basa en la utilización complementaria de un transistor nMOS y un pMOS. De esta manera, se consigue una reducción en el consumo de potencia, una mejora significativa en la frecuencia de funcionamiento y la reducción de costes de fabricación, dando lugar a que esta tecnología sea la favorita en el diseño de circuitos integrados.

En la integración de chips, se eligen familias lógicas como CMOS para su implementación, pero a su vez, se tienen en cuenta tecnologías de fabricación determinadas que permitan obtener una mejora de las prestaciones. Este es el caso de SOI (*Silicon On Insulator*), donde se sustituye el sustrato tradicional por un conjunto de capas de semiconductor, aislante y semiconductor. Este tipo de tecnología mejora las prestaciones a nivel de conseguir altas frecuencias de funcionamiento, reducción de la disipación de potencia y mejora en la capacidad de escalabilidad en aplicaciones como el despliegue de estaciones base 5G, comunicaciones inalámbricas, radares, etc. Por este motivo, en el presente Trabajo Fin de Máster se emplea la tecnología 45RFSOI, que destaca principalmente por una longitud de puerta mínima de 45 nm, con opciones de un total de siete a once capas de metales como cobre o aluminio y por las opciones de elementos pasivos que ofrece para circuitos de RF con condensadores MIM y bobinas con un elevado factor de calidad (Q).

### 3. Objetivos

El objetivo principal de este Trabajo Fin de Máster es realizar un diseño a nivel de *layout* para un amplificador de bajo ruido que opere en la banda K/Ka para receptores 5G. Para llevar a cabo dicho diseño se emplea la tecnología 45RFSOI de GlobalFoundries. Además, se plantean los siguientes objetivos complementarios:

- O1. Realizar el diseño de un LNA para receptores 5G a una frecuencia de trabajo de 30 GHz.

- O2. Realizar un layout full-custom de un LNA para un receptor 5G en 45RFSOI.

- **O3.** Analizar las simulaciones *post-layout* para realizar la optimización del diseño y comprobar su correcto funcionamiento.

#### 4. Estructura del documento

La estructura del documento está compuesta por siete capítulos, en los cuales se discuten los siguientes contenidos:

- Capítulo 1. En este capítulo se presenta una breve introducción de los aspectos determinantes del proyecto. Se indican los antecedentes de este trabajo se introducen las tecnologías 5G y se desglosan los objetivos a cumplir con este Trabajo Fin de Máster.

- Capítulo 2. El contenido de este capítulo constituye el estado del arte sobre el que se basa el proyecto. Se explica la teoría básica de los LNAs y se ejemplifican algunos diseños de LNA para 5G.

- Capítulo 3. En el tercer capítulo se realiza un estudio de la tecnología empleada,

45RFSOI de GlobalFoundries. Se muestran los diferentes componentes pasivos y activos de la tecnología y se comentan las restricciones del proceso de fabricación.

- Capítulo 4. Se discute el diseño a nivel esquemático del circuito. Se expone el cascodo

como topología elegida para el circuito, se detalla el diseño empleando en un inicio

componentes ideales y luego componentes del PDK (*Process Design Kit*). Finalmente,

se comentan los resultados obtenidos.

- Capítulo 5. En el quinto capítulo se muestra el diseño a nivel de *layout*. Se explica el procedimiento seguido para obtener el *layout* de los transistores, de las bobinas y del circuito completo con y sin *pads*.

- Capítulo 6. En este capítulo se presentan las simulaciones tras realizar el *layout*, donde se muestra el LNA con la extracción de componentes parásitos, con la extracción del modelo electromagnético de los pasivos y el análisis de Monte Carlo para estudiar las variaciones del circuito en diferentes ensayos del proceso de fabricación.

- Capítulo 7. En el último capítulo este documento se presenta un resumen del trabajo realizado, destacando los resultados y las conclusiones obtenidas y las líneas de trabajo futuro.

### Capítulo 2. Estado del Arte

El papel de los amplificadores de bajo ruido es fundamental en los sistemas de recepción de comunicaciones inalámbricas, ya que afecta en gran medida a la figura de ruido total del receptor y, por lo tanto, es crítico en los receptores 5G. Este elemento puede ser implementado basándose en distintas topologías que permiten optimizar unas determinadas prestaciones, ya sea nivel de ganancia, figura de ruido, linealidad, consumo, ancho de banda, etc. Por este motivo, en el presente capítulo se explica la teoría básica de los LNAs, analizando los parámetros S (de dispersión o *Scattering*), la carta de Smith, y los conceptos de ganancia, figura de ruido, estabilidad y linealidad. A su vez, se presenta una discusión sobre los diferentes LNAs para receptores 5G que el lector puede encontrar en la bibliografía científica.

#### 1. Teoría Básica de los LNAs

Los LNAs son los primeros elementos en la cadena de recepción de un transceptor y su función principal es adaptar la señal procedente de la antena, amplificarla e introducir la menor cantidad de ruido posible para que las etapas siguientes puedan procesar de una manera eficaz la señal. Por este motivo, existen ciertos parámetros como la ganancia o la figura de ruido que caracterizan a un LNA que se estudian en este capítulo.

#### I. Parámetros S y Carta de Smith

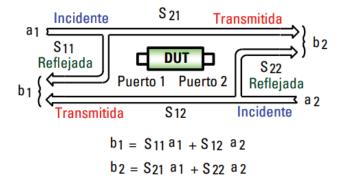

Para cuantificar algunos aspectos como la ganancia o el aislamiento de un LNA se emplean los parámetros S, o de dispersión, que son los coeficientes de reflexión y transmisión entre la onda incidente y reflejada. Estos elementos describen el comportamiento de un sistema lineal y representan la potencia transferida entre los distintos puertos de un circuito. En el caso de los circuitos de radiofrecuencia se debe especificar la impedancia característica del sistema y la frecuencia de trabajo. En la Figura 3 se muestra un cuadripolo con los puertos del sistema, que se emplean para calcular los coeficientes asociados a los parámetros S, donde se destacan las siguientes equivalencias:

- S<sub>11</sub>: Coeficiente de reflexión a la entrada (Pérdidas de retorno de entrada o *Input Return Loss*).

- O S<sub>12</sub>: Coeficiente de transmisión (Aislamiento entrada/salida o *Isolation*).

- o S<sub>21</sub>: Coeficiente de transmisión directa (Ganancia o *Gain*).

- S<sub>22</sub>: Coeficiente de reflexión a la salida (Pérdidas de retorno de salida o *Output Return Loss*).

Figura 3. Cuadripolo con las ondas incidentes y reflejadas en cada puerto y los parámetros S [13].

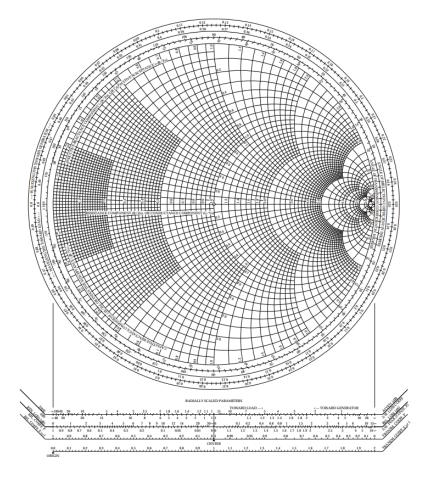

Para representar los parámetros de reflexión se suele utilizar la carta de Smith. Esta herramienta es un nomograma que muestra la variación de la impedancia compleja a lo largo de una línea de transmisión. La carta de Smith, ilustrada en la Figura 4, se emplea en este Trabajo Fin de Máster para realizar la adaptación del parámetro  $S_{11}$  a una impedancia de  $50~\Omega$ , localizada en el centro de la carta. La adaptación se realiza de este modo para conseguir que la transferencia de potencia de la señal proveniente de la antena hacia el LNA sea máxima.

Figura 4. Ejemplo de una Carta Smith [13].

#### II. Figura de ruido

Uno de los factores determinantes de un LNA es la figura de ruido. Este parámetro se mide en dB e indica la cantidad de ruido agregada por el amplificador a la señal de entrada. Asimismo, cuando esta medida se expresa de forma lineal se denomina factor de ruido. Este factor establece la relación entre la potencia del ruido disponible a la entrada y la potencia de ruido en la salida, referida a los diferentes tipos de ruido como el ruido térmico o el ruido *Flicker*. En términos generales, un LNA suele agregar una figura de ruido de 2 o 3 dB dependiendo de la aplicación, la frecuencia y del proceso tecnológico en el que se implemente. Para estudiar el ruido dentro de un sistema se emplea la Fórmula de Friis (1), que determina el factor de ruido total de las etapas en serie del sistema. Por lo tanto, como el LNA es el primer elemento de la cadena de recepción, su ruido se agrega de forma íntegra al total del factor de ruido del sistema [14].

$$F_{total} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{G_1 G_2 \dots G_{n-1}}$$

(1)

#### III. Estabilidad

Un amplificador puede generar una elevada cantidad de potencia, siendo posible la generación de oscilaciones. Dichas oscilaciones aparecen debido a las capacidades internas existentes entre drenador-puerta, fuente-puerta, etc., puesto que son vías de alimentación resonantes a una frecuencia determinada. Por lo tanto, se debe prestar atención a la hora de realizar el diseño debido a que en ocasiones la señal se filtra, realimentándose de forma positiva y creando oscilaciones. Para detectar esas filtraciones, se emplea el factor de estabilidad k de Rollet, definido en la ecuación (2). El parámetro  $\Delta$  se define según la ecuación (3), debiéndose cumplir que k > 1 y  $\Delta < 1$  para todas las frecuencias para que el sistema sea incondicionalmente estable [14]. Además, se debe analizar si se presentan irregularidades en los parámetros S, como picos o valles en la ganancia o en la figura de ruido.

$$k = \frac{1 + |\Delta|^2 - |S_{11}|^2 - |S_{22}|^2}{2 * |S_{21}|^2 * |S_{12}|^2}$$

(2)

$$\Delta = S_{11}S_{22} - S_{12}S_{21} \tag{3}$$

#### IV. Ganancia

La ganancia en potencia de un circuito viene dada por la relación entre la potencia de entrada y la potencia de salida del mismo, y se identifica con el parámetro S<sub>21</sub>. Siguiendo la Fórmula de Friis, la ganancia debe ser lo suficientemente grande como para minimizar la contribución de ruido que aportan el resto de los elementos de la cadena de recepción. El diseñador de circuitos integrados de RF debe mantener un compromiso entre la ganancia, la figura de ruido, el consumo y la linealidad del circuito. En general, se diferencian dos tipos de ganancia de un amplificador. Por un lado, se distingue la Ganancia Máxima Disponible (*Maximum Available Gain*, MAG) definida en la ecuación (4), que es la ganancia máxima que es capaz de ofrecer el amplificador independientemente de si es estable o no, donde k pertenece al factor de estabilidad.

$$MAG = G_{max} = \left| \frac{S_{21}}{S_{12}} \right| \left( k - \sqrt{k^2 - 1} \right)$$

(4)

Por otro lado, la Ganancia Máxima Estable (*Maximum Stable Gain*, MSG) indica la ganancia máxima que es capaz de ofrecer el LNA sin volverse inestable. La MSG es la relación entre la ganancia y el aislamiento del sistema, definido por los parámetros S como se indica en la ecuación (5) [15]. Dicho de otra forma, la MSG es la MAG cuando k=1.

$$MSG = \left| \frac{S_{21}}{S_{12}} \right| \tag{5}$$

#### V. Linealidad

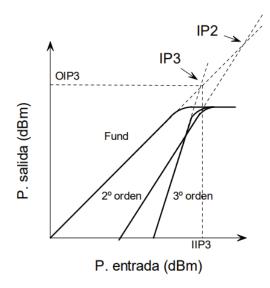

La linealidad de un dispositivo viene determinada por la capacidad de un determinado bloque de manejar señales con un nivel de potencia elevado sin introducir distorsión a la salida. Se puede determinar introduciendo una señal pura a una frecuencia determinada y observando para qué nivel de potencia la ganancia cae 1 dB respecto a la ganancia deseada. Este test determina el punto de compresión a 1 dB (PoldB). También se puede medir introduciendo dos tonos a distinta frecuencia y observando en la salida si se producen productos de intermodulación para un determinado nivel de potencia de entrada. Esta última prueba es la más empleada en el ámbito de las comunicaciones inalámbricas, la linealidad de un circuito se expresa con el punto de intercepción de tercer orden (IP3). Este punto corresponde a la intersección de las rectas de potencia de la señal principal y la potencia de los productos de intermodulación de tercer orden. En la Figura 5 se representa dicha relación, y se puede

comprobar como el IP3, en caso de no existir saturación de potencia, coincide con la intersección de la potencia debida al primer armónico y al tercer armónico. Por último, un dispositivo es más lineal cuanto mayor es el IP3, pudiéndose dar este punto referido a la entrada (IIP3) o a la salida (OIP3).

Figura 5. Representación gráfica de los productos de intermodulación de segundo y tercer orden y el cálculo del IP3 para una determinada potencia de entrada [16].

## 2. Estado del arte de LNAs para tecnologías 5G

A la hora de diseñar un amplificador de bajo ruido hay que tener en cuenta la aplicación en la que se integra. En el caso de este TFM, los diseños están enfocados a receptores de comunicaciones inalámbricas 5G. Por este motivo, en este apartado se analizan varios LNAs para dichos receptores diseñados en la misma tecnología. Principalmente se estudian las topologías de los amplificadores, las técnicas de diseño empleadas para la optimización de ciertos parámetros como el consumo de potencia o el área consumida y las prestaciones obtenidas.

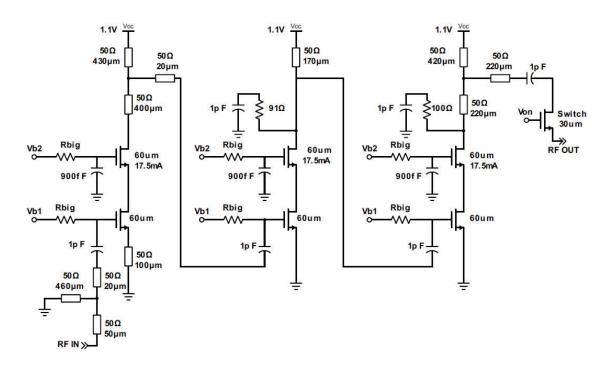

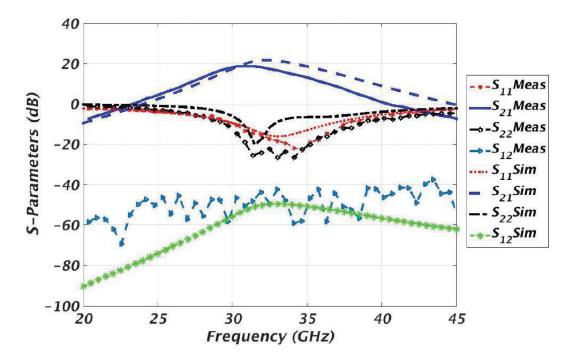

El primer circuito estudiado es un LNA de banda estrecha a una frecuencia de 28 GHz. Es un estudio de la Universidad del Estado de Carolina del Norte, cuyos autores son Vikas Chauhan y Brian Floyd [17]. El amplificador se diseña con la tecnología 45RFSOI, consiguiendo una ganancia máxima de 24 dB y una figura de ruido de 4 dB. En la Figura 6 se muestra el esquemático del diseño, donde destaca que la topología elegida es un cascodo de dos etapas. En la primera de ellas, se emplea un cascodo compuesto por un CS (*Common-Source*) en serie con un CG (*Common-Gate*) con una degeneración inductiva y una línea de transmisión de entrada junto a dos condensadores en serie para aislar la componente continua y conseguir adaptar la entrada del circuito.

Figura 6. LNA a 28 GHz diseñado con 45RFSOI [17].

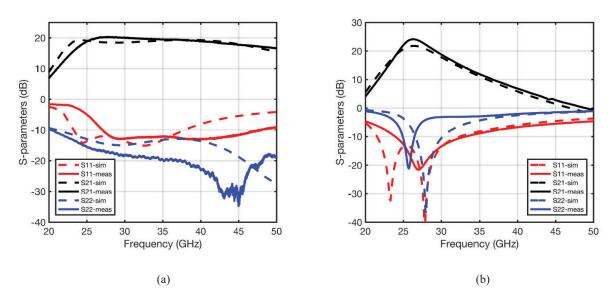

Este mismo estudio presenta un LNA de banda ultra ancha para bandas de frecuencia de 5G entre 24 y 44 GHz. En este caso, se plantea un amplificador en cascodo de tres etapas. En la Figura 7 se ilustra a nivel circuital el diseño, cuya función es configurar las distintas etapas para conseguir el incremento de ancho de banda mediante el aumento de corriente de polarización y la combinación de impedancias para lograr picos de ganancia en 27 GHz y 35 GHz. Ambos diseños se realizan con 45RFSOI, empleando transistores que alcanzan frecuencias de transición (f<sub>T</sub>) equivalentes a 305 GHz con once capas de metales. Se obtiene una ganancia máxima de 20 dB y una figura de ruido comprendida entre 4.2 y 5.5 dB. En la Figura 8 se muestra la respuesta de los parámetros S, perteneciendo la primera gráfica al LNA de banda ultra ancha y la segunda al LNA a 28 GHz.

Figura 7. Esquemático del LNA de banda ultra ancha entre 24 y 44 GHz [17].

Figura 8. Parámetros S del LNA de banda ancha (a) y del LNA de banda ancha a 28 GHz (b) [17].

Los principales parámetros a estudiar de estos dos LNAs se recogen en la Tabla 2 mostrada a continuación:

Tabla 2. Comparación de los resultados de ambos LNAs

|                   | LNA banda ancha    | LNA 28 GHz          |

|-------------------|--------------------|---------------------|

| Tecnología        | 45RFSOI            | 45RFSOI             |

| Frecuencia        | 24-44 GHz          | 28 GHz              |

| Ganancia máxima   | 20 dB              | 24 dB               |

| Figura de ruido   | 4.2-5.5 dB         | 4 dB                |

| otencia consumida | 58 mW              | 18.5 mW             |

| Área consumida    | $0.2 \text{ mm}^2$ | $0.15 \text{ mm}^2$ |

El siguiente diseño es un LNA para sistemas 5G inalámbricos a 33 GHz en una tecnología 28 nm Bulk CMOS [18]. Los objetivos a cumplir con este LNA son la optimización del diseño y la aplicación de técnicas a nivel *layout* que optimicen los componentes activos y pasivos empleados teniendo en cuenta las reglas de densidad de los metales. Se utilizan simulaciones electromagnéticas para obtener un factor de calidad elevado en los componentes pasivos y técnicas eficientes en el *layout* para reducir el área consumida. En la Figura 9 se muestra el esquemático del LNA, el cual consta de dos etapas formadas por cascodos para obtener un mejor aislamiento, aumentar la ganancia y mejorar la estabilidad del circuito. Los transistores de cada etapa están conectados mediante una inductancia para que las capacidades resuenen, mejorando así las prestaciones.

Figura 9. Esquemático del LNA a 28 GHz bajo una tecnología de 28 nm CMOS [18].

En la Tabla 3 recogen los resultados obtenidos con este LNA, destacando que se obtiene una ganancia máxima de 18.6 dB y una figura de ruido de 4.9 dB cuando el diseño se alimenta con 1.2 V, mientras que cuando se alimenta con 2 V se obtienen unos valores de 24.5 dB y 4 dB respectivamente.

Tabla 3. Resumen de las prestaciones del LNA estudiado

| Tecnología         | 28 nm CMOS          |

|--------------------|---------------------|

| Frecuencia         | 33 GHz              |

| Ganancia máxima    | 18.6   24.5 dB      |

| Figura de ruido    | 4.9   4 dB          |

| Potencia consumida | 9.7   27.6 mW       |

| Área consumida     | $0.23 \text{ mm}^2$ |

En la Figura 10 se observa el *layout* del LNA estudiado, donde se indican las bobinas empleadas con la nomenclatura empleada en el esquemático. A su vez, en la Figura 11 se contempla la respuesta de los parámetros S medidos frente a los simulados, siendo aproximadamente similares.

Figura 10. Layout del LNA a 33 GHz para el receptor 5G.

Figura 11. Comparativa de los parámetros S medidos frente a los simulados.

En la literatura existen múltiples receptores 5G que poseen LNAs con características determinadas en función de las prestaciones que se deseen obtener. Por este motivo, es fundamental que el proceso de diseño elegido para desarrollar un proyecto sea el correcto. El proceso de diseño seguido en el trabajo de la Universidad de California comprende la realización de un diseño de un LNA mediante un proceso CMOS SOI [19]. La primera fase del diseño es la elección del tipo de transistor, pudiendo ser de tipo *floating body* FET o *body-contacted* FET. La elección de uno u otro depende de las prestaciones que aporta cada uno al rendimiento del circuito, teniendo los FB-FET una figura de ruido menor y consiguiendo una mejor frecuencia de transición. Por su parte, los BC-FET permiten controlar mejor la tensión

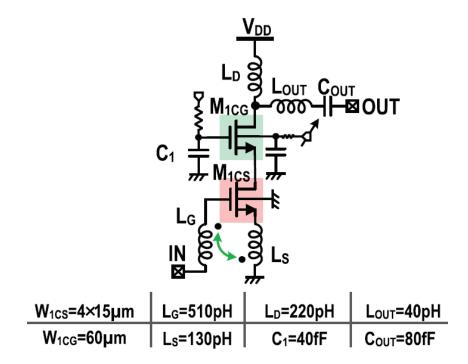

umbral del transistor, incrementando las prestaciones en términos de linealidad. No obstante, con esta elección, disminuye la ganancia y empeora la figura de ruido del diseño. La siguiente decisión es definir la tipología del circuito, siendo interesante un cascodo en los procesos CMOS SOI. Las ventajas aportadas por el cascodo comprenden la mejora de la estabilidad, la figura de ruido y el ancho de banda del diseño. Para ello, los transistores que forman dicha estructura deben tener una configuración determinada, siendo principalmente Puerta Común (*Common-Gate*, CG) o Fuente Común (*Common-Source*, CS). En dicho artículo, se emplean varias combinaciones de transistores FB o BC para la conformación del cascodo, obteniendo que para frecuencias en el rango de la banda Ka, la configuración ideal del cascodo es con dos FB. El esquemático del circuito se muestra en la Figura 12, donde se expone el cascodo, así como en la Figura 13 los resultados de la ganancia y la figura de ruido mínima frente a la densidad de corriente.

Figura 12. Esquemático del cascodo en configuración CG-CS [19].

Figura 13. Resultados de la figura de ruido mínima y la ganancia frente a la densidad de corriente [19].

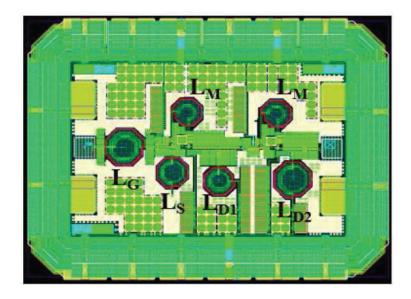

La aplicación principal de este LNA son las comunicaciones satelitales, por lo que obtener una figura de ruido reducida es fundamental, repercutiendo directamente en el factor de calidad (*Quality*, Q) de la bobina de puerta, puesto que es la vía de entrada de la señal. El factor Q se relaciona con la conductividad del metal, el grosor y las pérdidas en el sustrato, entre otros parámetros. Puesto que se emplea cobre, las capas de metalización UA y UB son las más adecuadas de la tecnología para conseguir un factor Q elevado. Por otro lado, la tecnología empleada es de tipo SOI, con una longitud mínima de puerta de 45 nm, alimentando el diseño con 1.5V y una corriente de polarización de 10 mA. Respecto a los resultados obtenidos, se consigue una ganancia entre 14-12.8 dB y una figura de ruido entre 1.3-1.6 dB en el rango de 24 a 28 GHz, con un área consumida correspondiente a 530 μm x 570 μm, y con la disposición física mostrada en la Figura 14:

Figura 14. Implementación a nivel físico del LNA [19].

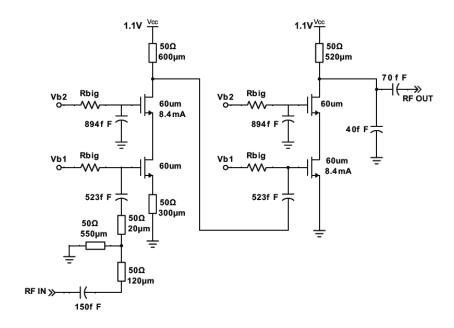

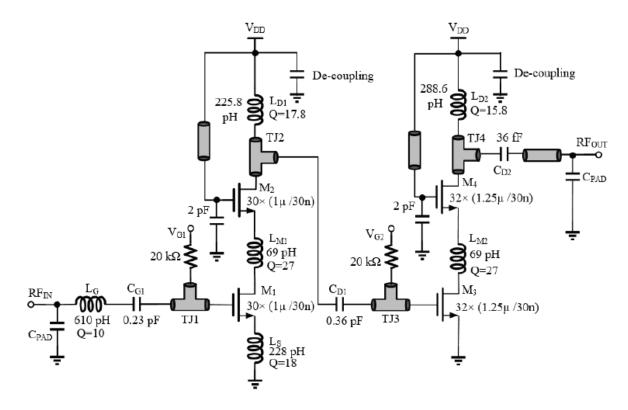

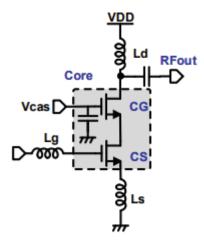

El último diseño analizado es un LNA para 5G empleando *Forward Body Bias* (FBB) sobre una tecnología de 22 nm FDSOI (*Fully Depleted Silicon-On-Insulator*) [20]. Omar El-Aasar y Rebeiz diseñan un amplificador de bajo ruido con un consumo y una NF reducida, así como elevada linealidad y ganancia. Para realizar el diseño, se centran en la topología de un LNA en cascodo. La degeneración inductiva en un LNA permite obtener buenas prestaciones en términos de figura de ruido y consumo de potencia siempre que se incremente el área del transistor y se inyecte la densidad de corriente óptima para mínimo ruido. A su vez, la impedancia óptima (Z<sub>opt</sub>) de un circuito es aquella a la que se consigue la mínima figura de ruido. Por esta razón, y como se observa en la Figura 15 perteneciente al diseño a nivel circuital, la inductancia L<sub>s</sub> tiene la función de reducir la parte real de la impedancia de entrada (Z<sub>in</sub>) y acercar dicha impedancia a Z<sub>opt</sub>. Al mismo tiempo, en la puerta se emplea una inductancia (L<sub>g</sub>) para que la capacitancia de Z<sub>in</sub> resuene a 50 Ω.

Figura 15. Esquemático del LNA implementado con los valores de los componentes [20].

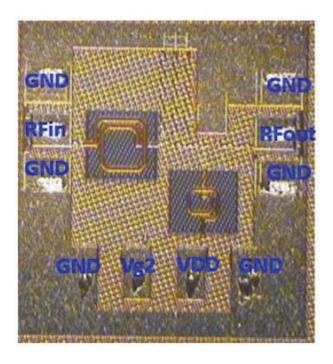

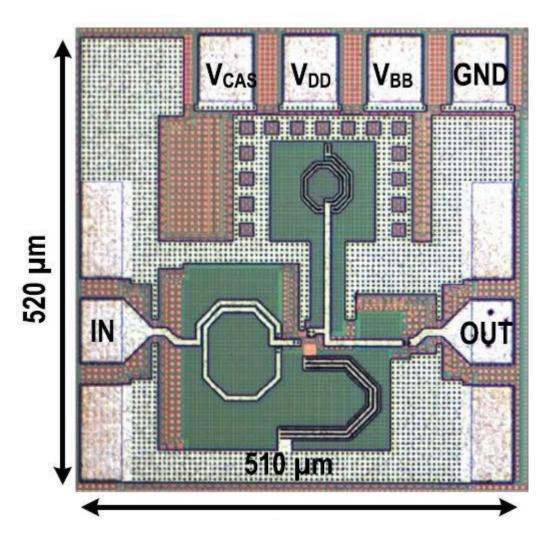

Otro aspecto a destacar de este diseño es el empleo de FBB para reducir el consumo de potencia, mejorar la ganancia y la conductancia de salida regulando la tensión aplicada al Bulk. Concretamente, reducen la tensión umbral (V<sub>TH</sub>) de 320 mV a 50 mV para valores de FBB de 0 a 4 V. Por su parte, en la Figura 16 se muestra el diseño del chip, donde se diferencian las bobinas de drenador y puerta, y la sustitución de la bobina de fuente por una línea de transmisión para optimizar el consumo de área. Asimismo, los autores presentan varios diseños empleando etapas de CS-CS o CAS-CAS. Los resultados obtenidos en dichas implementaciones se recogen en la Tabla 4.

Figura 16. Implementación del chip con las medidas y los terminales [20].

Tabla 4. Resultados de las diferentes implementaciones en función de la topología

| Tecnología           |           | 22 nm FDSOI |            |

|----------------------|-----------|-------------|------------|

| Topología            | Cascodo   | CS          | Cascodo    |

| r op orogin          | (1 etapa) | (2 etapas)  | (2 etapas) |

| Frecuencia (GHz)     | 21.6-32.8 | 19.5-29     | 23-27      |

| V <sub>DD</sub> (V)  | 0.8/1.6   | 0.4/0.8     | 0.8/1.6    |

| Consumo (mW)         | 6/15      | 3.2/9.6     | 5.5/20     |

| Ganancia máx. (dB)   | 7.8/10.2  | 16.9/20.1   | 23.2/28.5  |

| Figura de ruido (dB) | 2.65/2.2  | 2.18/2.08   | 2.38/2.25  |

| Área (mm²)           | 0.12      | 0.19        | 0.19       |

#### 3. Conclusiones

En este capítulo se realiza un análisis desde un punto de vista teórico de los principales parámetros a tener en cuenta de un LNA. Se presenta la base teórica de los LNA como paso previo al estudio de la tecnología 45RFSOI. A su vez, se estudian algunos LNAs que forman parte de receptores 5G, determinando principalmente las topologías elegidas para diseñarlos, que comúnmente son cascodos por las ventajas que proporcionan a nivel de ganancia, aislamiento del circuito y reducción del consumo al emplear la corriente de una etapa para alimentar al resto de transistores. A pesar de que la figura de ruido se empeore, destaca el aumento notable de la ganancia. Del mismo modo, algunos de los diseños propuestos emplean la misma tecnología que en este Trabajo Fin de Máster, por lo que puede ser interesante para comparar los resultados en cuanto a ganancia y figura de ruido con los diseños propios.

# Capítulo 3. Estudio de la Tecnología 45RFSOI

En el presente capítulo se detalla la tecnología empleada, así como los componentes del kit de diseño utilizados en los diferentes circuitos. Cabe destacar que se analizan los componentes pasivos y activos de 45RFSOI, haciendo hincapié en los transistores, bobinas y condensadores, en concreto, aspectos como dimensiones, topologías o metales que forman dicho componente.

## 1. Introducción a la tecnología

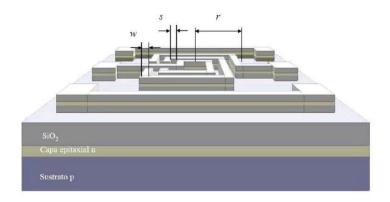

La tecnología elegida para realizar el diseño es 45RFSOI, perteneciente a la fundidora GlobalFoundries. Al ser una tecnología puntera en el campo de la nanotecnología, puede emplearse en diferentes tipos de diseños, siempre en función de las prestaciones esperadas de la misma. En el caso del presente TFM, el circuito diseñado pertenece al ámbito de la radiofrecuencia, buscando así elevadas frecuencias de trabajo con pérdidas reducidas al ser una tecnología de tipo SOI (*Silicon On Insulator*). Este tipo de circuitos implementados en 45RFSOI pueden emplearse en el despliegue de estaciones base de 5G, telefonía, radares, etc., gracias a las características que ofrecen.

La característica notoria de esta tecnología es que la longitud mínima de puerta es de 45 nm, pudiendo emplear de siete a once capas de metales como cobre o aluminio, de las cuáles, la capa más separada del sustrato es aluminio y el resto es cobre. Respecto a la tensión de alimentación, depende del tipo de transistor, puesto que en los transistores de óxido fino la tensión está comprendida en un rango de 0.9 V a 1 V, y para los de óxido grueso la tensión puede llegar hasta 1.5 V y 1.8 V. A su vez, el transistor de óxido fino dispone de un espesor de óxido de puerta de 1.16 nm, mientras que el espesor de óxido de puerta del transistor grueso es de 2.5 nm. Entre los componentes de la tecnología destacan los condensadores MIM (*Metal-Insulator-Metal*) y los inductores con un factor de calidad Q elevado.

#### 2. Elementos Pasivos

Por definición, los elementos pasivos son aquellos componentes incapaces de suministrar potencia a la señal que los recorre, por lo que se emplean en funciones de almacenamiento, disipación o liberación de energía, como es el caso de las resistencias, condensadores o inductores.

### I. Resistencias

El objetivo de una resistencia es dificultar el paso de la corriente que la atraviesa. Además, es uno de los componentes más sencillos y comunes en el mundo de la electrónica,

cuyo valor se mide en Ohmios ( $\Omega$ ). Los elementos que definen el valor de una resistencia son el tipo de material y las dimensiones, relacionándose según la ecuación (6), donde  $\rho$  es la resistividad del material, t es el grosor del material, t el largo del mismo, así como t el ancho. En la Figura 17 se muestra una representación simple de una resistencia.

$$R = \frac{\rho}{t} \frac{L}{W} (\Omega) \tag{6}$$

Figura 17. Modelo simplificado de una resistencia [21].

En un diseño CMOS, el valor de la resistividad se ve afectado por las variaciones de tensión y de la temperatura, midiéndose dichos cambios en ppm/°C, siendo partes por millón entre grados centígrados. Por esta razón, se deben acotar los valores que puede tomar la resistencia en función de la tensión y la temperatura, tal y cómo indica el fabricante al diseñador en la tolerancia de dichos componentes [21].

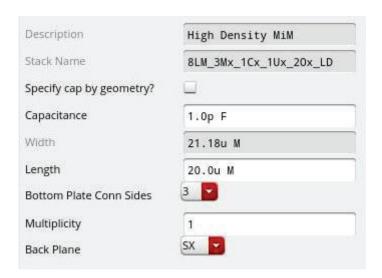

#### II. Condensadores

La función de un condensador es almacenar energía sustentando un campo eléctrico, estando compuesto por dos superficies conductoras separadas por un material dieléctrico o un vacío. Para que se adquiera una carga eléctrica que sea capaz de retener o suministrar energía en procesos de carga y descarga, es necesario que exista una diferencia de potencial entre ambas superficies [22].

Existen numerosas formas de diseñar un condensador, aunque principalmente se implementan dos tipos: MIMCAP (*Metal-Insulator-Metal*) y MOMCAP (*Metal-Oxide-Metal*), diferenciándose en el compuesto presente entre las superficies. En el caso de los MIMCAP, las superficies metálicas que conforman el componente están separadas por un material aislante, presentando así características como la resistencia frente a variaciones de tensión y temperatura. Asimismo, permiten las escalabilidad de valores capacitivos, reduciendo el valor de las capacidades parásitas al situarlos en las capas elevadas del metal, lejos del sustrato [23]. Por su parte, el MOMCAP, también conocido como VPP (*Vertical Parallel Plate*) o condensador de flujo lateral, se caracteriza por una elevada densidad capacitiva y una reducida

capacidad parásita. Sin embargo, este tipo de condensadores presenta inconvenientes en el cálculo de su valor al depender de la frecuencia de funcionamiento.

En ambos modelos, la capacitancia depende de las dimensiones del dispositivo (W, L) así como de la multiplicidad (M). Al mismo tiempo, estos parámetros repercuten en la capacidad por unidad de área (C<sub>a</sub>) y la capacidad por unidad de perímetro (C<sub>p</sub>). Para ejemplificar ambos condensadores, su esquemático se muestra en la Figura 18, indicándose el metal al que está conectado cada terminal, así como en la Figura 19 el *layout* de cada condensador.

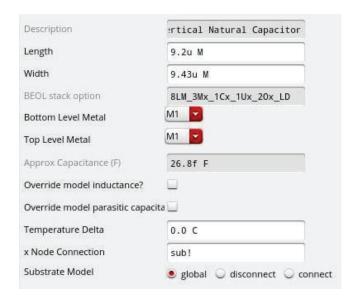

Figura 18. Esquemático del condensador mimhd (a) y mimhq (b).

Figura 19. Layout de las condensadores mimhd y mimhq [16].

Respecto a los valores que pueden tomar ambos condensadores, cabe destacar que dependen de los parámetros mencionados previamente, tal y cómo se indica en la Tabla 5:

|                     | Ca (fF/μm²)      | Cp (fF/μm)     | L (m) | W (m) | M |

|---------------------|------------------|----------------|-------|-------|---|

| High Density<br>MIM | 2.4±0.36         | $0.2 \pm 0.18$ | 6µ    | >=5µ  | 1 |

| High-Q MIM          | $0.335 \pm 0.05$ | 0.11±0.099     | 6μ    | >=5µ  | 1 |

Tabla 5. Posibles valores de los parámetros de los condensadores MIM

En el caso de los condensadores con elevado factor de calidad, para calcular Q se sigue la ecuación (7), donde se indica la relación entre la energía máxima almacenada y la energía disipada en el circuito en cada oscilación. A su vez, la ecuación se basa en los parámetros de admitancia Y, obteniendo el valor de Q una forma más precisa [24].

$$Q = \operatorname{Imag}[Y_{22}]/\operatorname{Real}[Y_{22}] \tag{7}$$

#### III. Bobinas

Una bobina es un elemento pasivo capaz de almacenar energía en forma de campo magnético cuando la corriente eléctrica fluye a través de ella. Dentro del ámbito de la microelectrónica, se emplean bobinas integradas que se obtienen mediante una espiral de pistas metálicas sobre un sustrato. En la Figura 20 se muestra un ejemplo de una bobina integrada, así como los parámetros que definen su geometría. Se puede apreciar el parámetro w que corresponde con la anchura de las pistas, el parámetro s indica la separación entre pistas y la variable r define el radio de la bobina.

Figura 20. Estructura de una inductancia cuadrada en espiral simple [21].

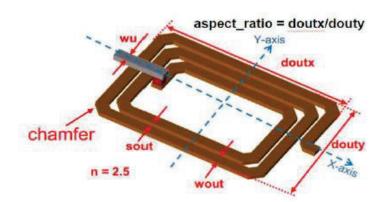

Las bobinas proporcionadas por el kit de diseño 45 RFSOI de GlobalFoundries poseen una forma de espiral cuadrada o rectangular como la que se muestra en la Figura 21. El inconveniente de las bobinas integradas es que para elevadas frecuencias se incrementan las pérdidas por el efecto *skin* y las pérdidas debidas a efectos de proximidad inducidas por el campo magnético, algo que es típico en ellas. En este caso, al usar solamente dos dimensiones para implementarlas, se accede al terminal que se encuentra en el interior de la espiral por medio de un segundo nivel de metal llamado *underpass*. En la propia figura, se puede ver que se nombran algunos parámetros como *sout*, que es el espacio entre espiras, pudiendo ser de 3 µm o 4 µm, la relación de aspecto entre el largo (*doutx*) y el ancho (*douty*) de la bobina que puede ser de 1, 1.4 o 2 y *wout* es el ancho de la pista. Por lo tanto, a la hora de realizar el diseño de la bobina que se quiera incluir en el circuito, se deben respetar estos parámetros e incluir otros como el número de vueltas.

Figura 21. Inductancia en espiral rectangular con los parámetros de diseño [25].

Uno de los parámetros principales de las bobinas es el factor de calidad (Q). Dicho factor se define como la relación entre el pico de energía almacenada por ciclo y la potencia disipada por ciclo para un elemento reactivo con pérdidas reales. Sin embargo, en el caso de los inductores en espiral es complejo calcular el valor de Q debido a que se debe conocer la energía almacenada y la potencia disipada instantáneamente por cada elemento reactivo. Por lo

tanto, se utiliza un método común para calcularlo partiendo de los parámetros Y, aplicando la expresión (8) [25].

$$Q_{conv} = -\left(\frac{\text{Imag}[Y_{11}]}{\text{Real}[Y_{11}]}\right) \tag{8}$$

Este método es conocido como "Q convencional" y es válido para frecuencias bajas dónde la espiral actúa como un circuito RL. Pero en caso de que se use un inductor con espiral simétrica, el cálculo de Q es diferente ya que se aplica el método conocido como "Q diferencial", mostrado en las expresiones (9) y (10).

$$Z_{diff} = 2 \cdot Z_0 \cdot \frac{(1 - S_{21}) \cdot (1 - S_{21}) - (S_{11} \cdot S_{22})}{(1 - S_{22}) \cdot (1 - S_{11}) - (S_{12} \cdot S_{21})} (\Omega)$$

(9)

$$Q_{diff} = \frac{Imag(Z_{diff})}{Real(Z_{diff})}$$

(10)

En cuanto a los modelos de inductores de la tecnología, en los circuitos a diseñar se utilizan los de tipo *indr*, aunque se destacan también los siguientes:

- o Indr: Inductor rectangular de una sola capa.

- o **Indrp**: Inductor rectangular apilado en paralelo.

- O Symindr: Espiral simétrica rectangular de una capa.

- o **Symindrp**: Espiral simétrica rectangular apilada en paralelo.

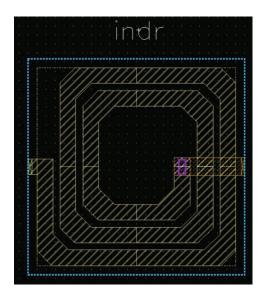

Por lo tanto, los valores de los parámetros de los inductores que se emplean en los diseños se muestran en la Tabla 6. Además, en la Figura 22 se aprecia el *layout* de una bobina *indr*.

Figura 22. Layout de una bobina asimétrica sin apilar (INDR).

Tabla 6. Posibles valores de los parámetros de la bobina INDR

| Tipo de inductor | Largo<br>(m)   | Ancho (m)  | Relación<br>de<br>aspecto | Ancho<br>de la<br>espira<br>(m) | Distancia<br>entre<br>espiras (m) | Nº de<br>vueltas               |

|------------------|----------------|------------|---------------------------|---------------------------------|-----------------------------------|--------------------------------|

| INDR             | 28 μ-<br>400 μ | 28 μ-200 μ | 1, 1.4, 2                 | 2 μ-20 μ                        | 3 μ, 4 μ                          | Mínimo: 1, incrementos de 0.25 |

#### 3. Elementos Activos

Los elementos activos tienen la capacidad de proporcionar ganancia a un circuito. En este trabajo el único elemento activo que se emplea es el transistor MOSFET, pero existen otros elementos activos como los diodos. Además, son elementos que pueden controlar el flujo de carga eléctrica de un circuito.

#### I. Transistores

Los transistores MOS o MOSFETs son elementos activos que están caracterizados por la existencia de dos tipos de transistores complementarios, los de tipo N y los de tipo P, siendo el origen del nombre de la tecnología CMOS (*Complementary Metal-Oxide Semiconductor*). Hay que destacar que los MOSFET presentan una ventaja frente a los BJT (*Bipolar Junction Transistor*), que es el aislamiento entre la puerta y el canal. Esto implica que el flujo de corriente entre la puerta y el sustrato es muy pequeño.

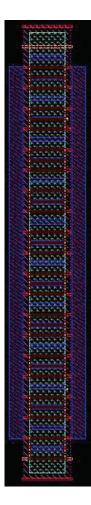

Dentro de los transistores MOS de GlobalFoundries del kit de diseño 45 RFSOI se pueden distinguir dos grupos: los MOSFET de banda base y los de RF, siendo estos últimos los que se usan en el diseño del LNA. Dentro de los transistores MOS de RF existen los siguientes tipos:

- o Floating body NFET con L=  $0.04 \mu m$ .