2. Introducción al QuartusII/Modelsim-Altera¶

2.1. Introducción¶

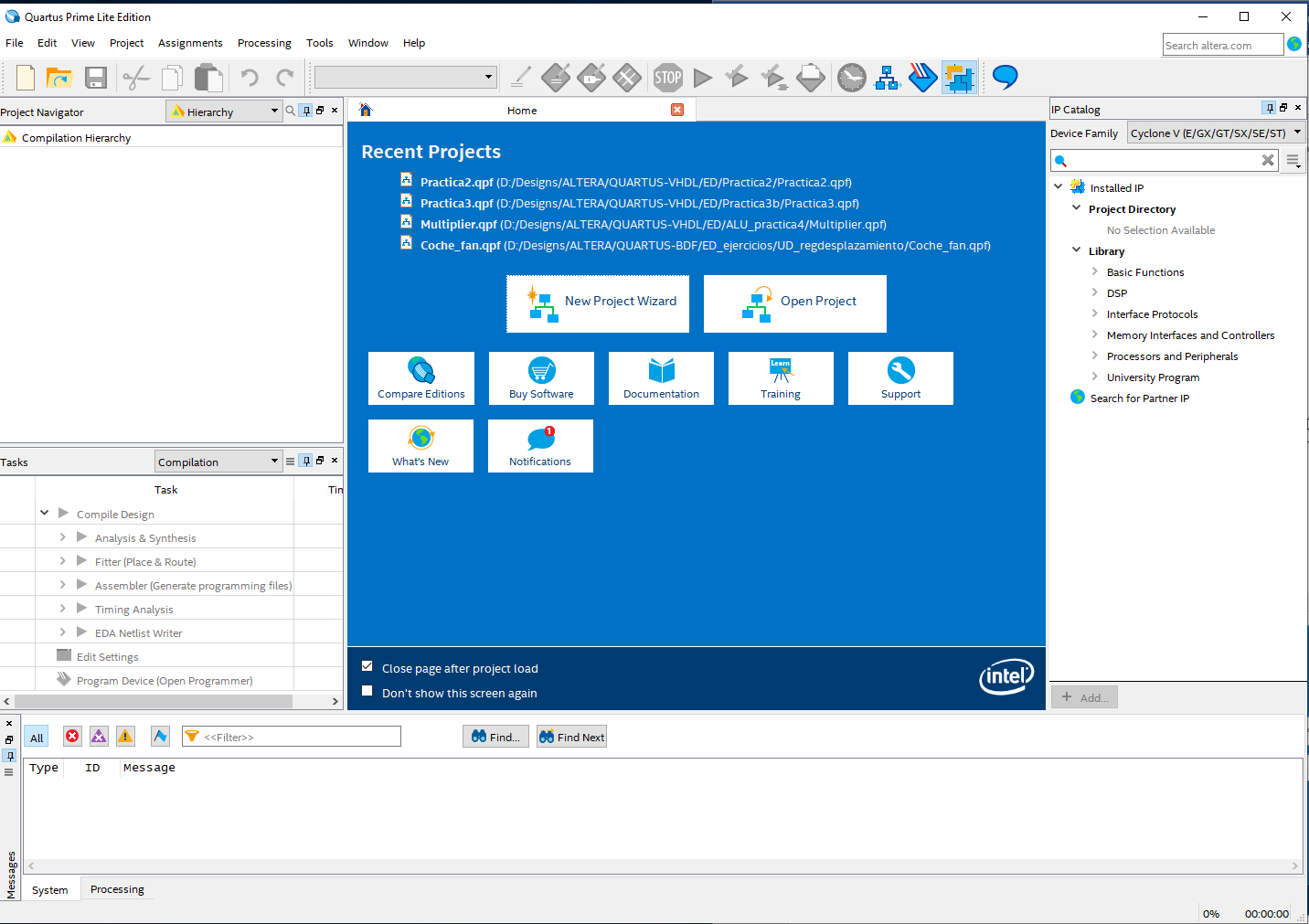

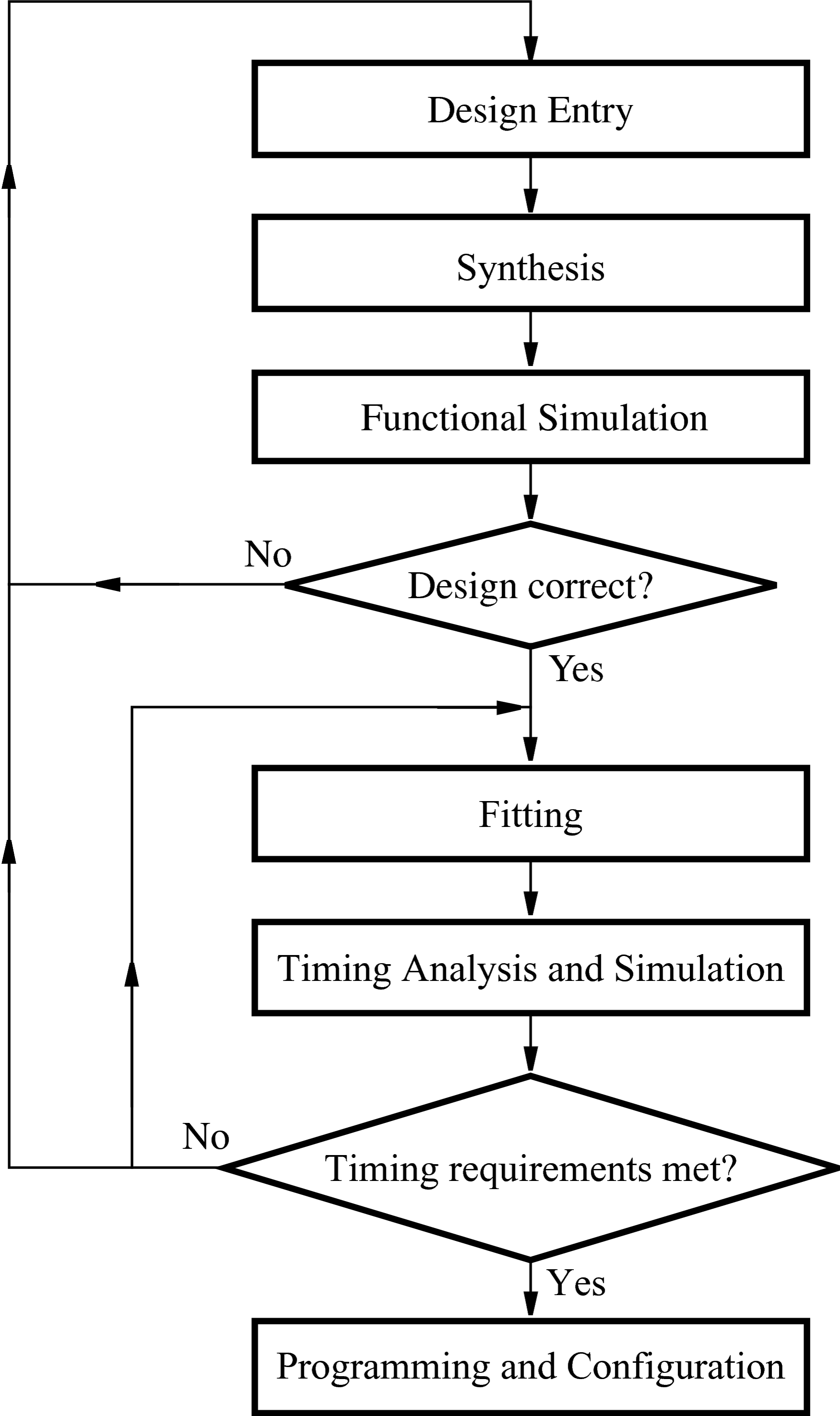

El software de diseño Altera Quartus II proporciona un entorno de diseño completo y multiplataforma que se adapta fácilmente a sus necesidades de diseño específicas. Es un entorno integral para el diseño de sistema en chip programable (SOPC). El software Quartus II incluye soluciones para todas las fases del diseño FPGA y CPLD (Figura 2.1).

2.2. Flujo de diseño¶

El flujo de diseño (es decir los pasos que hay que seguir para implementar un diseño) es el que se muestra en la siguiente figura siguiente:

Figura 2.1 Flujo de diseño en Altera Quartus II.¶

Varios de estos procesos son automáticos y los realiza Quartus II al ejecutar el proceso de compilación. En esta asignatura solo se realizarán los siguientes pasos:

Descripción del diseño (Design Entry). Quartus admite tanto la descripción por medio de esquemáticos como por medio de VHDL. Este tutorial realizará una descripción mixta (primero usando esquemáticos y posteriormente VHDL) pero el resto de prácticas de la asignatura solo utilizará VHDL.

Síntesis (Synthesis), es el proceso que genera un circuito desde VHDL. Proceso automático que realizará Quartus.

Simulación funcional (Functional Simulation). La realizaremos con la versión de Mentor Modelsim incluida en Quartus: Modelsim-Altera.

Fitting, es el proceso de pasar el circuito sintetizado en el paso 2 a la FPGA. Proceso automático que realizará Quartus.

Análisis de tiempos y simulación (Timming Analysis and Simulation). En esta asignatura no se hará el análisis de tiempo, ni la simulación temporal.

Programación y configuración (Programming and Configuration). Paso por el cual se configura la FPGA usando el circuito obtenido en el paso 4. En el laboratorio se realizará este paso mediante la herramienta Programmer de Quartus.

Para realizar todo el flujo de diseño, el software Quartus II permite utilizar la interfaz gráfica de usuario y/o la interfaz de línea de comandos de Quartus II. En estas prácticas de laboratorio únicamente utilizaremos la interfaz gráfica.

2.3. Tutorial de QuartusII¶

2.3.1. Introducción¶

En este tutorial se va a realizar un diseño guiado a través de todos los pasos del flujo de diseño de Altera Quartus II.

Previamente debe seguir todas las instrucciones indicadas en la sección Instrucciones generales. Necesariamente debe haber realizado los siguientes pasos:

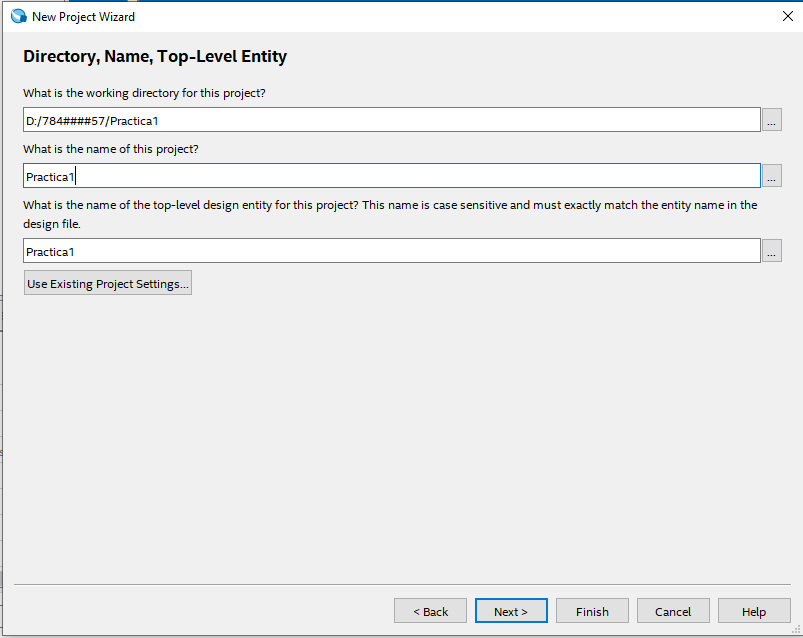

Crear un directorio externo en el disco D: con el número de DNI (todos los números sin letra).

Dentro de ese directorio crear una nueva carpeta con el nombre Practica2. Este directorio es el que va a contener la base de datos de Quartus II.

Advertencia

Nunca poner acentos, ni «ñ», ni espacios en los nombres de los ficheros o diseños.

Nota

Todas las figuras en las que aparece Practica1 debe entenderse como Practica2.

2.3.2. Abrir QuartusII y crear un proyecto¶

Abrir Quartus (Quartus Prime 19.1 Lite Edition)

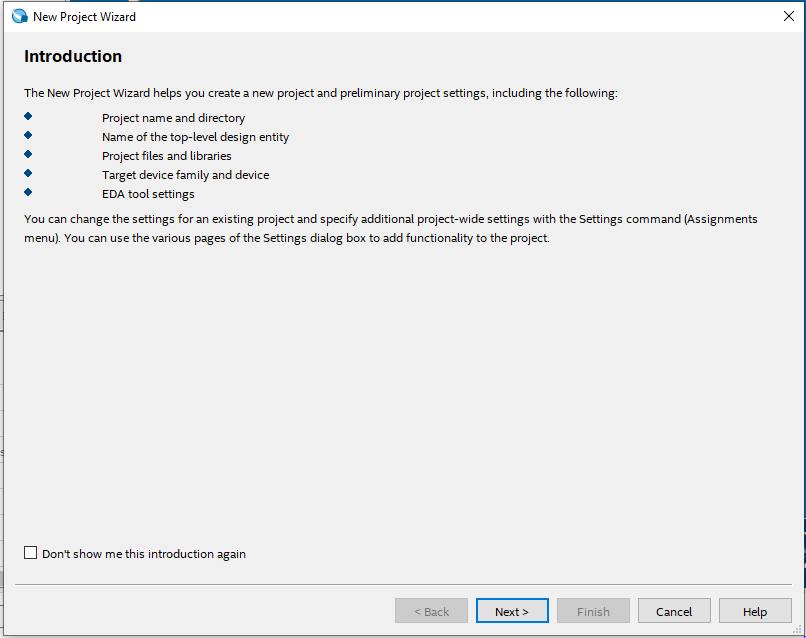

Hacer click en New Project Wizard (en la parte de azul)

Hacer click en NEXT

Seleccionar el nombre del directorio que hemos creado en D: y que se denomina Practica2. Indicar que el nombre del proyecto es Practica2. Inmediatamente debe aparecer también Practica2 como nombre del top-level.

Lo dejamos como está y hacemos click en NEXT

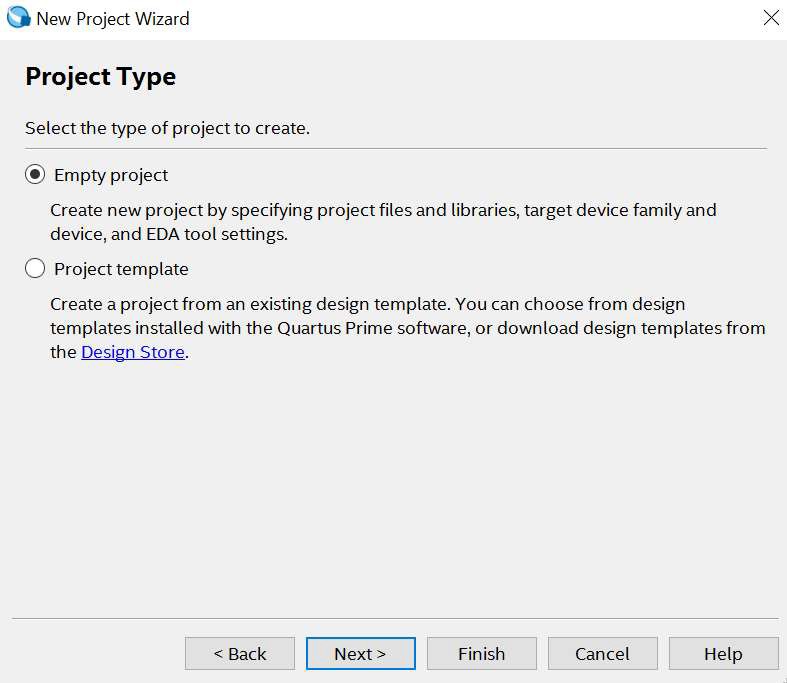

En la siguiente ventana, seleccionamos el tipo de proyecto esta VACIO o «Empty», NEXT

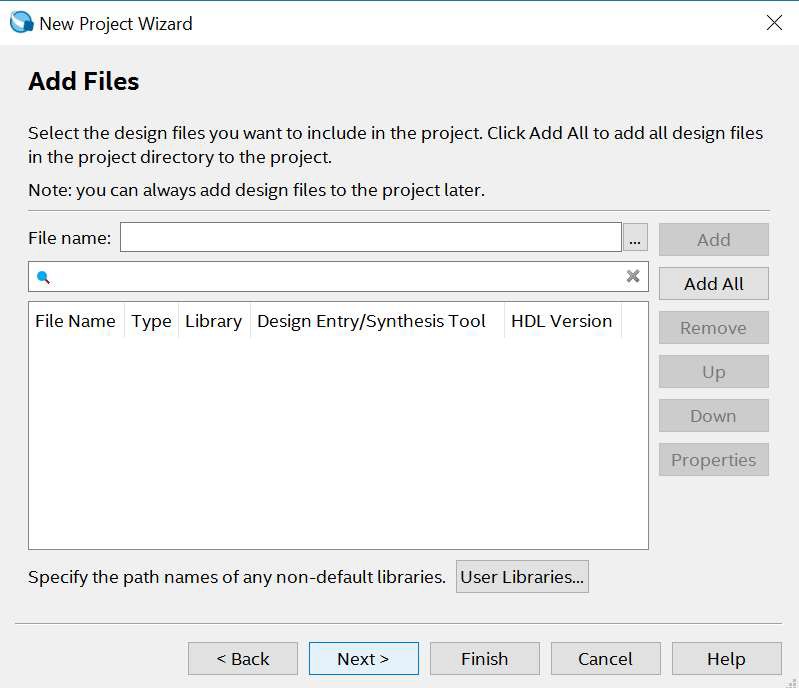

No se requiere añadir archivos. NEXT

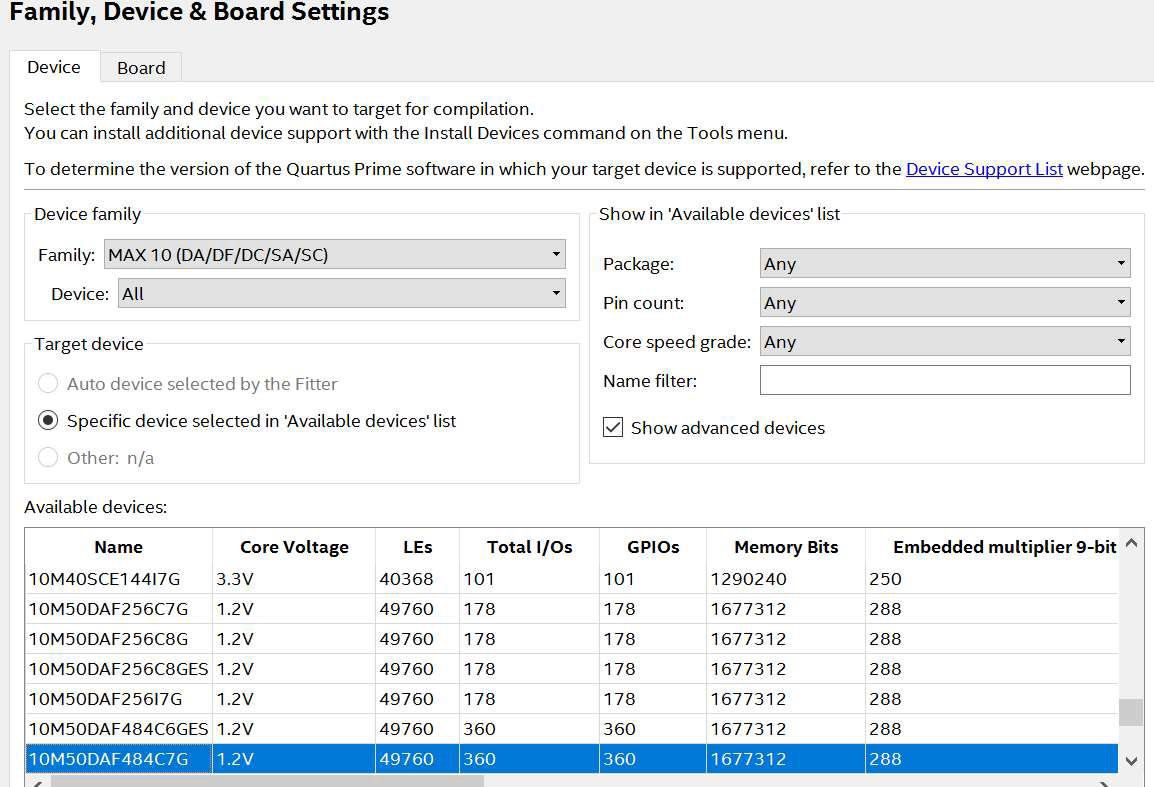

En el cuadro «Family», escogemos «MAX 10» y luego 10M50DAF484C7G. NEXT.

Nota

Es importante seleccionar correctamente el nombre del dispositivo a utilizar.

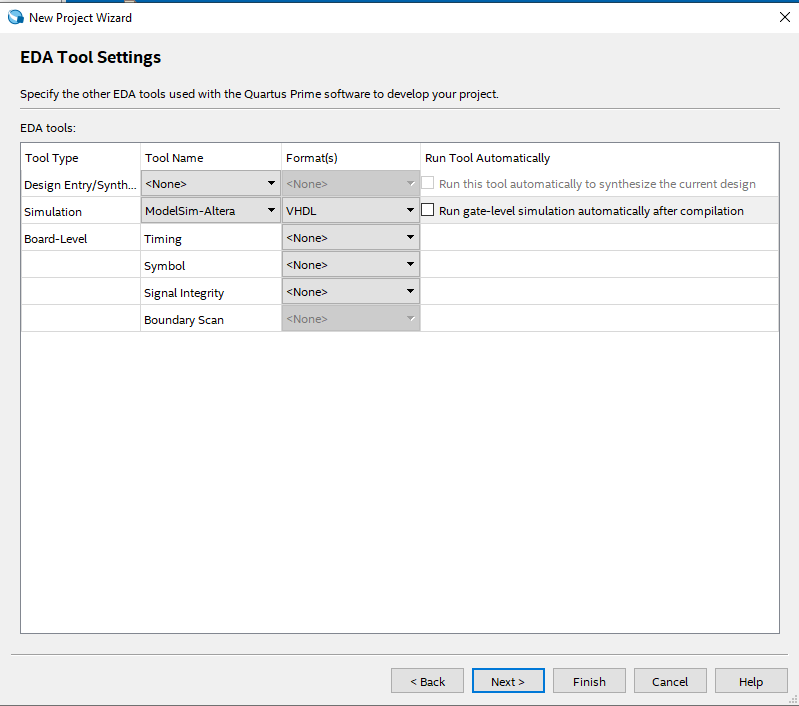

En la ventana de «EDA Tool settings», en «Tool Name» de simulation seleccionar «Modelsim-Altera» y en «Format(s)» seleccionar «VHDL». NEXT

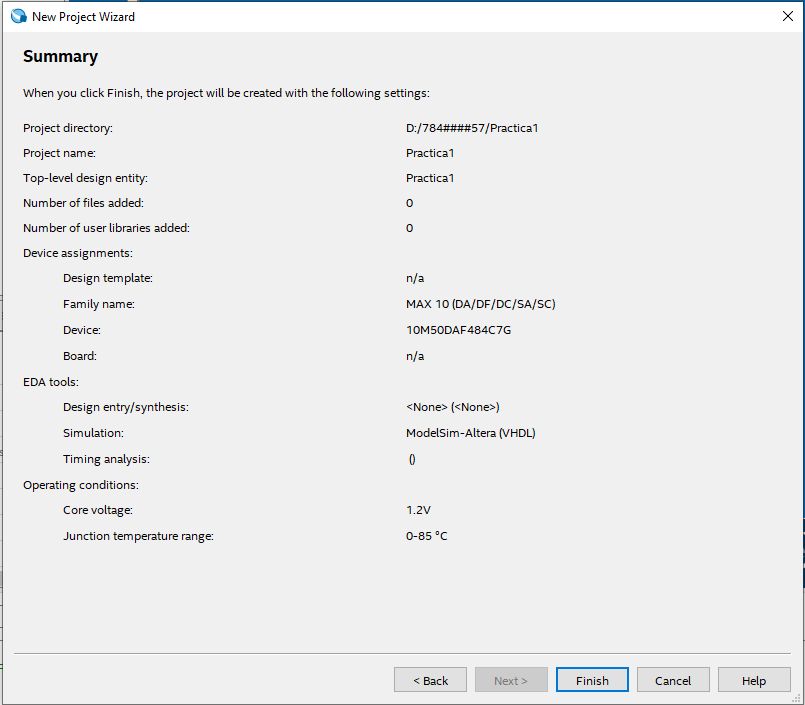

Finalmente aparece el resumen de lo que hemos seleccionado y haciendo click en FINISH habremos terminado de crear el proyecto.

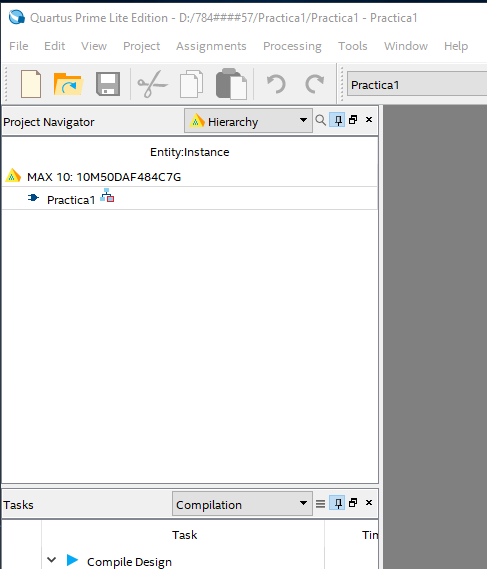

En el Project Navigator del QuartusII debe aparecer el nuevo diseño y el dispositivo seleccionado.

2.3.3. Realizar la captura de esquemas del diseño¶

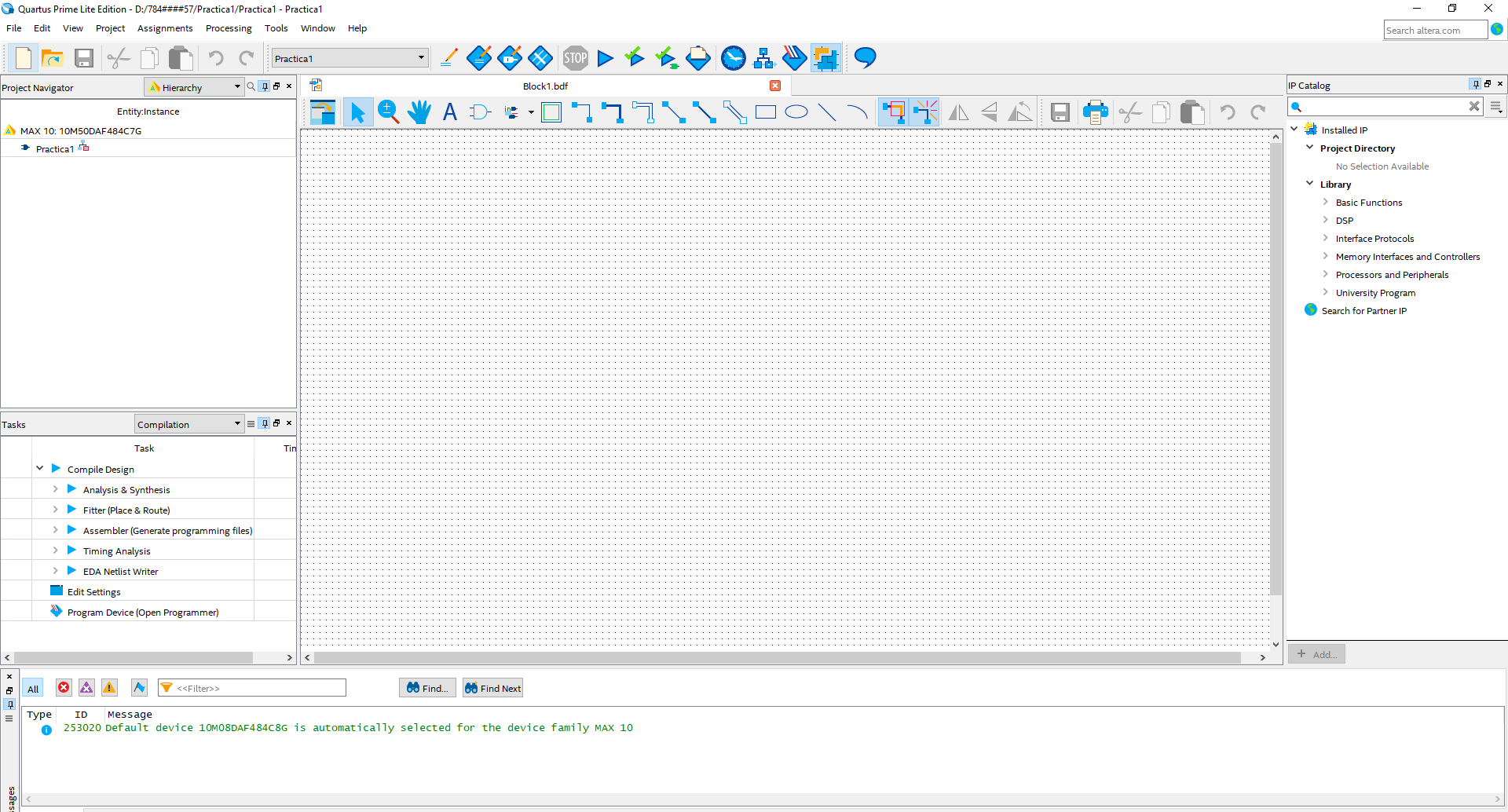

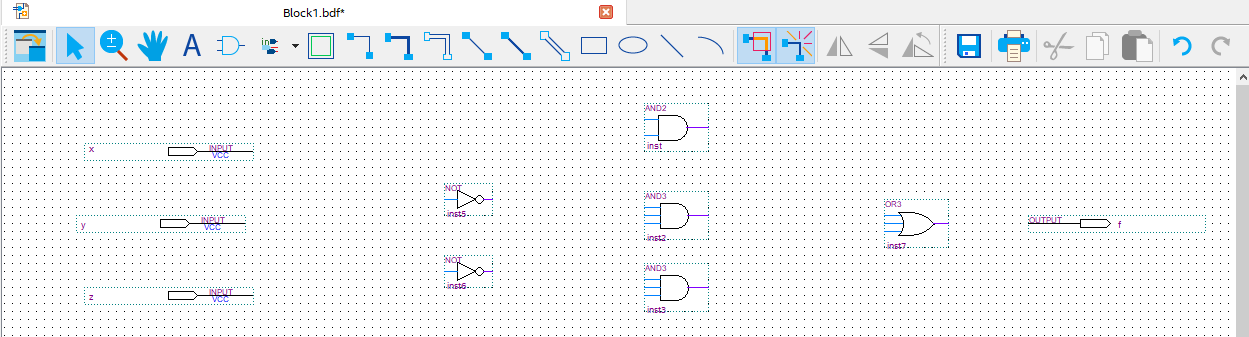

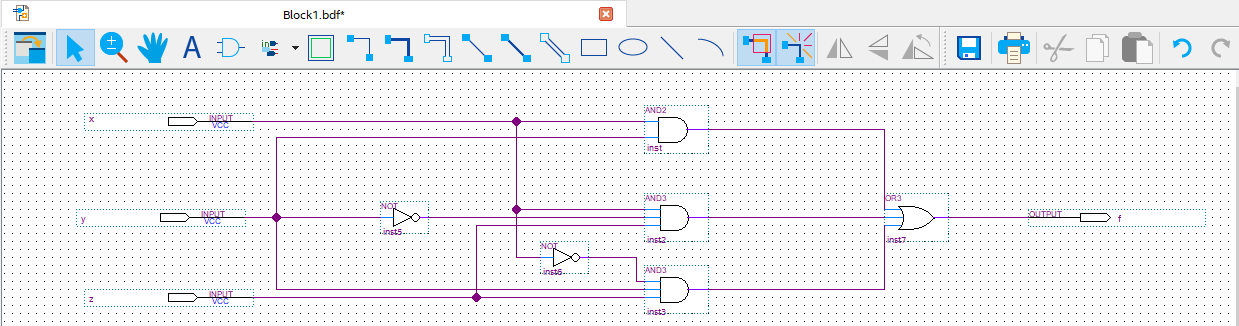

Seleccionar File > New > Design Files > Block/Diagram/Schematic File y aparecerá la siguiente ventana.

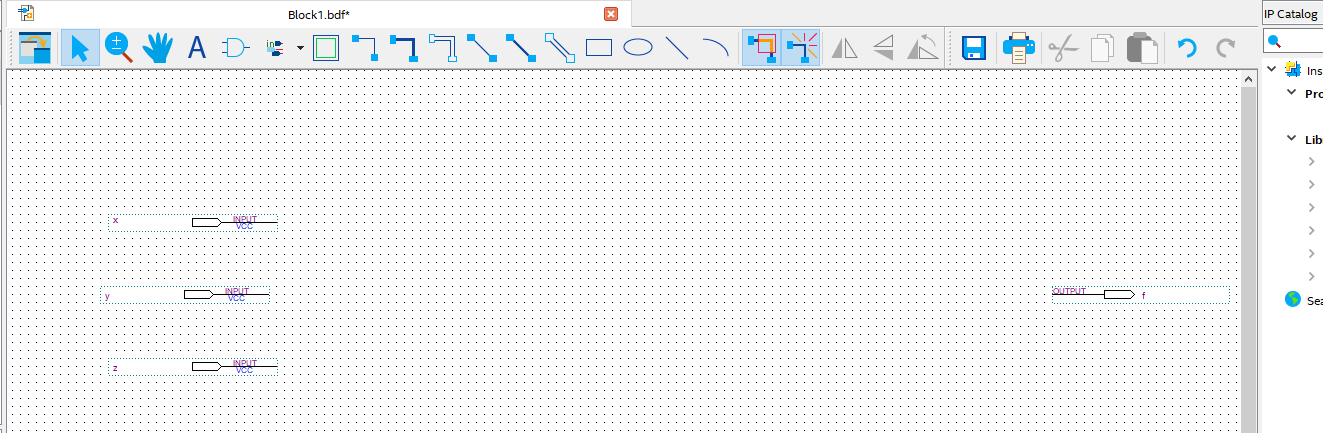

Usando la herramienta de pin (

) incluir tres pines de

«input» y uno «output».

) incluir tres pines de

«input» y uno «output».Hacer click en el «pin_name» de cada uno de los pines e incluir los nombres de entrada x, y, y z, y el de salida f.

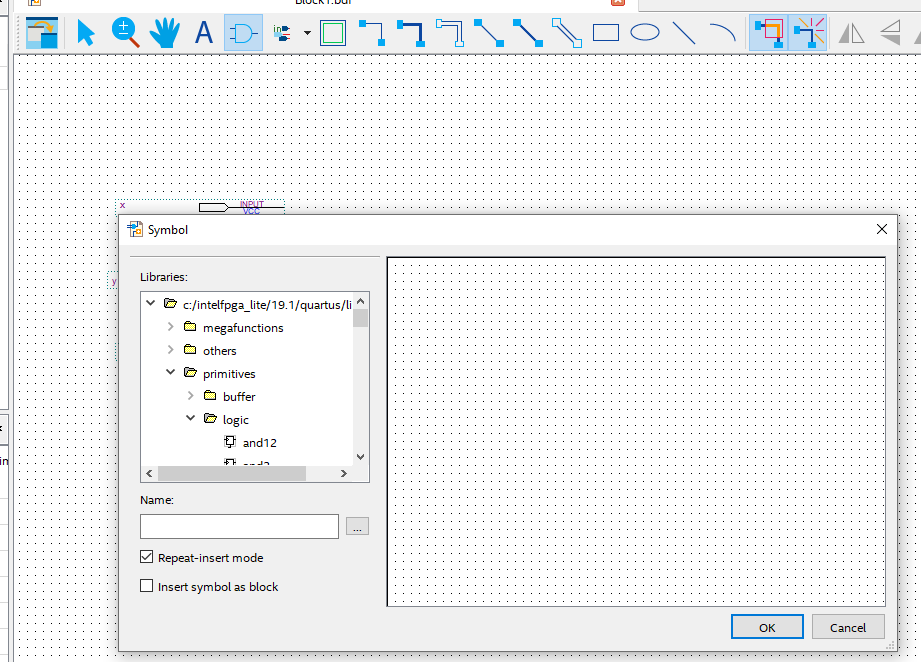

En la herramienta «symbol»(

) seleccionar «primitives/logic»

e incluir en el diseño dos puertas not, una and2, dos and3 y

una or3.

) seleccionar «primitives/logic»

e incluir en el diseño dos puertas not, una and2, dos and3 y

una or3.

Finalmente, los puertos de entrada salida y las puertas lógicas incluidas deben ser las siguientes:

Nota

Nunca poner acentos, ni «ñ», ni espacios en los nombres de los ficheros.

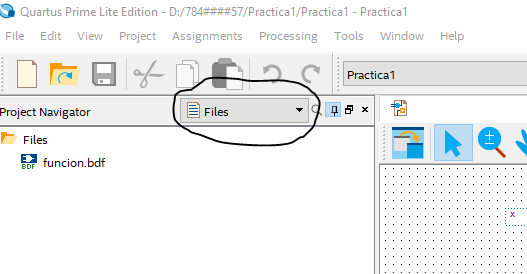

En la ventana del «Project Navigator» seleccionar «Files».

Situar el ratón sobre función.bdf y con la tecla derecha del ratón en el menú emergente seleccionar Set as Top-Level Entity.

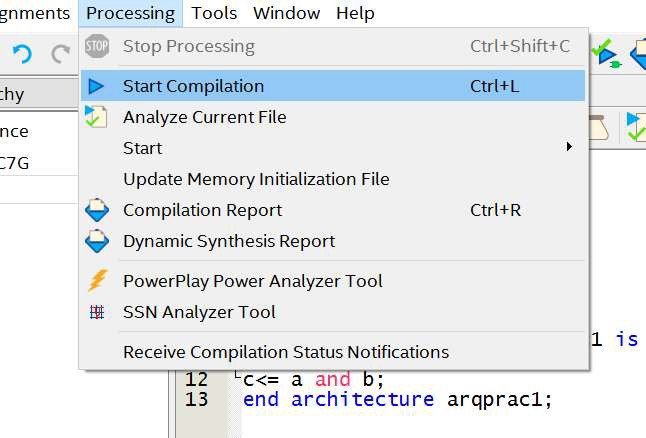

2.3.4. Compilar el diseño¶

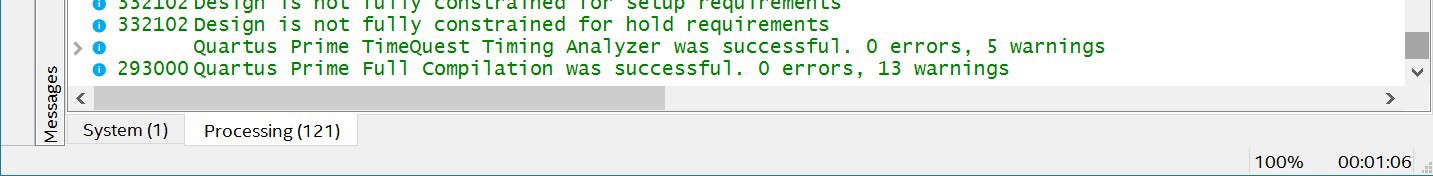

Compilar el diseño usando los menús Processing > Start Compilation.

Tarda sobre 1 min. La compilación, hace como 121 procesos. Si hubo errores, hacer click sobre los mensajes de error para resolverlos en el esquemático. Si no hay errores procedemos a simular el diseño y luego asignar pines.

2.3.5. Simulación del diseño con Modelsim-Altera¶

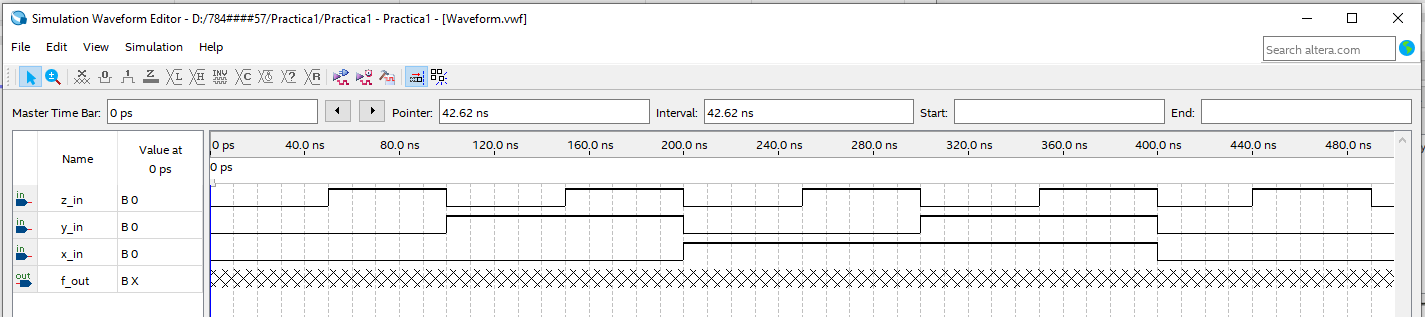

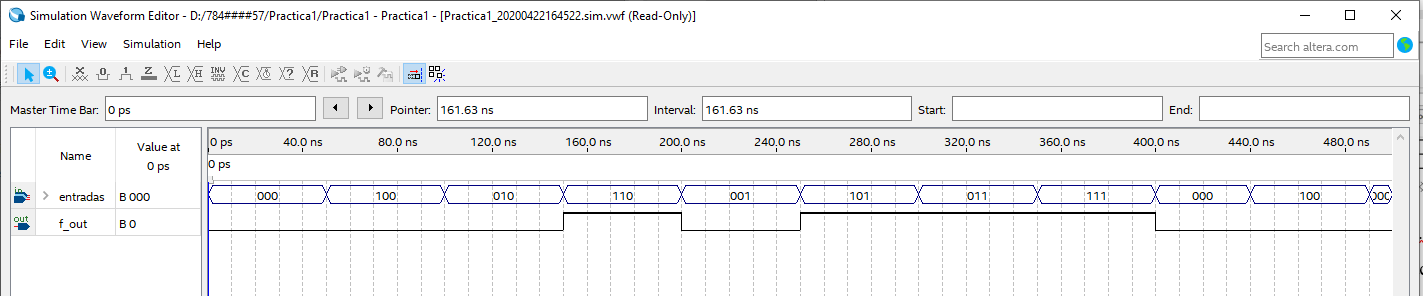

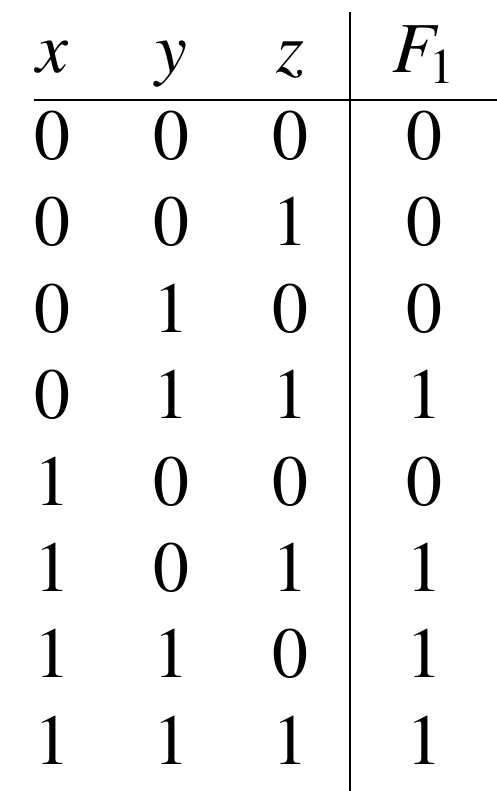

En este apartado se va a realizar una simulación del circuito diseñado. Para ello crearemos un fichero de formas de onda que incluya todas los valores posibles de las entradas. La salida esperada en la que se encuentra en la tabla de verdad que se presenta en la transparencia de la página 40 del tema 2 de teoría.

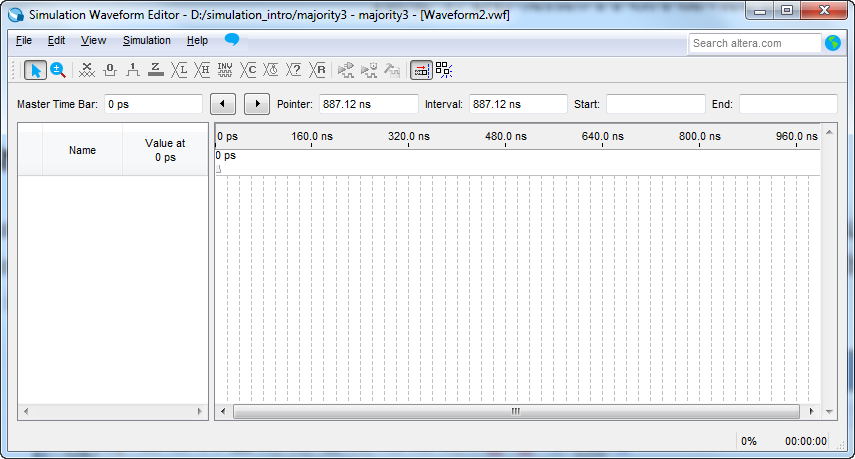

Seleccionar File > New > Verification/Debugging File > University Programm VWF. Aparecerá la siguiente ventana.

Como existen tres entradas en el diseño, habrá 8 posibles variaciones que tendremos que comprobar. A cada variación le daremos un tiempo de simulación de 50 ns, lo que hace un total de 500 ns de simulación. Seleccionamos Edit > Set End Time y especificamos 500ns en la ventana emergente.

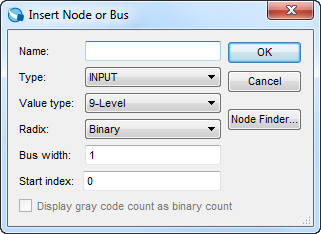

Inlcuir los pines de entrada y salida en la simulación. Seleccionamos Edit > Insert Node o Bus y en la ventana emergente hacemos click en Node Finder.

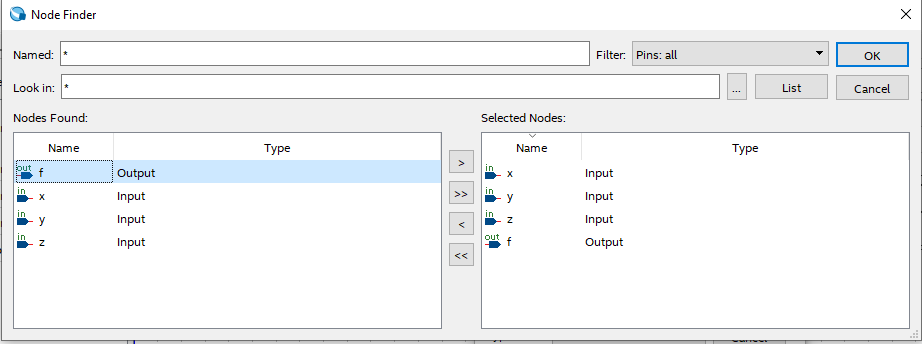

En la ventana de Node finder hacemos click en «List» y vamos pasando a la derecha los nodos que queremos incluir en la selección (en el orden que aparece en la imagen).

En la ventana Simulation Waveform Editor aparecerán las entradas con un valor asignado de «0» y la salida como «no inicializada». Para dar valores a las señales de entrada utilizaremos el menú Edit > value o los iconos de la parte superior de la pantalla.

Seleccionando con el ratón la franja adecuada de cada una de las entradas y dándoles valor de «1» (

), llegaremos al

siguiente resultado:

), llegaremos al

siguiente resultado:

Guardar las formas de ondas File > Save y dejar el mismo nombre Waveform.vwf.

Simular el diseño. Seleccionar Simulation > Run Functional Simulation, o hacer click en el icono

.

.El resultado final aparecerá en una nueva ventana emergente y debe ser el siguiente:

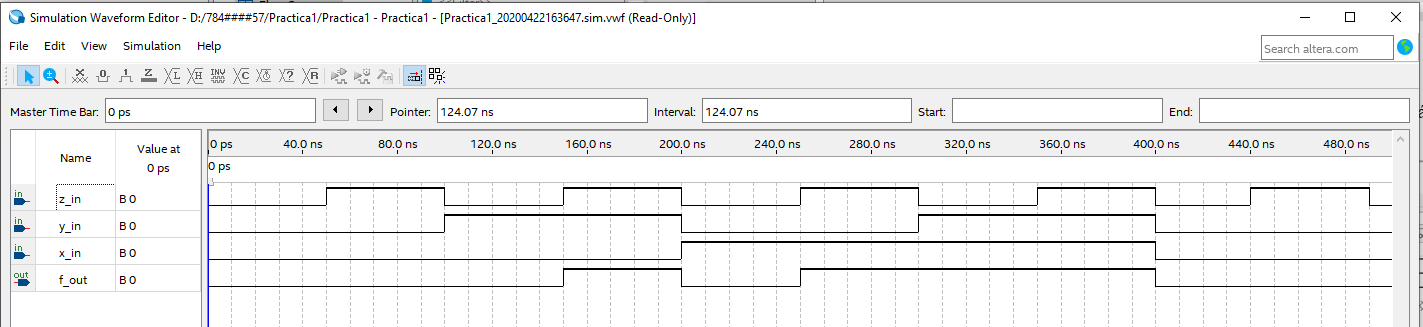

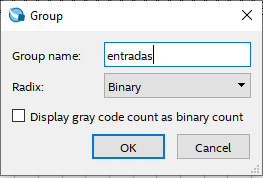

Cerrar la última ventana emergentes (la que tiene el resultado de la simulación) y volvemos a la anterior (la que tiene la salida f sin definir). Usando la tecla CTRL y el ratón, seleccionamos conjuntamente las tres entradas x, y y z (en la parte de la izquierda) y luego Edit > Grouping. En «Group name» ponemos «entradas» y seleccionamos a Ok.

Simulamos de nuevo el diseño y vemos el resultado final más cómodo de leer.

2.3.6. Crear el diseño jerárquico top-level¶

Crearemos un nuevo fichero VHDL usando el menú File > New > Design Files >VHDL File. Aparecerá una ventana nombrada como Vhdl1.vhd.

En esa ventana incluimos la siguiente descripción VHDL:

Como se observa hemos incluido en el VHDL el esquemático funcion.bdf como un COMPONENT denominado funcion (exactamente como el fichero).

Seleccionamos File > Save y damos el nombre de Practica2.vhd al nuevo fichero.

Con la descripción VHDL a la vista seleccionamos el menú Project > Add Current File to Project.

En la ventana de «Project Navigator», situamos el ratón sobre Practica2.vhd y con la tecla derecha del ratón en el menú emergente seleccionar «Set as Top-Level Entity».

Compilar el diseño usando los menús Processing > Start Compilation.

La compilación debería terminar sin errores. Compruebe que la línea final tiene el siguiente aspecto:

Info (293000): Quartus Prime Full Compilation was successful. 0 errors, 14 warnings

2.3.7. Asignación de pines del diseño¶

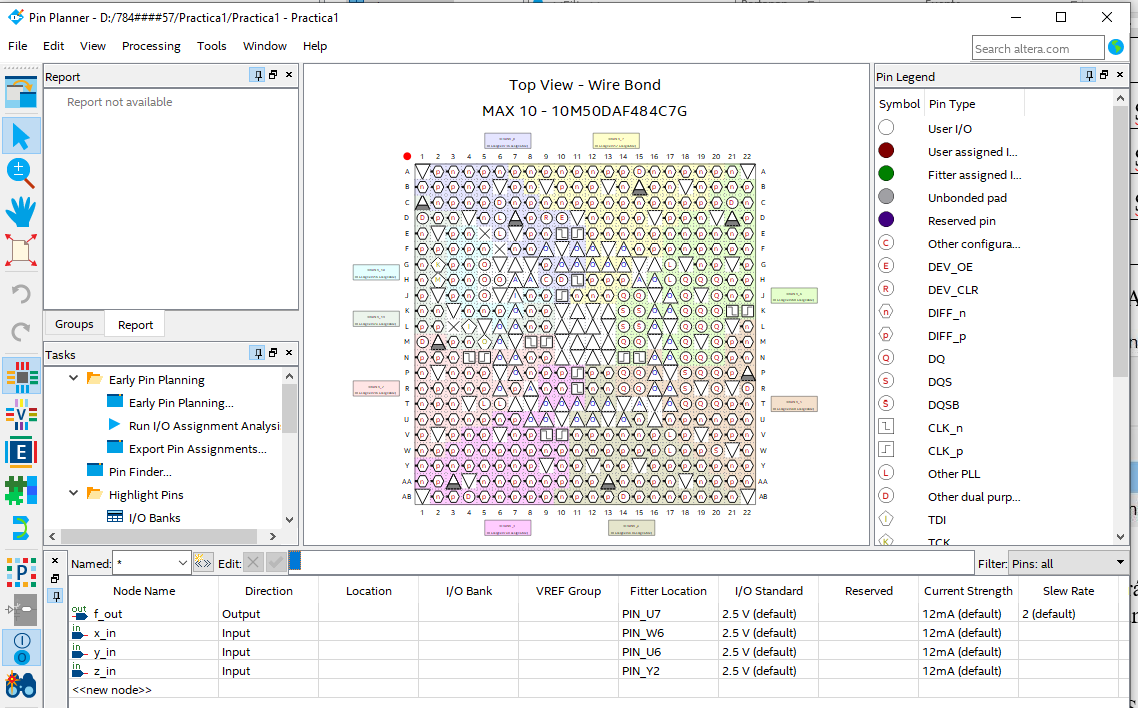

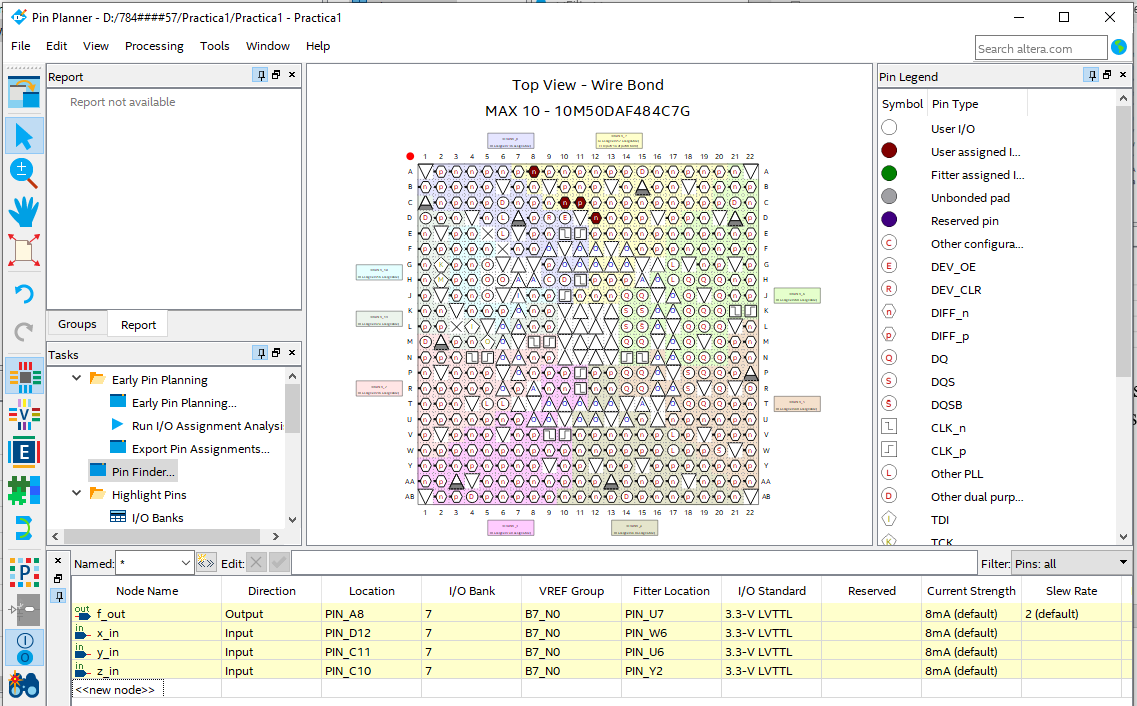

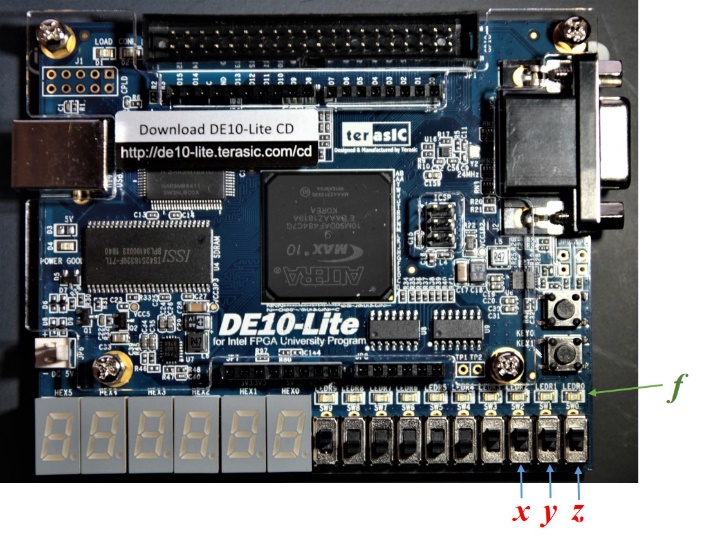

Hasta este momento, se ha realizado la descripción de un circuito digital y se ha comprobado su correcto funcionamiento mediante la simulación. De forma previa a la programación de dicho circuito digital en la placa DE10-Lite, se debe establecer la correspondencia entre las entradas y salidas del circuito con los pines de la placa. Vamos a realizar la asignación de pines según se indica en la figura siguiente:

Figura 2.2 Pin-out de la Práctica 1¶

Para asignar los pines de la tarjeta utilizaremos la herramienta de Pin-Planner. En este diseño requeriremos tres interruptores de entrada (una para cada entrada) y un led de salida, siguiendo la siguiente tabla:

señal |

Conectada a: |

PIN |

I/O Standard |

|---|---|---|---|

x_in |

Slide Switch[2] |

PIN_D12 |

3.3-V LVTTL |

y_in |

Slide Switch[1] |

PIN_C11 |

3.3-V LVTTL |

z_in |

Slide Switch[0] |

PIN_C10 |

3.3-V LVTTL |

f_out |

LED[0] |

PIN_A8 |

3.3-V LVTTL |

Abrir el Pin Planner: Assignments > Pin Planner.

Inicialmente aparecerán todas las entradas del circuito en la columna de «Node Name». Deben rellenarse para cada uno de las entradas los campos «Location» y el de «I/O Standard».

Para escribir el pin simplemente se debe escribir su letra y número en la columna «Location». Por ejemplo, para la entrada x simplemente es necesario escribir en su celda: D12.

La selección del «I/O Standard» se hace seleccionando la opción «3.3-V LVTTL» en cada una de las celdas.

El resultado final debe ser el siguiente:

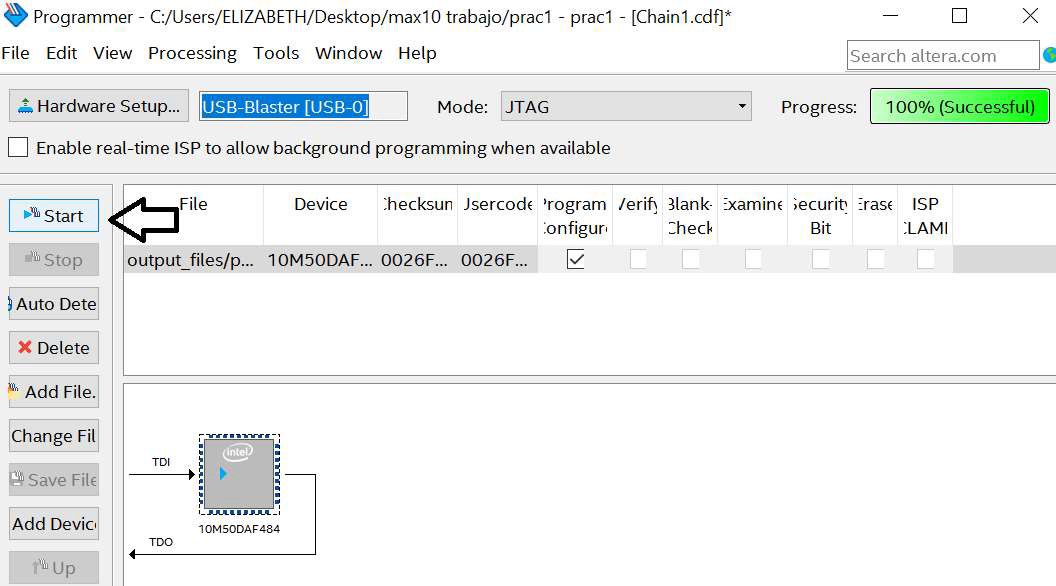

2.3.8. Programar el diseño en la Tarjeta DE10-Lite¶

Conectar la tarjeta DE10-Lite al PC a través del cable USB.

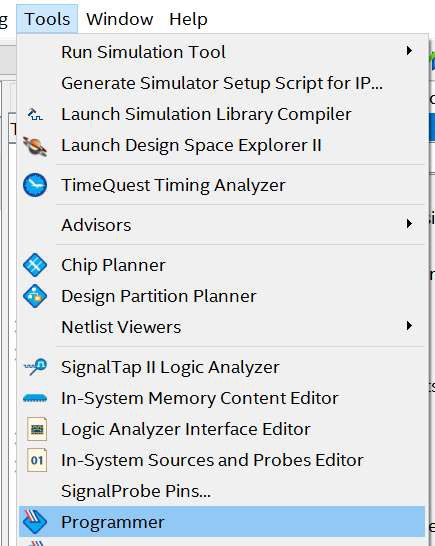

Para abril el programador usamos los menús Tools > Programmer.

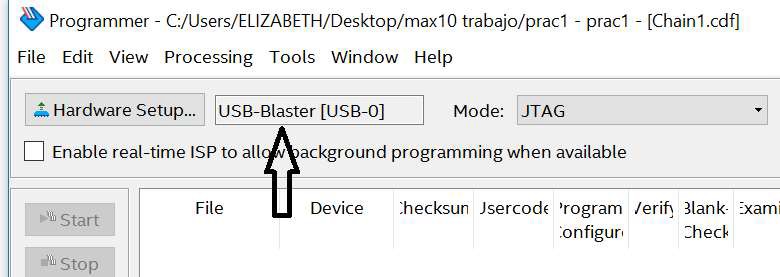

Si en la casilla «Hardware Setup» aparece «No Hardware» hacer click en «Hardware Setup» y seleccionar «USB blaster» en la ventana emergente y luego «Close».

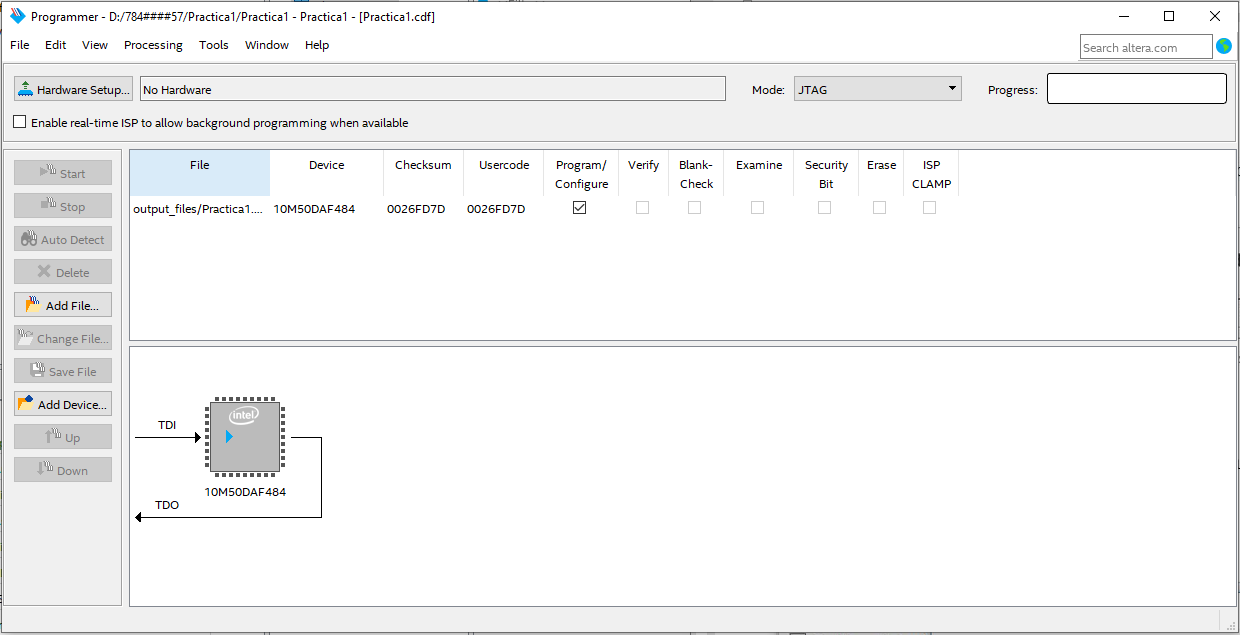

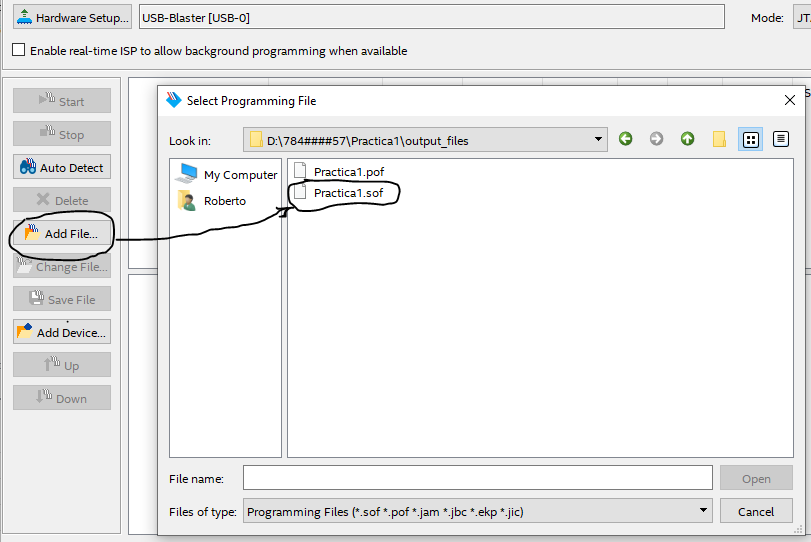

Hacer click sobre el circuito integrado que aparece dibujado en la ventana principal y luego en el menú de la izquierda Delete.

Entonces seleccionamos en el menú de la izquierda Add File, aparece otra ventana de dialogo, y escogemos «output files».

Seleccionar el fichero Practica2.sof y OPEN

Finalmente seleccionar en el menú de la izquierda «Start» y se observará un color verde de porcentaje de descarga, cuando indique 100% la programación ha terminado con éxito.

Ya se puede probar el diseño en la tarjeta DE10-Lite moviendo los interruptores 0 (z), 1 (y) y 2 (z), viendo el resultado en el LED0 (f) según indica la Figura 2.2. para comprobar el funcionamiento correcto introduzca todos los valores posibles en las entradas para ver que el resultado es el esperado según la siguiente tabla de verdad:

Cerrar el Programmer. No guardar los cambios.

Cerrar el QuartusII.

2.3.9. Resumen¶

En este tutorial se ha presentado el flujo de diseño de circuitos digitales usando Quartus II. A continuación, se resume brevemente el contenido de este tutorial, incluyendo los números de las secciones donde se pueden encontrar los detalles relativos a cada una de las etapas del flujo de diseño.

El primer paso es crear un proyecto en Quartus II, especificando la información sobre la placa de desarrollo que se va a emplear (Abrir QuartusII y crear un proyecto).

A continuación, se realiza la descripción del circuito (Realizar la captura de esquemas del diseño). Aunque en este tutorial se ha descrito el circuito usando un esquemático, lo más común es emplear ficheros VHDL.

La compilación del diseño (Compilar el diseño) permitirá comprobar que la descripción no tiene errores y sintetizará lógicamente el circuito para implementarlo en la FPGA MAX10 de Altera.

En este punto disponemos de una descripción de un circuito, y se ha de verificar mediante simulación que el circuito se comporta tal y como debería (Simulación del diseño con Modelsim-Altera). En este caso, se comprueba que se cumple la tabla de verdad, introduciendo las combinaciones posibles de las entradas, y verificando que las salidas se corresponden con las de la tabla de verdad. Si en este paso se detectara que el circuito no cumple con las especificaciones, se deberán realizar los cambios oportunos en la descripción del diseño hasta que se verifique que el funcionamiento es el correcto.

Una vez se ha comprobado el correcto funcionamiento del circuito diseñado, el último paso del flujo de diseño es la programación de la placa DE10-Lite. Para ello, en primer lugar se declarar o se deberá crear un circuito que constituya el top level (Crear el diseño jerárquico top-level), y asignar las entradas y salidas del circuito a los pines correspondientes de la tarjeta (Asignación de pines del diseño). Se configurará la FPGA con nuestro diseño mediante la programación de la tarjeta (Programar el diseño en la Tarjeta DE10-Lite).

Finalmente, actuando sobre los pines de la placa, se comprueba (valida) el funcionamiento del diseño.