1. Simulación de descripciones VHDL en el entorno Eda_Playground¶

1.1. Presentación¶

En un tutorial previo se ha visto como utilizar EDA playground para hacer la descripción y simulación (verificación) de un sumador de enteros. Dado que en Electrónica Digital se deben usar las librerías de std_logic, en este anexo se explicará como siimular un diseño digital, lo que será útil para la realización del trabajo previo en muchas de las prácticas. En concreto se mostrará lo siguiente:

Como realizar la descripción de un diseño en el entorno EDA playground (https://www.edaplayground.com/). EDA Playground incluye la herramienta EPWave que permiten ver las formas de onda.

Comprobar la sintaxis de la descripción con la herramienta VHDL-tool (https://www.vhdltool.com/tryit).

Generar un esqueleto de un banco de pruebas (testbench) con la herramienta Testbench Generator (https://vhdl.lapinoo.net/testbench/).

1.2. Objetivos¶

Hacer una descripción VHDL y un banco de pruebas.

Utilizar el entorno EDA Playground para hacer una simulación funcional.

Comprobar el correcto funcionamiento a través de la representación de formas de onda.

1.3. Introducción¶

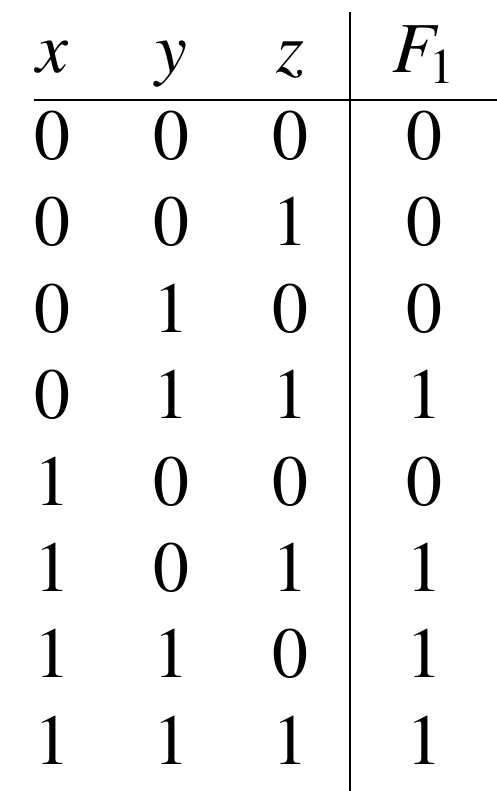

Como ejemplo vamos a utilizar la misma función que en la Práctica 1. Es decir, una función f de tres entradas (x, y, z) que viene definida por la siguiente expresión de suma de productos:

Especificación funcional:

Entradas: \(x, y, z \in \{0, 1\}\).

Salida: \(f \in \{0, 1\}\).

Función: \(x · y + x · y^\prime · z + x^\prime · y · z\).

Esta función se puede representar mediante su tabla de verdad.

La descripción de esta función en VHDL es la siguiente:

-- Electrónica Digital 2º curso EITE

-- Tema 2: Especificación de sistemas combinacionales

-- Función xy + xy'z + x'yz en VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY funcion IS

PORT(x_in : IN STD_LOGIC;

y_in : IN STD_LOGIC;

z_in : IN STD_LOGIC;

f_out: OUT STD_LOGIC );

END funcion;

ARCHITECTURE funcional OF funcion IS

BEGIN

-- f_out = x_in·y_in + x_in·y_in'·z_in + x_in'·y_in·z_in

f_out <= (x_in AND y_in) OR

(x_in AND (NOT y_in) AND z_in) OR

((NOT x_in) AND y_in AND z_in);

END funcional;

La verficación (comprobación del buen funcionamiento) de esta descripción VHLD se puede realizar utilizando el siguiente banco de prueba (testbench):

-- Electrónica Digital 2º curso EITE

-- Tema 2: Especificación de sistemas combinacionales

-- Función xy + xy'z + x'yz en VHDL

-- Banco de pruebas (testbench)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY tb_funcion IS

END tb_funcion;

ARCHITECTURE tb OF tb_funcion IS

COMPONENT funcion IS

PORT (x_in : IN STD_LOGIC;

y_in : IN STD_LOGIC;

z_in : IN STD_LOGIC;

f_out : OUT STD_LOGIC);

END COMPONENT;

SIGNAL x : STD_LOGIC := '0'; --cada señal del componente

SIGNAL y : STD_LOGIC := '0'; --debe tener una señal en el

SIGNAL z : STD_LOGIC := '0'; --testbench

SIGNAL f : STD_LOGIC;

--la señal entradas permitirá utilizar las entradas en conjunto

SIGNAL entradas : STD_LOGIC_VECTOR (2 DOWNTO 0);

BEGIN

--se intancia el componente como dut (Device Under Test)

dut : funcion

PORT MAP (x_in => x,

y_in => y,

z_in => z,

f_out => f);

--cada entrada corresponderá a un bit del vector "entradas"

x <= entradas(2);

y <= entradas(1);

z <= entradas(0);

--el siguiente proceso asignará un valor a las entradas

PROCESS

BEGIN

entradas <= "000";

WAIT FOR 20 ns;

entradas <= "001";

WAIT FOR 20 ns;

entradas <= "010";

WAIT FOR 20 ns;

entradas <= "011";

WAIT FOR 20 ns;

entradas <= "100";

WAIT FOR 20 ns;

entradas <= "101";

WAIT FOR 20 ns;

entradas <= "110";

WAIT FOR 20 ns;

entradas <= "111";

WAIT FOR 20 ns;

WAIT;

END PROCESS;

END tb;

Como se observa el testbench únicamente introuduce en las entradas las combinaciones posibles según la tabla de verdad. La salida (f_out) debe coincidir para cada una de las combinaciones con el valor indicado en la tabla de verdad.

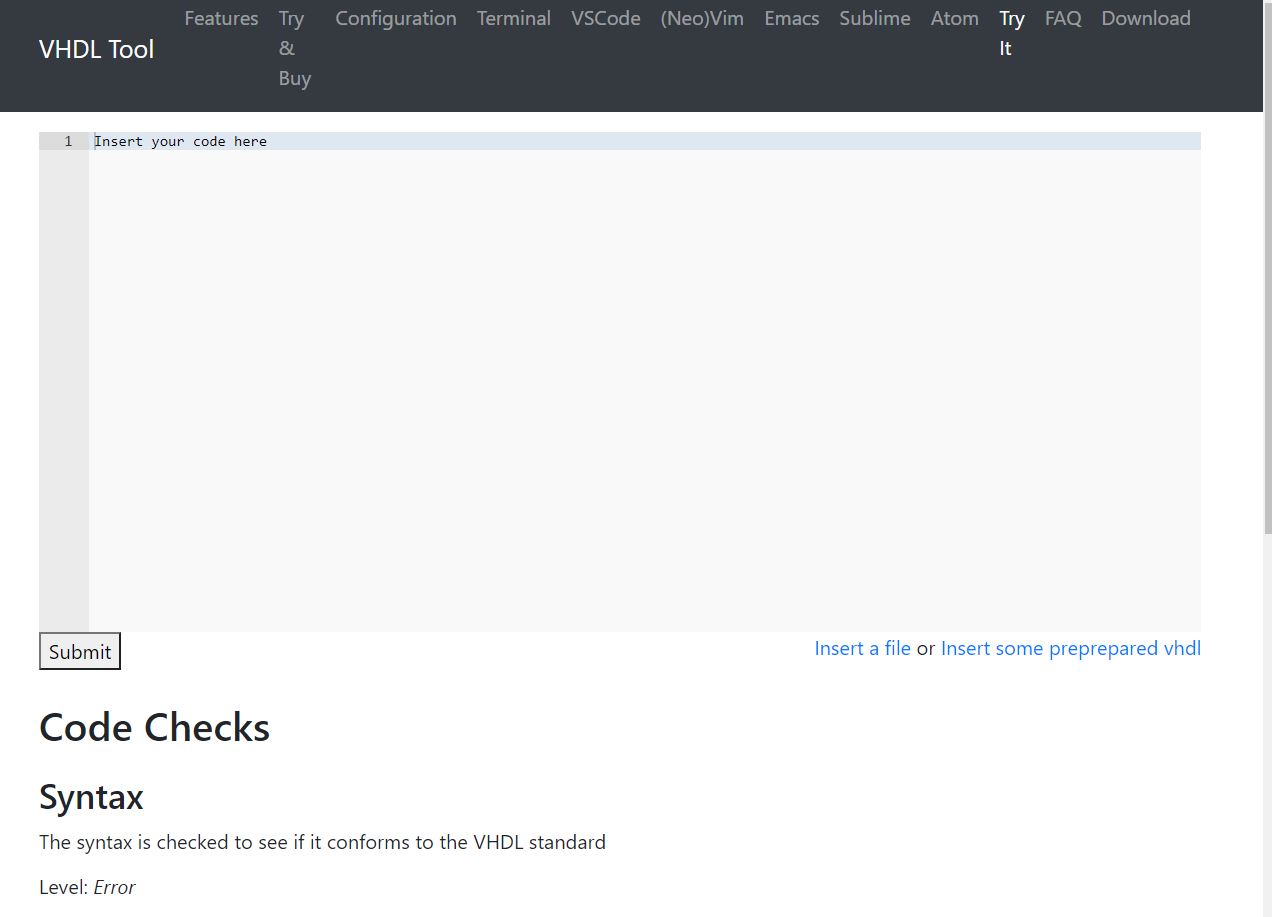

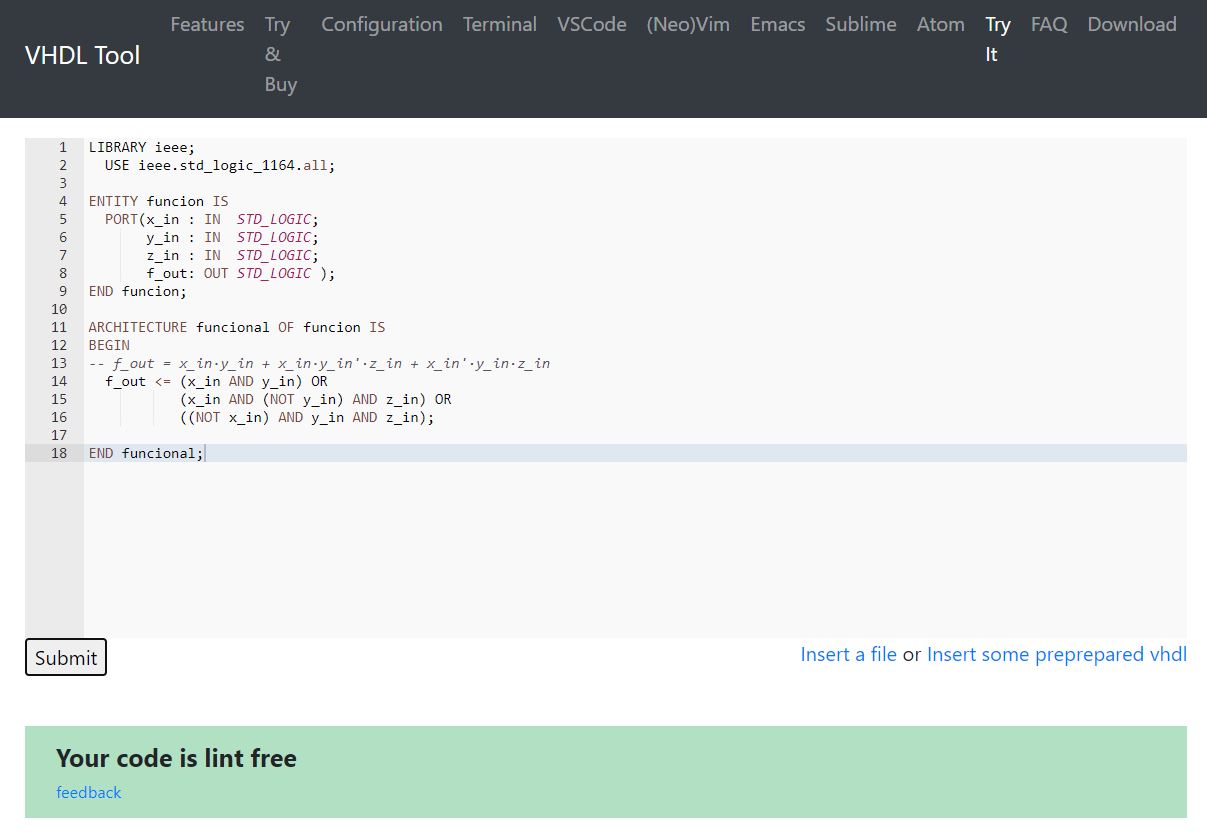

1.4. Comprobación de errores de sintaxis¶

Antes de iniciar la simulación en Eda Playground comprobaremos que no existen errores de sintaxis en la descripción VHDL.

Entrar en la página web VHDL-tool (https://www.vhdltool.com/tryit). Aparecerá la siguiente página web:

Copiar la descripción VHDL ( Listado 1.1) y pegarla en la ventana VHDL-tool y picar en submit. El resultado debe ser que no hay errores. Si los hubiera hay que corregirlos.

Nota

Hay que asegurarse de borrar el texto que aparece inicialmente en la ventana.

realizar el mismo procedimiento con la descripción que contiene el testbench del diseño ( Listado 1.2).

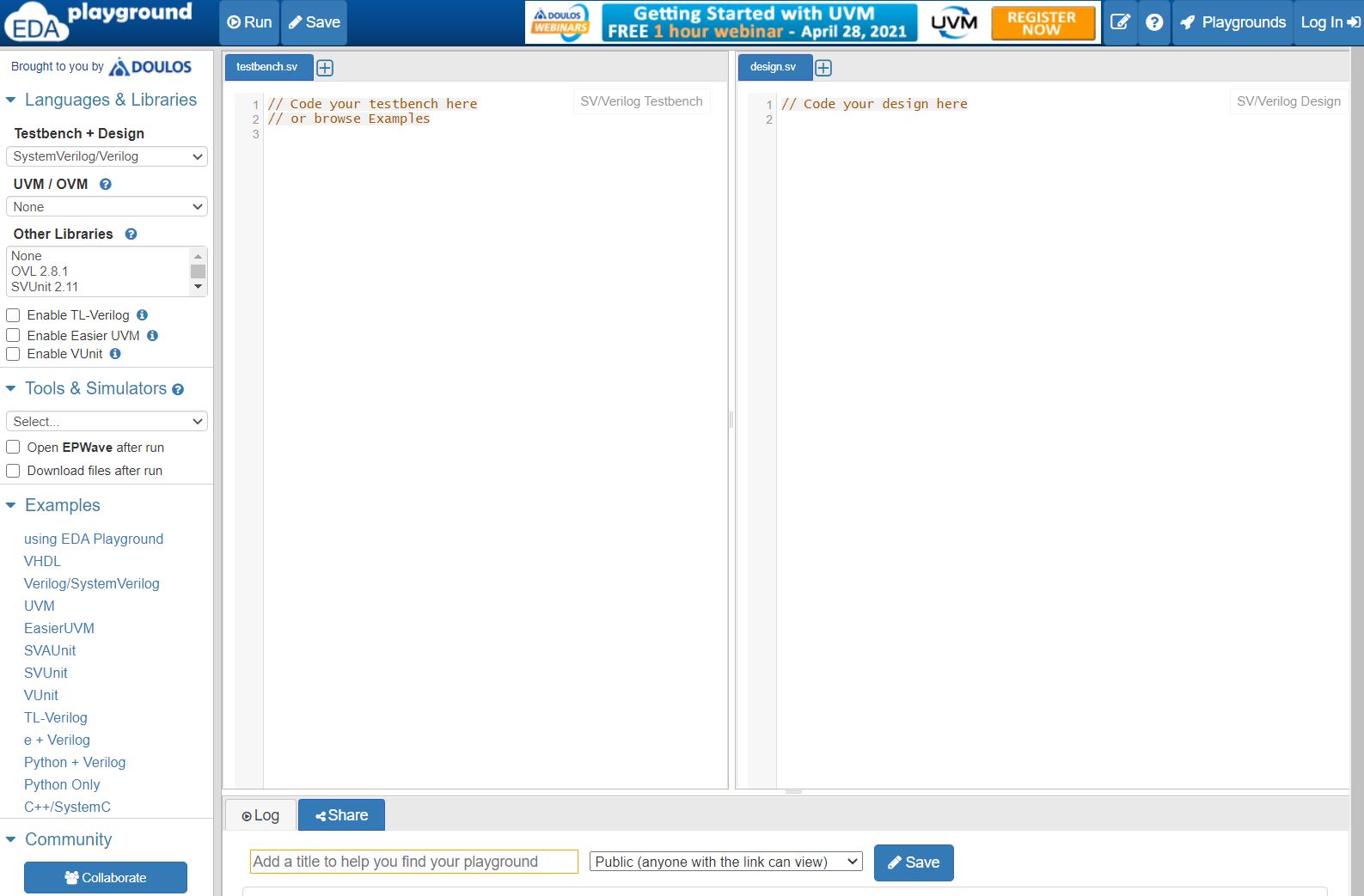

1.5. Entorno Eda Playground¶

Una vez que hemos comprobado la sintaxis de la descripción y del testbench pasaremos a hacer la simulación en Eda Playground.

Entrar en el entorno EDA playground (https://www.edaplayground.com/). Se mostrará la siguiente página web:

Es necesario crear una cuenta ya que a la hora de hacer las simulaciones hará falta guardar los diseños. Seguir todo el proceso y entrar en la página que se muestra en la figura del punto anterior.

Copiar la descripción VHDL ( Listado 1.1) en la ventana de la derecha (actualmente aparece etiquetada como design.sv) y copiar el testbench del diseño ( Listado 1.2) en la ventana de la izquierda (actualmente aparece marcada como testbench.sv).

En el menú de la parte superior izquierda, picar en Save. Esta acción guardará el diseño en la librería de diseños, a la cual puede accederse picando en el menú superior de la derecha Playground.

En la ventana de la izquierda, que permite seleccionar herramientas y opción hacer las siguientes selecciones:

Pestaña Testbench + Design elegir VHDL.

Pestaña Libraries elegir none.

Pestaña Top entity indicar el nombre de la entidad de la descripción del testbench, en este caso tb_funcion.

Pestaña Tools & Simulators seleccionar la herramienta Aldec Riviera Pro 2020.04.

El resto de opciones hay que dejarlas como están.

Finalmente marcar la casilla: Open EPWave after run.

Picar en Run que se encuentra en el menú superior derecho del EDA playground.

Una vez realizado este proceso en la ventana del log aparecerán todas las acciones que ha realizado en software de Aldec Riviera. El listado debe ser algo parecido a esto:

[2021-04-12 11:59:06 EDT] vlib work && vcom '-2019' '-o' design.vhd testbench.vhd && vsim -c -do "vsim tb_funcion; vcd file dump.vcd; vcd add -r sim:/*; run -all; exit"

VSIMSA: Configuration file changed: '/home/runner/library.cfg'

ALIB: Library "work" attached.

work = /home/runner/work/work.lib

Aldec, Inc. VHDL Compiler, build 2020.04.130

VLM Initialized with path: "/home/runner/library.cfg".

DAGGEN WARNING DAGGEN_0523: "The source is compiled without the -dbg switch. Line breakpoints and assertion debug will not be available."

COMP96 File: design.vhd

COMP96 Compile Entity "funcion"

COMP96 Compile Architecture "funcional" of Entity "funcion"

COMP96 File: testbench.vhd

COMP96 Compile Entity "tb_funcion"

COMP96 Compile Architecture "tb" of Entity "tb_funcion"

COMP96 Top-level unit(s) detected:

COMP96 Entity => tb_funcion

COMP96 Compile success 0 Errors 0 Warnings Analysis time : 20.0 [ms]

# Aldec, Inc. Riviera-PRO version 2020.04.130.7729 built for Linux64 on June 10, 2020.

# HDL, SystemC, and Assertions simulator, debugger, and design environment.

# (c) 1999-2020 Aldec, Inc. All rights reserved.

# ELBREAD: Elaboration process.

# ELBREAD: Elaboration time 0.0 [s].

# KERNEL: Main thread initiated.

# KERNEL: Kernel process initialization phase.

# ELAB2: Elaboration final pass...

# ELAB2: Create instances ...

# KERNEL: Time resolution set to 1ps.

# ELAB2: Create instances complete.

# SLP: Started

# SLP: Elaboration phase ...

# SLP: Elaboration phase ... skipped, nothing to simulate in SLP mode : 0.0 [s]

# SLP: Finished : 0.0 [s]

# ELAB2: You do not have a license to run VHDL performance optimized simulation. Contact Aldec for ordering information - sales@aldec.com.

# ELAB2: Elaboration final pass complete - time: 0.0 [s].

# KERNEL: Warning: You are using the Riviera-PRO EDU Edition. The performance of simulation is reduced.

# KERNEL: Warning: Contact Aldec for available upgrade options - sales@aldec.com.

# KERNEL: Kernel process initialization done.

# Allocation: Simulator allocated 5401 kB (elbread=427 elab2=4831 kernel=143 sdf=0)

# KERNEL: ASDB file was created in location /home/runner/dataset.asdb

# KERNEL: PLI/VHPI kernel's engine initialization done.

# PLI: Loading library '/usr/share/Riviera-PRO/bin/libsystf.so'

# KERNEL: Simulation has finished. There are no more test vectors to simulate.

# VSIM: Simulation has finished.

Finding VCD file...

./dump.vcd

[2021-04-12 11:59:08 EDT] Opening EPWave...

Done

Automáticamente se abrirá la ventana de presentación de la simulación.

1.5.1. Entorno EP Wave¶

El EP Wave es una ventana emergente, que tendrá un aspecto similar al de la siguiente figura:

Los menús disponibles son los siguienes:

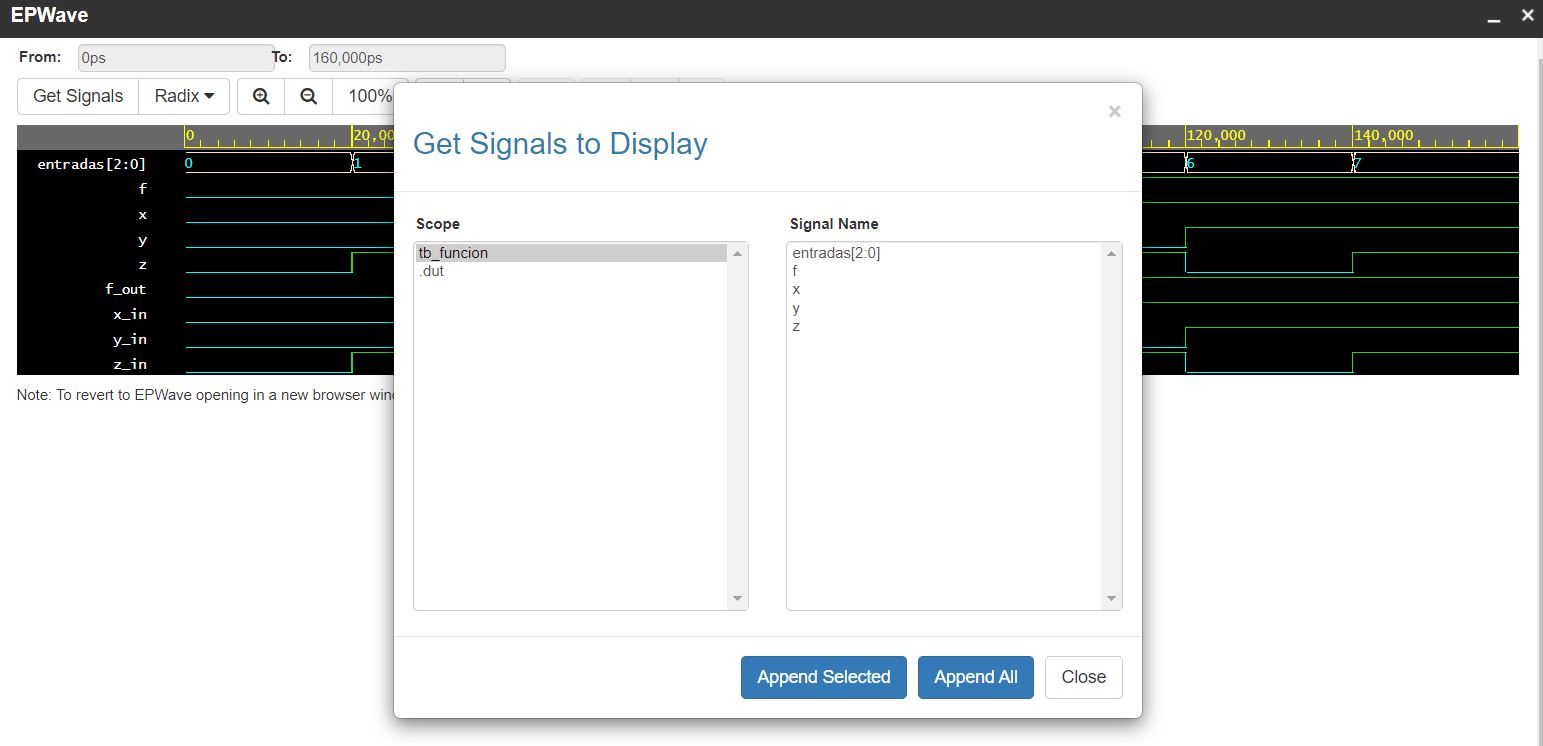

Get Signals: Permite incorporar a la EP Wave las señales y puertos de entrada salida del diseño mediante una ventana emergente.

Nota

Normalmente solo se requiere seleccionar aquellas señales que corresponden al testbench.

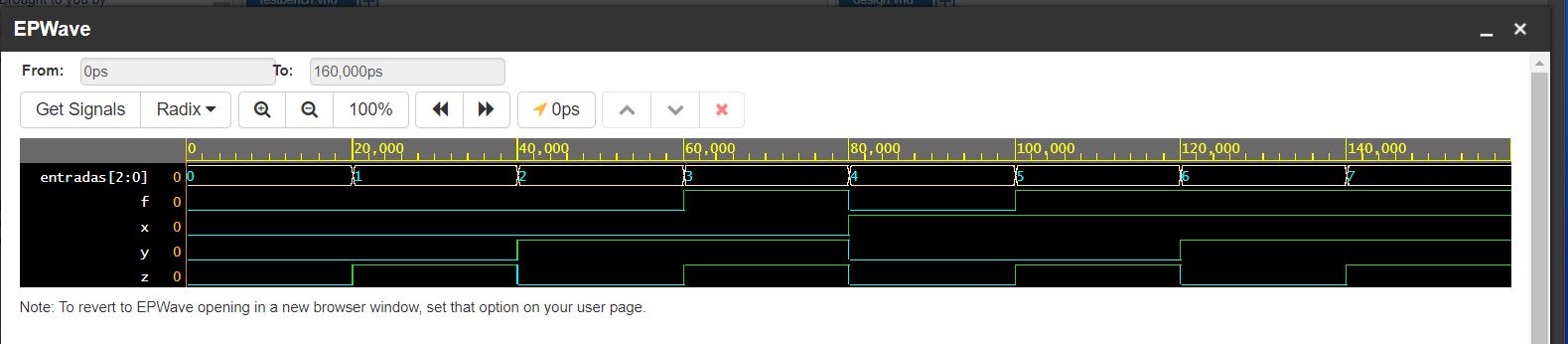

Seleccionamos todas las señales del testbench y las incoporamos.

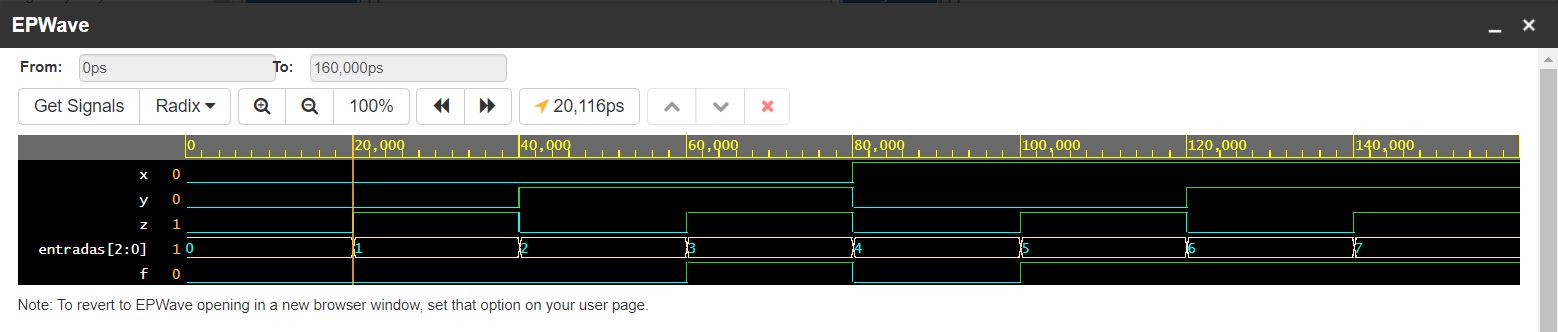

Radix: Nos permitirá seleccionar si la información se representa en Binario o en Hexadecimal.

Zoom Permite aumentar y reducir la escala de tiempos.

Scroll Left y Scroll Right: permite mover la simulación a izquierda o derecha

La fecha arriba y abajo permite mover las señales arriba o abajo para comprender mejor la simulación.

Marca de borrado. Permite eliminar una señal de la representación EP Wave.

Colocando la información como se observa en la figura siguiente podremos observar que el funcionamiento es correcto y sigue exactamente lo que indica la tabla de verdad.