Un trabajo sobre UVM del IUMA premiado a nivel nacional

El trabajo Fin de Grado titulado “Desarrollo de un testbench UVM integrando IP de verificación de Mentor Graphics (QVIP)” del estudiante Álvaro José Moreno Florido y desarrollado en el Instituto Universitario de Microelectrónica Aplicada (IUMA) ha sido galardonado con el segundo premio en la XV edición de los Premios Futuro de las Telecomunicaciones, en la categoría a los mejores Trabajos Fin de Grado realizados por Graduados/as en Ingeniería de Telecomunicación en España en el año 2021. Este Trabajo Fin de Grado ha sido desarrollado bajo la dirección del profesor Dr. Valentín de Armas Sosa y Dr. Félix Bernardo Tobajas Guerrero de la División DSI.

En la actualidad, la etapa de verificación ocupa un lugar imprescindible para el desarrollo de sistemas hardware digitales. Debido al aumento de la demanda de los sistemas electrónicos y a la mejora de la tecnología asociada al sector de la electrónica, los sistemas desarrollados se diseñan con una estructura de mayor complejidad, ya que se integra un mayor número de componentes y, además, se incrementan las funcionalidades asociadas a dicho sistema. Por estos motivos, las tareas de verificación son complejas y consumen mucho tiempo a lo largo del proceso descrito. Para solventar estos inconvenientes, surge la metodología Universal Verification Methodology (UVM), que se basa en el lenguaje de descripción y de verificación hardware SystemVerilog.

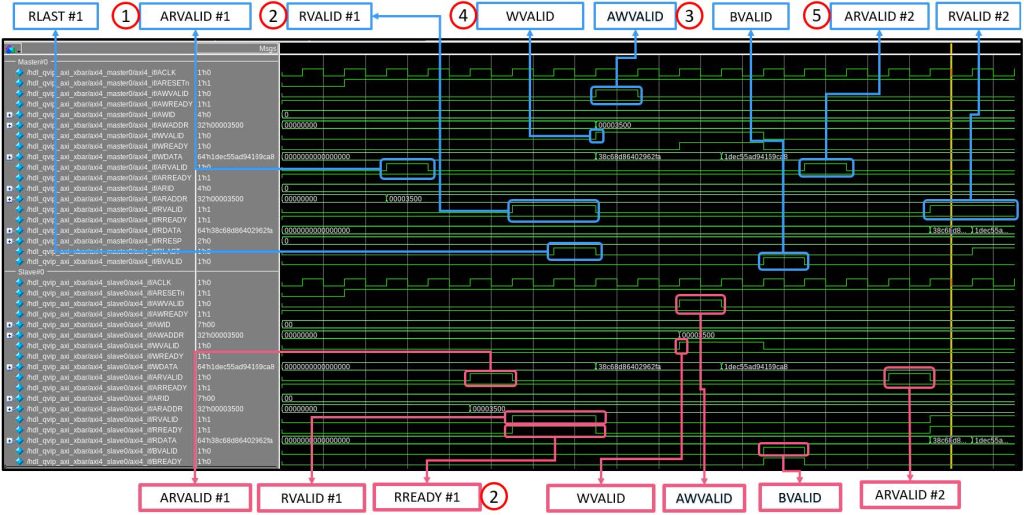

El objetivo principal del presente Trabajo Fin de Grado (TFG) consiste en el diseño de un testbench UVM usando un IP de verificación de Mentor Graphics, a Siemens Business. Este módulo IP está desarrollado con la metodología UVM y utiliza el protocolo de comunicación AMBA AXI4 y es totalmente configurable. En primer lugar, se efectuará una etapa de estudio donde se profundizará en el funcionamiento del protocolo AXI4 y en los conceptos necesarios de la metodología UVM. En segundo lugar, se estudiará el IP de verificación de Mentor Graphics y la herramienta QVIP configurator, la cual creará el entorno de verificación UVM que se utilizará para la estimulación del módulo IP que se desea verificar. Tras esto, se estudiará en profundidad el dispositivo a verificar (DUV), para entender su funcionamiento. Finalmente, se diseñará un testbench UVM que verificará el correcto comportamiento de dicho sistema.

Para más información:

https://www.ulpgc.es/noticia/2022/03/16/cuatro-egresados-eite-premios-nacionales-xv-edicion-premios-futuro

https://www.telecos.zone/index.php/actualidad/noticias-coitt/909-estos-son-los-ganadores-de-los-premios-coitt-2021-futuro-de-las-telecomunicaciones