3.1.4. Tema 6: Problemas de aula¶

3.1.4.1. Análisis de sistemas secuenciales¶

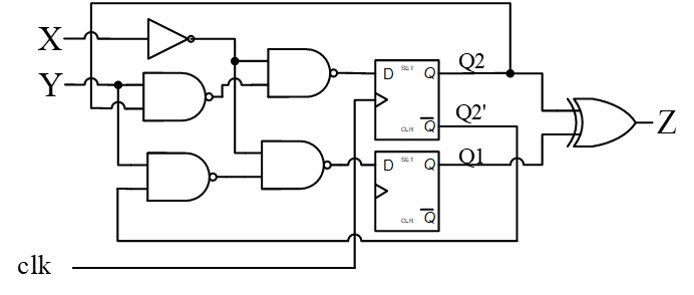

El circuito de la siguiente figura representa un autómata de Moore, con dos entradas (X, Y) y una salida (Z). Se pide:

Analizar el autómata y obtener su grafo de estados.

Realizar el código VHDL que lo representa, definiéndolo en tres procesos diferentes.

3.1.4.2. Síntesis de sistemas secuenciales¶

Realizar un autómata de Mealy de una entrada (x) y una salida (z) que detecte el siguiente patrón:

P = (1,0,1,1); n = 4

Realizar el grafo de estados.

Realizar la tabla de estados-salida.

Tabla de transición/ salida con codificación GRAY.

Ecuaciones de transición/salida.

Implementación del circuito con Flips-Flops tipo D.

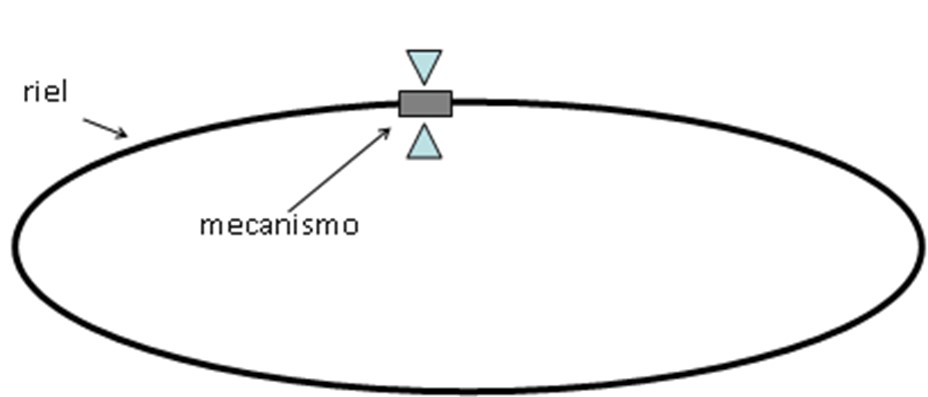

Diseñar un autómata de Moore que controle un mecanismo que se desplaza en el sentido de la agujas de reloj por un riel elipsoidal a partir de la posición A en la cual existe un sensor que detecta su presencia.

El movimiento se controla mediante un pulsador P de la siguiente manera:

Cuando el mecanismo se encuentre en A y se pulse P, se inicia el movimiento en sentido de las agujas del reloj.

Si no se vuelve a pulsar P el mecanismo da dos vueltas y se detiene en A; es decir, se detiene la segunda vez que pasa por A.

Cuando el mecanismo se encuentra moviéndose, si se pulsa P el móvil se detiene y al pulsarlo de nuevo inicia la marcha y se detiene en A independientemente del número de vueltas que haya dado.

Si justo al completar la segunda vuelta se pulsa P el mecanismo inicia inmediatamente el proceso de girar las dos vueltas, tal como se ha especificado en los puntos 1 y 2 anteriores.

Nota

Un pulsador al ser presionado da un pulso que pasa al valor uno y luego a cero independientemente del tiempo que se tenga pulsado.

Realizar el grafo de estados.

Minimizar los estados.

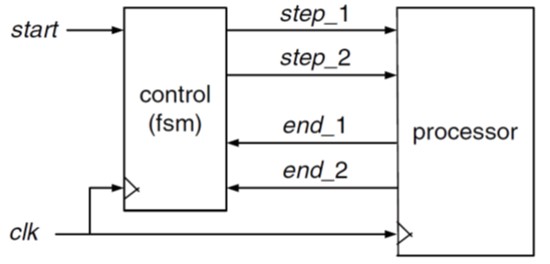

La unidad de control es una máquina de estados finitos cuyas entradas son las señales de estado end_1 y end_2 y la señal de inicio start, y cuyas salidas son las señales de control step_1 y step_2. Realizar la unidad de control como un autómata de Moore con el siguiente funcionamiento:

Cuando se activa la señal start (start = 1), el autómata activará el primer paso del proceso (step_1 = 1) se pone alta y el procesador comienza la ejecución del primer paso.

Cuando el procesador termina el primer paso, activará la señal de estado end_1 (end_1 = 1). El autómata desactivará la señal step_1 (step_1 = 0), y activará la señal step_2 (step_2 = 1), y el procesador desactivará la señal de estado end_1 (end_1 = 0) y comienza a ejecutar el segundo paso del programa.

Cuando se completa el segundo paso, el procesador activará la señal de estado end_2 (end_2 = 1). El autómata desactivará la señal step_2 (step_2 = 0) y el procesador desactivará la señal de estado end_2 (end_2 = 0), y el circuito de control pasará al inicio.

Realizar el grafo de estados.

Realizar la descripción en VHDL.