6.3. Práctica 1: Simulación de descripciones VHDL en el entorno Eda Playground¶

6.3.1. Duración¶

Esta práctica tendrá una duración de 2 horas en el laboratorio (1 sesión).

6.3.2. Objetivos¶

Iniciar la cuenta en los ordenadores del Laboratorio de ASICs y Sistemas Digitales para realizar las prácticas de la asignatura.

Abrir una cuenta en el entorno EDA Playground.

Hacer una descripción VHDL y un banco de pruebas.

Utilizar el entorno EDA Playground para hacer una simulación funcional.

Comprobar el correcto funcionamiento a través de la representación de formas de onda y con un banco de pruebas que permita salida mediante texto.

6.3.3. Introducción¶

En esta práctica se explicará como usar EDA Playground para hacer una simulación de una descripción VHDL. Todo el proceso se realizará en web por lo que puede ser realizado desde cualquir punto con acceso a internet. En esta práctica se mostrará lo siguiente:

Como realizar la descripción de un diseño en el entorno EDA playground (https://www.edaplayground.com/).

Comprobar la sintaxis de la descripción con la herramienta VHDL-tool (https://www.vhdltool.com/tryit).

Hacer la verificación de la descripción VHDL mediante un banco de pruebas que permita ver las salidas mediante la herramienta EPWave incluida en EDA Playground.

Hacer la verificación de la descripción VHDL mediante un banco de pruebas que permita ver mensajes de salida en la consola de EDA Playground.

6.3.4. Descripción de la Práctica¶

Como ejemplo vamos a realizar la descripción de un sumador de dos dígitos que se presenta en las transparencias de teoría del Tema 1 de la asignatura (transparencia 19). Todos los datos usados son enteros (INTEGER) por lo que no necesitaremos librerías específicas en VHDL. La descripción en VHDL de esta función es la siguiente:

-- Electronica Digital, curso 2

-- EITE-ULPGC

-- VHDL del sumador de enteros de dos digitos (funcional)

ENTITY sumador2digitos IS

PORT( x0_in : IN INTEGER RANGE 0 TO 9;

x1_in : IN INTEGER RANGE 0 TO 9;

y0_in : IN INTEGER RANGE 0 TO 9;

y1_in : IN INTEGER RANGE 0 TO 9;

z0_out : OUT INTEGER RANGE 0 TO 9;

z1_out : OUT INTEGER RANGE 0 TO 9;

z2_out : OUT INTEGER RANGE 0 TO 9);

END sumador2digitos;

ARCHITECTURE funcional OF sumador2digitos IS

SIGNAL s0, s1 : INTEGER RANGE 0 TO 99;

SIGNAL carry : INTEGER RANGE 0 TO 1;

CONSTANT diez : INTEGER :=10;

CONSTANT uno : INTEGER := 1;

CONSTANT cero : INTEGER := 0;

BEGIN

s0 <= x0_in + y0_in;

s1 <= x1_in + y1_in + carry;

PROCESS (s0)

BEGIN

IF (s0 >= diez) THEN

z0_out <= s0 - diez;

carry <= uno;

ELSE

z0_out <= s0;

carry <= cero;

END IF;

END PROCESS;

PROCESS(s1)

BEGIN

IF (s1 >= diez) THEN

z1_out <= s1 - diez;

z2_out <= uno;

ELSE

z1_out <= s1;

z2_out <= cero;

END IF;

END PROCESS;

END funcional;

6.3.5. Trabajo previo¶

Esta práctica no tiene trabajo previo.

6.3.6. Trabajo de laboratorio¶

6.3.6.1. Establecer la cuenta en el Laboratorio¶

Siguiendo las instrucciones indicadas en la sección Instrucciones Generales iniciar la cuenta en el Laboratorio. Se deben realizar los siguientes pasos:

Iniciar la cuenta.

Cambiar la contraseña.

Registrar la cuenta.

Una vez iniciada la sesión en el PC del Laboratorio se podrá realizar la práctica.

6.3.6.2. Comprobación de errores de sintaxis¶

Antes de iniciar la simulación en Eda Playground comprobaremos que no existen errores de sintaxis en la descripción VHDL.

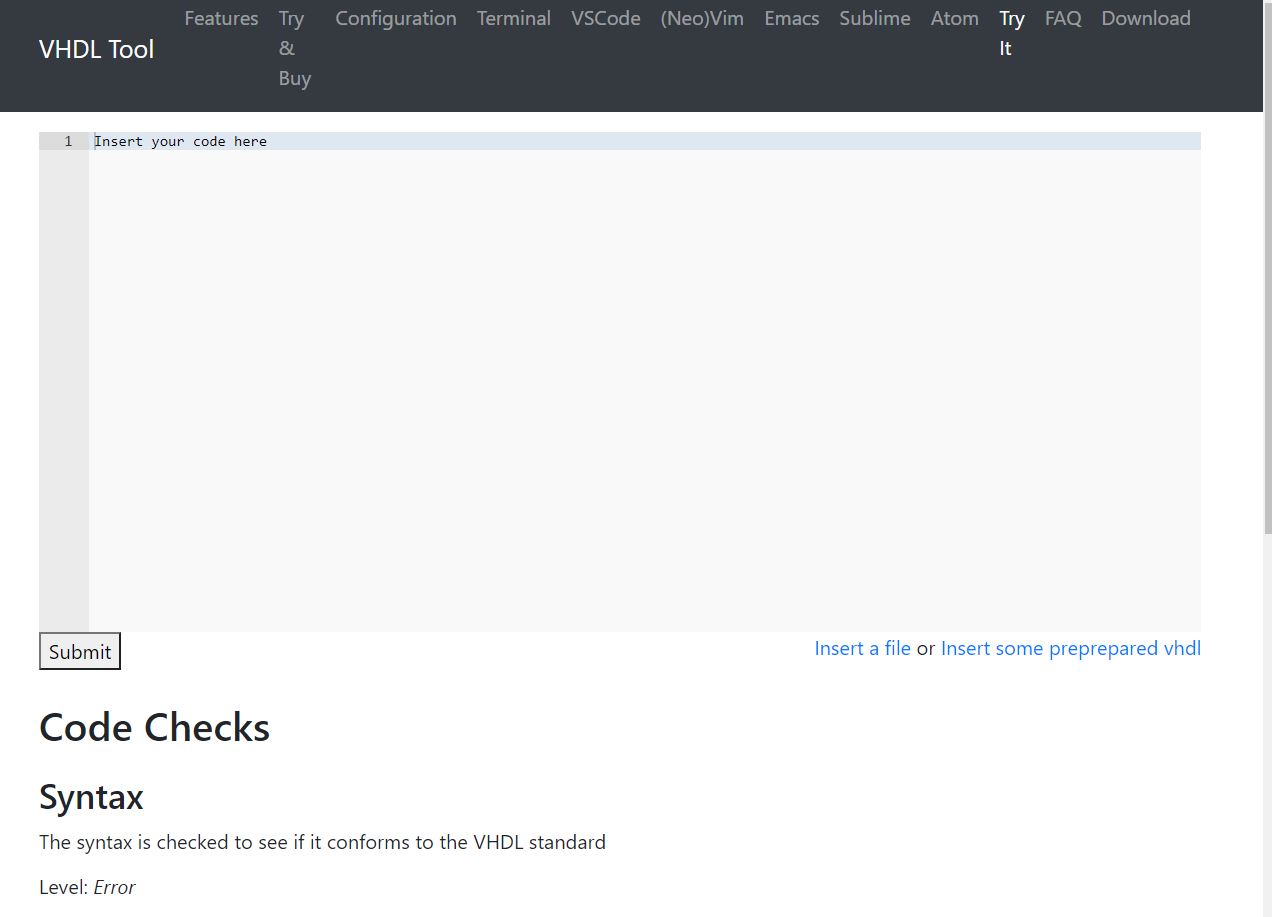

Entrar en la página web VHDL-tool (https://www.vhdltool.com/tryit). Aparecerá la siguiente página web:

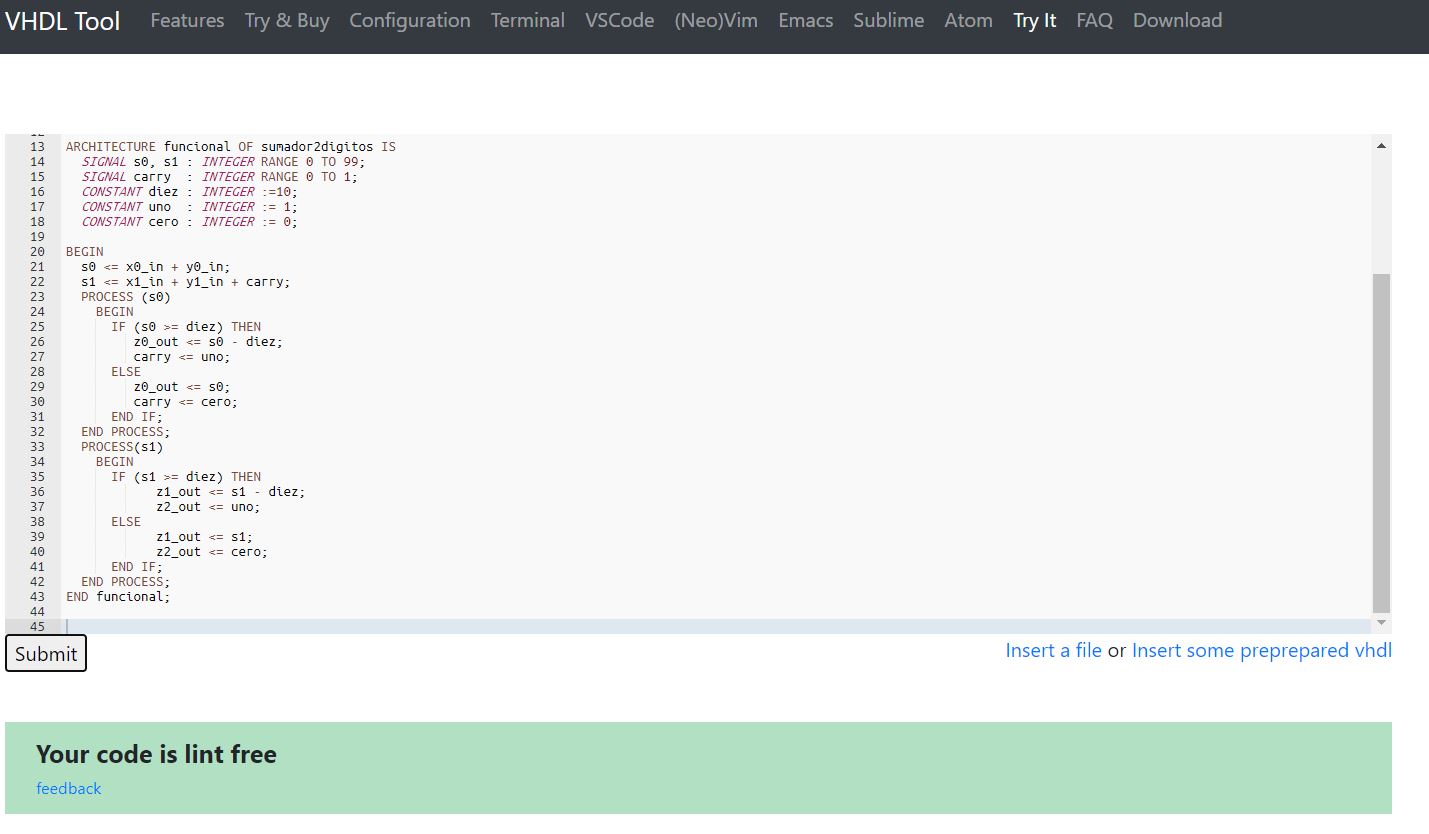

Copiar la descripción VHDL (Listado 6.1) y pegarla en la ventana VHDL-tool y picar en submit. El resultado debe ser que no hay errores. Si los hubiera hay que corregirlos.

Nota

Hay que asegurarse de borrar el texto que aparece inicialmente en la ventana.

6.3.6.3. Entorno Eda Playground¶

Una vez que hemos comprobado la sintaxis de la descripción VHDL pasaremos a hacer la simulación en Eda Playground.

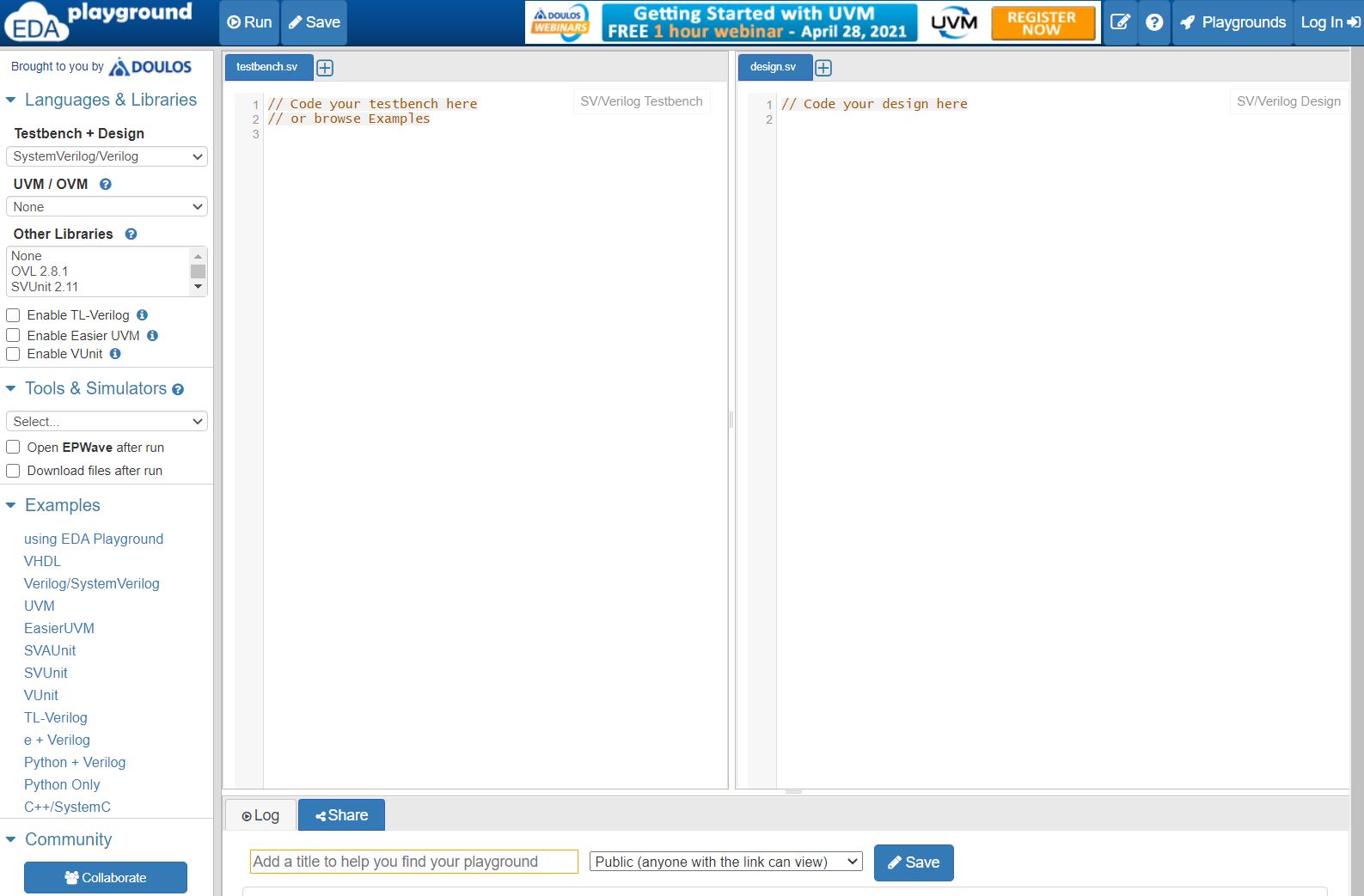

Entrar en el entorno EDA playground (https://www.edaplayground.com/). Se mostrará la siguiente página web:

Este entorno presenta cuatro botones en la parte superior cuya funcionalidad es la siguiente:

En la parte superior hay un menú sencillo con las opciones:

Run para realizar la simulación.

Save para guardar los diseños.

Copy para copiar los diseños.

Playgrounds, lugar donde se almacenan los diseños.

Login para registrse y hacer el login de usuario.

En la parte central derecha aparece una ventana etiquetada como design.sv y que incluye el texto Code your design here. En este ventana incluiremos la descripción VHDL.

En la parte central izquierda aparece una ventana etiquetada como testbench.sv y que incluye el texto Code your testbench here or browse Examples. En este ventana incluiremos el testbench.

En el lateral izquierdo aparecen las opciones del EDA playground que puede usarse para múltiples lenguajes.

En la parte central debajo aparece la ventana de consola en la que el entorno EDA playground nos informará de los procesos que realiza o servirá de ventana de mensajes.

Es necesario crear una cuenta ya que a la hora de hacer las simulaciones será necesario guardar los diseños. Picar en el menú login y realizar todo el proceso de registro y login.

6.3.6.3.1. Introducir el diseño y el testbench¶

Una vez realizado el login pasamos a introducir el diseño y el testbechn en EDA playground.

Copiar la descripción VHDL (Listado 6.1) en la ventana de la derecha (actualmente aparece etiquetada como design.sv).

Copiar el testbench del diseño (Listado 6.2) en la ventana de la izquierda (actualmente aparece marcada como testbench.sv).

La verificación (comprobación del buen funcionamiento) de esta descripción VHDL se puede realizar utilizando el siguiente banco de prueba (testbench):

-- Electronica Digital, curso 2 -- EITE-ULPGC -- Banco de pruebas (testbench) específico -- se definen las entradas que queremos probar --la entidad del testbench no lleva --ni entradas ni salidas entity sumador2digitos_tb is end sumador2digitos_tb; --la architectura definirá el test que se realice architecture tb of sumador2digitos_tb is --añadimos el componente que queremos probar component sumador2digitos is port ( x0_in : IN INTEGER RANGE 0 TO 9; x1_in : IN INTEGER RANGE 0 TO 9; y0_in : IN INTEGER RANGE 0 TO 9; y1_in : IN INTEGER RANGE 0 TO 9; z0_out : OUT INTEGER RANGE 0 TO 9; z1_out : OUT INTEGER RANGE 0 TO 9; z2_out : OUT INTEGER RANGE 0 TO 9); end component; --debemos declarar tantas señales como --entradas y salidas tenga el dut signal x0 : integer RANGE 0 TO 9; signal x1 : integer RANGE 0 TO 9; signal y0 : integer RANGE 0 TO 9; signal y1 : integer RANGE 0 TO 9; signal z0 : integer RANGE 0 TO 9; signal z1 : integer RANGE 0 TO 9; signal z2 : integer RANGE 0 TO 9; begin --se instancia el dispositivo bajo test (dut) dut : sumador2digitos port map (x0_in => x0, x1_in => x1, y0_in => y0, y1_in => y1, z0_out => z0, z1_out => z1, z2_out => z2); --se hace un proceso con los estímulos a las --entradas del dut stimuli : process begin --Empezamos con todas las entradas a 0 x0 <= 0; x1 <= 0; y0 <= 0; y1 <= 0; --Añadimos las operaciones a realizar wait for 10 ns; x0 <= 5; x1 <= 1; y0 <= 0; y1 <= 2; --el resultado debe ser 35 wait for 10 ns; x0 <= 9; x1 <= 0; y0 <= 1; y1 <= 1; --el resultado debe ser 20 wait for 10 ns; x0 <= 9; x1 <= 9; y0 <= 9; y1 <= 9; --el resultado debe ser 198 wait for 10 ns; --el ultimo wait detiene la ejecución de tb wait; end process; end tb;

Como se observa el testbench únicamente introduce en las entradas algunos valores para realizar su suma. Los resultados correctos se muestran en el mismo fichero del testbench como un comentario.

Para comprobar que este testbench no contiene errores, copiar la descripción VHDL del Listado 6.2 y pegarla en la ventana VHDL-tool y picar en submit. El resultado debe ser que no hay errores.

De vuelta en EDA playground, en el menú de la parte superior izquierda, picar en Save. Esta acción guardará el diseño en la librería de diseños, a la cual puede accederse picando en el menú superior de la derecha Playground.

En la ventana de la izquierda, que permite seleccionar herramientas y opción hacer las siguientes selecciones:

Pestaña Testbench + Design elegir VHDL.

Pestaña Libraries elegir none.

Pestaña Top entity indicar el nombre de la entidad de la descripción del testbench, en este caso sumador2digitos_tb.

Pestaña Tools & Simulators seleccionar la herramienta GHDL 0.37.

El resto de opciones hay que dejarlas como están.

Finalmente marcar la casilla: Open EPWave after run.

Picar en Run que se encuentra en el menú superior derecho del EDA playground.

Una vez realizado este proceso en la ventana de la consola (pestaña log) aparecerán todas las acciones que ha realizado el software de GHDL. El listado debe ser algo parecido a esto:

[2021-04-15 07:23:07 EDT] ghdl -i design.vhd testbench.vhd && ghdl -m sumador2digitos_tb && ghdl -r sumador2digitos_tb --vcd=dump.vcd && sed -i 's/^U/X/g; s/^-/X/g; s/^H/1/g; s/^L/0/g' dump.vcd

analyze testbench.vhd

analyze design.vhd

elaborate sumador2digitos_tb

Finding VCD file...

./dump.vcd

[2021-04-15 07:23:08 EDT] Opening EPWave...

Done

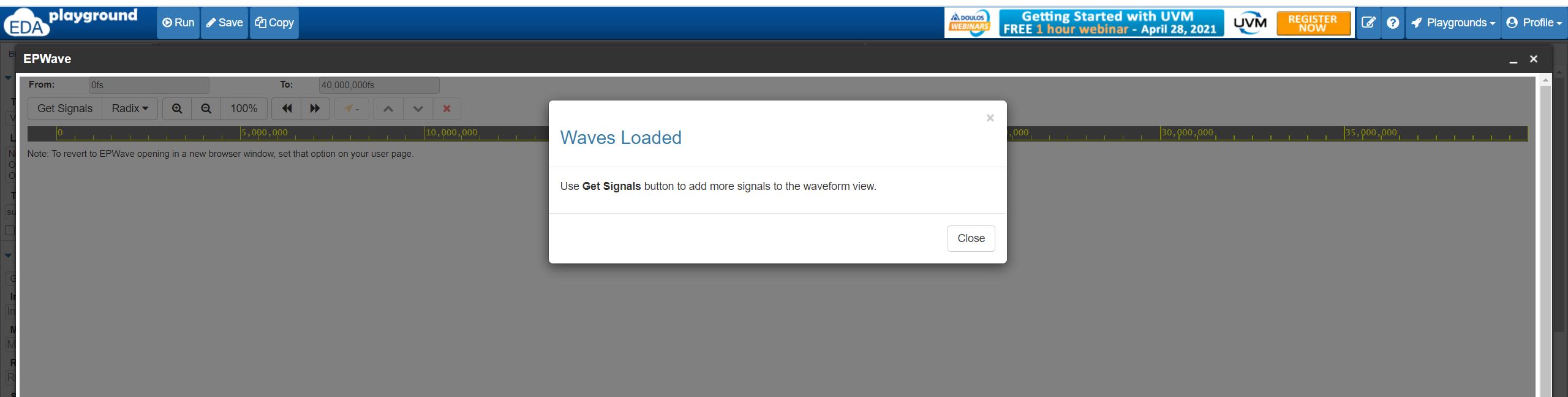

No podremos ver directamente la consola porque, si no ha habido errores, el EDA playground abrirá automáticamente una ventana emergente con la presentación de la simulación.

6.3.6.3.2. Entorno EP Wave¶

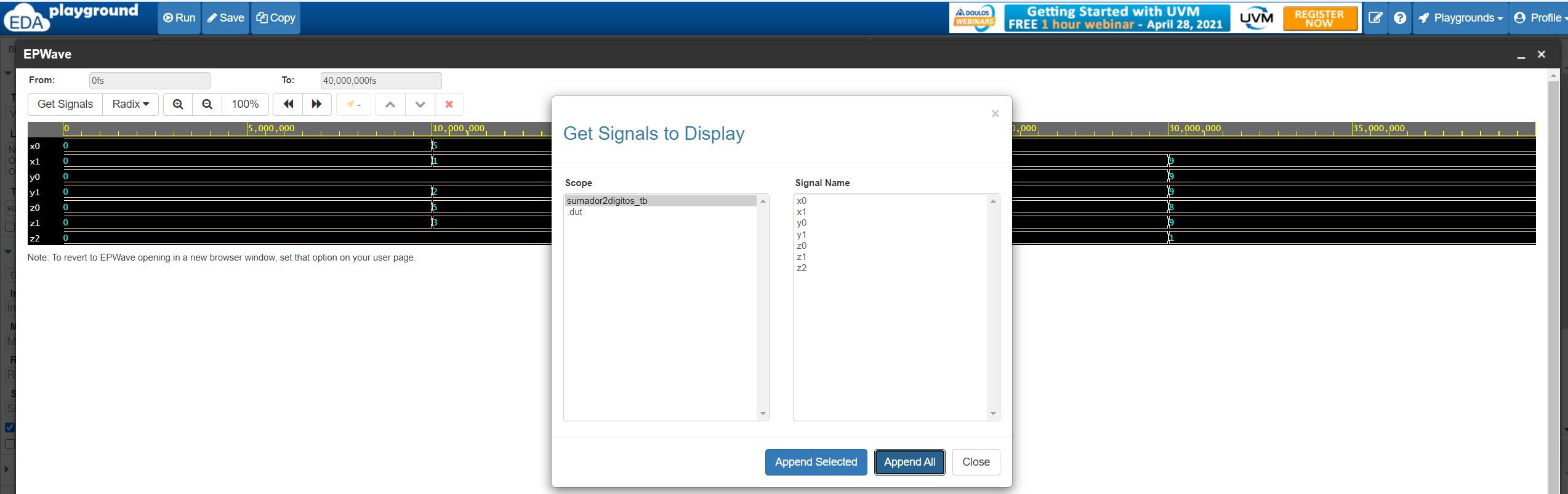

El EP Wave es una ventana emergente, que en el primer momento tendrá un aspecto similar al de la siguiente figura:

Picamos en close y luego en Get Signals y seleccionamos el sumador2digitos_tb y picamos en Append All.

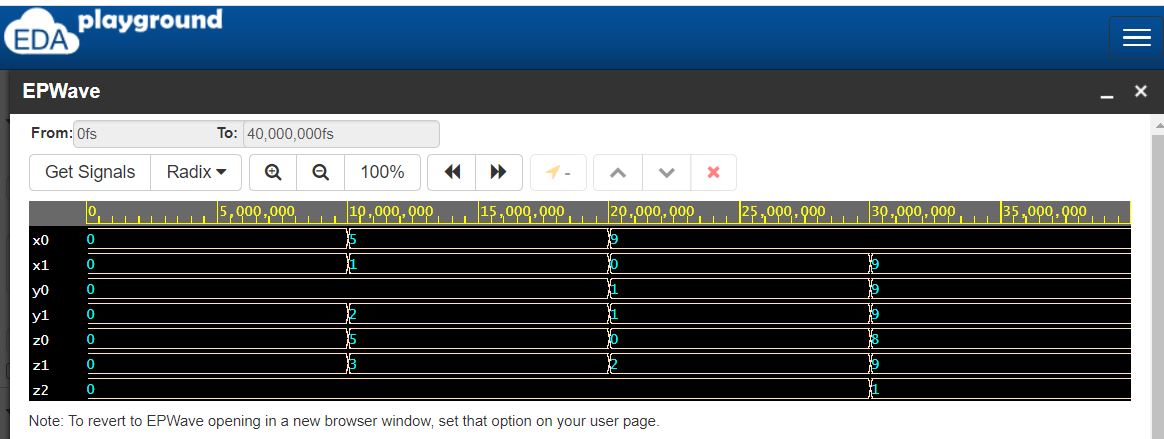

El resultado final debe ser unas formas de onda tales como las siguientes:

Siguiendo las formas de onda se puede ver que el resultado de cada operación de suma es correcto.

Los menús disponibles EP Wave son los siguientes:

Get Signals: Permite incorporar a la EP Wave las señales y puertos de entrada salida del diseño mediante una ventana emergente.

Nota

Normalmente solo se requiere seleccionar aquellas señales que corresponden al testbench.

Radix: Nos permitirá seleccionar si la información se representa en Binario o en Hexadecimal.

Zoom Permite aumentar y reducir la escala de tiempos.

Scroll Left y Scroll Right: permite mover la simulación a izquierda o derecha

La fecha arriba y abajo permite mover las señales arriba o abajo para comprender mejor la simulación.

Marca de borrado. Permite eliminar una señal de la representación EP Wave.

Si cerramos la ventana de EP Wave volveremos al entorno de EDA playground y podremos ver los mensajes de consola mencionados en el apartado anterior.

6.3.6.3.3. Banco de pruebas con salida textual¶

Las formas de onda son muy útiles cuando se quiere analizar en detalle lo que ocurre en los circuitos diseñados. En diseños muy complejos es más conveniente que la salida del testbench sea un mensaje que indique si el circuito ha pasado el test o no. En esos casos el testbench es mucho más elaborado ya que requiere de:

Una generación de estímulos (entradas) adecuados (por ejemplo, en este caso deben estar en el rango de 0 a 9).

Una parte de descripción en VHDL que obtenga las salidas que deberían ser correctas. En este caso se puede hacer simplemente generando la suma según las entradas (estímulos).

Nota

Para obtener una descripción de las salidas correctas a veces es necesario un modelo que realice exactamente la misma operación que el circuito diseñado. A eso se llama golden reference.

Una parte de descripción VHDL que permita la comparación de la salida real del circuito con la salida correcta.

Acceder al Campus Virtual de la asignatura y en la sección de la práctica 1, descargar el Banco de prueba automático para verificar el sumador de enteros. El banco de prueba realiza todas las funciones mencionadas anteriormente para el sumador de dos digitos.

Para realizar la verficación mediante simulación realizamos los siguientes pasos:

En la ventana de testbench.vhd del EDA playground borramos el texto que hay ahora y lo sustituimos por el nuevo testbench bajado del Campus Virtual.

En el menú de la izquierda deshabilitamos la opción Open EPWave after run.

Guardamos el diseño con Save.

Realizamos la simulación con Run.

En la consola se puede ver que el resultado es el correcto. Se han realizado 26 operaciones (inicialización más 25 operaciones de sumas) con enteros de dos dígitos y siempre el resultado ha sido correcto. El último mensaje así lo indica: Adder Simulation successfully completed.

Log Share

[2021-04-15 07:53:27 EDT] ghdl -i design.vhd testbench.vhd && ghdl -m sumador2digitos_tb && ghdl -r sumador2digitos_tb --vcd=dump.vcd && sed -i 's/^U/X/g; s/^-/X/g; s/^H/1/g; s/^L/0/g' dump.vcd

analyze testbench.vhd

analyze design.vhd

elaborate sumador2digitos_tb

testbench.vhd:63:13:@0ms:(report note): Adder Simulation started

testbench.vhd:108:9:@0ms:(report note): testid:0 x1x0:00 + y1y0:00 = Z:000

testbench.vhd:108:9:@5ns:(report note): testid:1 x1x0:88 + y1y0:25 = Z:113

testbench.vhd:108:9:@15ns:(report note): testid:2 x1x0:10 + y1y0:05 = Z:015

testbench.vhd:108:9:@25ns:(report note): testid:3 x1x0:11 + y1y0:15 = Z:026

testbench.vhd:108:9:@35ns:(report note): testid:4 x1x0:18 + y1y0:22 = Z:040

testbench.vhd:108:9:@45ns:(report note): testid:5 x1x0:86 + y1y0:80 = Z:166

testbench.vhd:108:9:@55ns:(report note): testid:6 x1x0:88 + y1y0:03 = Z:091

testbench.vhd:108:9:@65ns:(report note): testid:7 x1x0:08 + y1y0:38 = Z:046

testbench.vhd:108:9:@75ns:(report note): testid:8 x1x0:71 + y1y0:10 = Z:081

testbench.vhd:108:9:@85ns:(report note): testid:9 x1x0:78 + y1y0:20 = Z:098

testbench.vhd:108:9:@95ns:(report note): testid:10 x1x0:37 + y1y0:44 = Z:081

testbench.vhd:108:9:@105ns:(report note): testid:11 x1x0:81 + y1y0:30 = Z:111

testbench.vhd:108:9:@115ns:(report note): testid:12 x1x0:42 + y1y0:12 = Z:054

testbench.vhd:108:9:@125ns:(report note): testid:13 x1x0:75 + y1y0:32 = Z:107

testbench.vhd:108:9:@135ns:(report note): testid:14 x1x0:72 + y1y0:66 = Z:138

testbench.vhd:108:9:@145ns:(report note): testid:15 x1x0:42 + y1y0:33 = Z:075

testbench.vhd:108:9:@155ns:(report note): testid:16 x1x0:44 + y1y0:47 = Z:091

testbench.vhd:108:9:@165ns:(report note): testid:17 x1x0:07 + y1y0:83 = Z:090

testbench.vhd:108:9:@175ns:(report note): testid:18 x1x0:46 + y1y0:82 = Z:128

testbench.vhd:108:9:@185ns:(report note): testid:19 x1x0:46 + y1y0:61 = Z:107

testbench.vhd:108:9:@195ns:(report note): testid:20 x1x0:83 + y1y0:14 = Z:097

testbench.vhd:108:9:@205ns:(report note): testid:21 x1x0:06 + y1y0:22 = Z:028

testbench.vhd:108:9:@215ns:(report note): testid:22 x1x0:26 + y1y0:03 = Z:029

testbench.vhd:108:9:@225ns:(report note): testid:23 x1x0:40 + y1y0:65 = Z:105

testbench.vhd:108:9:@235ns:(report note): testid:24 x1x0:73 + y1y0:40 = Z:113

testbench.vhd:108:9:@245ns:(report note): testid:25 x1x0:34 + y1y0:45 = Z:079

testbench.vhd:108:9:@255ns:(report note): testid:26 x1x0:37 + y1y0:43 = Z:080

testbench.vhd:97:13:@260ns:(report note): Your code is working fine :-)

testbench.vhd:98:13:@260ns:(report note): Adder Simulation successfully completed

Done

Para comprobar que el banco de pruebas detecta correctamente cuando la descripción tiene un error, vamos a modificar la descripción VHDL del diseño (Listado 6.1). En la línea que describe s1 vamos a producir un error sumando siempre un acarreo.

La siguiente parte del código VHDL del Listado 6.1:

BEGIN

s0 <= x0_in + y0_in;

s1 <= x1_in + y1_in + carry;

PROCESS (s0)

vamos a cambiarla por esta otra (solo se sustituye carry por 1):

BEGIN

s0 <= x0_in + y0_in;

s1 <= x1_in + y1_in + 1;

PROCESS (s0)

Guardamos el diseño con Save.

Realizamos la simulación con Run.

En la consola se puede ver que el resultado en este caso no es correcto. Se han realizado 3 operaciones y en la tercera (testid = 2) ya ha detectado el error. El último mensaje así lo indica: Simulation ended with errors.

[2021-04-15 08:03:43 EDT] ghdl -i design.vhd testbench.vhd && ghdl -m sumador2digitos_tb && ghdl -r sumador2digitos_tb

analyze testbench.vhd

analyze design.vhd

elaborate sumador2digitos_tb

testbench.vhd:63:13:@0ms:(report note): Adder Simulation started

testbench.vhd:108:9:@0ms:(report note): testid:0 x1x0:00 + y1y0:00 = Z:000

testbench.vhd:108:9:@5ns:(report note): testid:1 x1x0:88 + y1y0:25 = Z:113

testbench.vhd:108:9:@15ns:(report note): testid:2 x1x0:10 + y1y0:05 = Z:025

testbench.vhd:115:9:@15ns:(assertion error): ERROR: expected output named suma:15

testbench.vhd:91:13:@20ns:(report note): Your code is NOT working properly :-(

testbench.vhd:92:13:@20ns:(report note): Simulation ended with errors

Done

6.3.7. Entregables¶

6.3.7.1. Trabajo previo¶

No hay entregables.

6.3.7.2. Trabajo de laboratorio¶

Por hacer

E1.1. Mostrar al profesor de prácticas la realización de cada uno de los pasos realizados según el apartado (ver Sección Trabajo de laboratorio).

6.3.8. Comentarios sobre la práctica¶

Las herramientas on-line EDA playground (https://www.edaplayground.com/) y VHDL-tool (https://www.vhdltool.com/tryit) constituye una manera rápida de comprobar si las descripciónes en VHDL tienen una sintaxis correcta y están realizadas correctamente para la función especificada.