6.7. Práctica 5: Unidad Aritmético Lógica (ALU)¶

6.7.1. Duración¶

Esta práctica tendrá una duración de 2 horas en el laboratorio (1 sesión).

6.7.2. Objetivos¶

El objetivo general de esta práctica es el «Diseño e implementación de una ALU que realiza operaciones aritméticas». Otros objetivos específicos son los siguientes:

Introducir las estructuras condicionales en VHDL.

Discriminar el uso de las instrucciones WHEN, IF y CASE

Introducir tipos de datos usados en numeric_std.

Repasar los conceptos de: 1) diseño modular, 2) diseño secuencial y concurrente, y 3) diseño a distintos niveles de abstracción.

6.7.3. Introducción¶

Las Unidades Aritmético Lógicas (ALUs) son circuitos que realizan varias operaciones de carácter aritmético o lógico (ver transparencias de teoría del tema 8, páginas 54 a 63). Su elemento principal es un sumador. Para la realización de las operaciones aritméticas en VHDL es necesario usar los tipos SIGNED y/o UNSIGNED (dependiendo de si las operaciones dan lugar a resultados negativos o no) definidos en la librería ieee.numeric_std. La descripción VHDL se hace con la instrucción CASE. Un ejemplo se puede ver en la página 60 de las transparencias de teoría del tema 8.

En esta práctica se va a construir una ALU que realiza las operaciones de suma o de resta de dos datos de entrada (ver Tabla 6.4.). Las entradas A y B estarán representadas en binario natural y tendrán en total 4 bits. La salida estará representada en complemento a dos (para poder representar resultados negativos) y con un número de bits a determinar por el diseñador (estudiante). La elección de la operación a realizar se gobierna con una señal OP de dos bits, de acuerdo a la siguiente tabla:

OP1 OP0 |

Operación |

|---|---|

0 0 |

A + B |

0 1 |

A - B |

1 0 |

-A + B |

1 1 |

0 |

6.7.4. Trabajo previo¶

6.7.4.1. Determinar el número de bits del resultado¶

Según las operaciones a realizar, determinar en qué situaciones puede haber desbordamiento (overflow) y determinar el número de bits de las operaciones intermedias y de la salida. Hay que tener en cuenta que las entradas A y B estarán representadas en binario natural (son siempre números positivos) y tendrán en total 4 bits (valores entre 0 y 15). Ya que en la ALU se van a realizar operaciones de suma y resta es necesario usar la librería numeric y el tipo SIGNED. Al usar el tipo SIGNED, que representa directamente los números en complemento a dos, se pueden realizar las operaciones de suma y resta directamente, siendo únicamente necesario tener en cuenta el número de bits necesarios para operar para que no haya desbordamiento.

6.7.4.2. Descripción en VHDL de la ALU¶

Hacer una descripción funcional del circuito en VHDL usando la instrucción CASE y la instrucción WHEN. La entrada de los datos debe realizarse siempre con tipos STD_LOGIC. Las operaciones internas se realizarán con señales con tipo SIGNED y/o UNSIGNED. Se evitará el desbordamiento usando la extensión de signo necesaria.

El resultado final debe darse en formato signo-magnitud, por lo que a la salida de la ALU se debe convertir de complemento a dos a signo-magnitud.

Realice la descripción de la ALU en el Laboratorio de Programación Virtual (VPL: Práctica 5: Unidad Aritmético-Lógica (ALU)) en el Campus Virtual de la asgnatura. Se recomienda realizar la simulación con EdaPlayground (ver sección Otras herramientas usadas) antes del VPL.

6.7.5. Trabajo en el Laboratorio¶

6.7.5.1. Pasos a realizar en el QuartusII/Modelsim-Altera¶

Obtener los ficheros necesarios del Campus Virtual y crear un proyecto nuevo (Practica5.qpf) dentro del subdirectorio quartus.

Crear un nuevo fichero VHDL para describir la función de la ALU.

Introducir en este fichero la descripción realizada en el apartado Descripción en VHDL de la ALU y guardar el fichero como ALU_Practica5.vhd.

Declarar a ALU_Practica5.vhd como el top-level del circuito.

Compilar el diseño.

Crear un nuevo fichero de formas de onda con el University Wafeform VWF (Waveform.vwf).

Simular este circuito usando Modelsim-Altera.

Introducir todos los pines del circuito en el diagrama de formas de onda.

Ordenar las señales de la siguiente manera: a_in, b_in, op1_in, op2_in, resultado.

Establecer el tiempo de simulación en 500 ns.

Siguiente secuencia de entradas a partir de los 50 ns iniciales.

tiempo (ns) |

a_in |

b_in |

op_in |

Operación |

|---|---|---|---|---|

0-100 |

1111 |

1111 |

00 |

A+B |

100-200 |

1111 |

1111 |

01 |

A-B |

200-300 |

1010 |

1111 |

10 |

-A+B |

300-400 |

1111 |

1010 |

10 |

-A+B |

400-500 |

1111 |

1010 |

11 |

0 |

Ejecutar la simulación en Modelsim-Altera.

Seleccionar para data1_in, data2_in y rest_out el radix como “Unsigned Decimal”

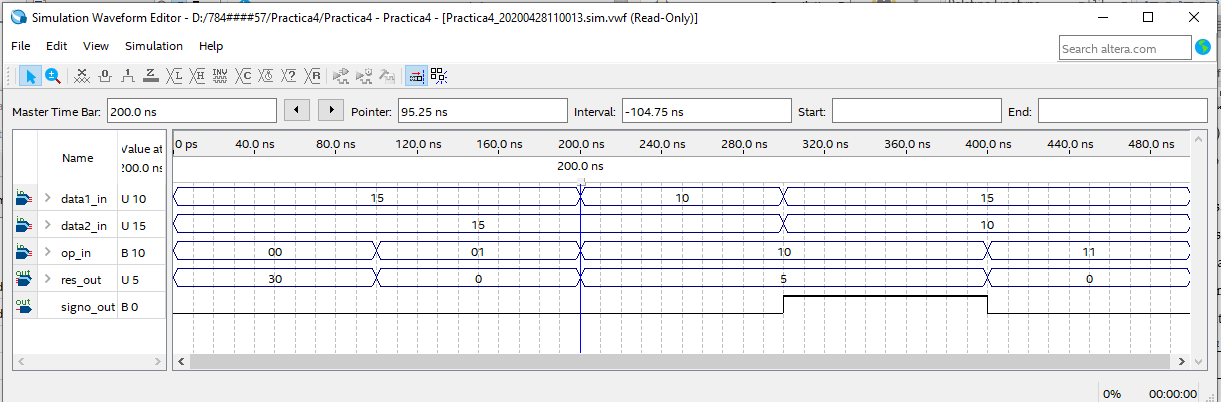

Comprobar que los resultados son los esperados según la figura siguiente:

Figura 6.10 Resultado de la simulación de la Práctica 5.¶

6.7.5.2. Implementación en la tarjeta DE10_lite¶

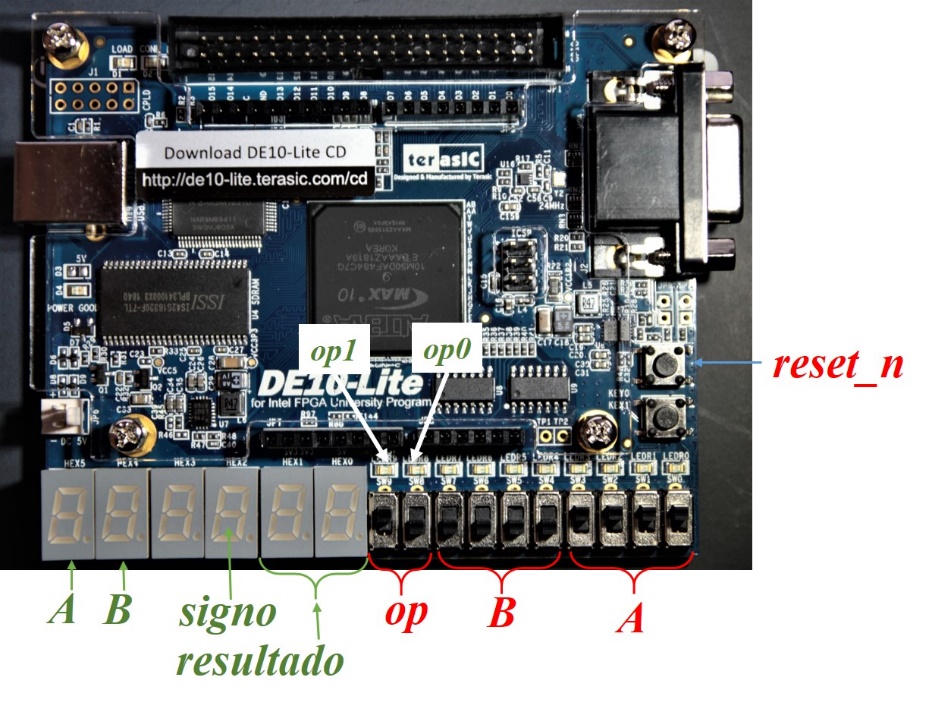

La información se introducirá mediante los interruptores de la siguiente manera:

El dato de entrada A en los interruptores SW[3] a SW[0].

El dato de entrada B en los interruptores SW[7] a SW[4].

Las operaciones a realizar con los SW[9] (OP2) y SW[8] (OP1).

La representación del resultado se realizará en los displays de 7 segmentos de la siguiente manera:

Los datos de entrada A y B (binario natural, valores entre 0 y 15), se representarán en hexadecimal en los displays números 5 y 4 respectivamente.

El resultado final se representará en los displays 1 y 0 en formato BCD.

El signo del resultado se representará en el display 2 mediante el segmento 6 (apagado para el 0 y encendido para el 1). El resto de segmentos estará siempre apagado.

Figura 6.11 Pin-out de la Práctica 5.¶

Para la implementación realice las siguientes tareas:

Añadir al proyecto la descripción VHDL (Practica5.vhd) que se proporciona en el Campus Virtual. Se observa que este VHDL representa la descripción del sistema completo y las conexiones de entrada/salida de la placa DE10-Lite.

Añadir al proyecto las descripciones proporcionadas en el Campus Virtual (ver Listado 6.12, Listado 6.13, Listado 6.14 y Listado 6.15):

binary_to_7seg_display.vhd, que representa un valor en binario en un display de 7 segmentos;

bynary_to_BCD.vhd y binary_to_bcd_digit.vhd, que convierten un valor binario en código BCD; y

BCD_7segment.vhd, que representa un valor en BDC en un display de 7 segmentos.

Declarar a Practica5.vhd como el top-level del circuito.

Compilar el diseño.

Importar las descripciones de los pines que está en el subdirectorio quartus (Practica5.qsf): Assignments > Import Assignments.

Compilar el diseño.

Programar la tarjeta usando el fichero Practica5.sof.

Comprobar que los resultados son exactamente iguales que los obtenidos de la tabla de verdad y a la simulación realizada.

6.7.6. Entregables¶

6.7.6.1. Trabajo previo¶

Por hacer

E5.1. Descripción funcional VHDL de la ALU descrita en el apartado Descripción en VHDL de la ALU y su verficación en el VPL del Campus Virtual.

6.7.6.2. Trabajo de laboratorio¶

Por hacer

E5.2. Mostrar al profesor de prácticas la realización de los pasos realizados según el apartado Pasos a realizar en el QuartusII/Modelsim-Altera.

E5.3. Mostrar al profesor el funcionamiento del circuito realizado en el apartado Implementación en la tarjeta DE10_lite en la tarjeta DE10-lite.

6.7.7. Comentarios sobre la práctica¶

6.7.7.1. Corrección de la salida¶

Recuerde que los circuitos que operan en complemento a dos pueden tener desbordamiento (overflow) cuando el signo de los operandos es igual entre sí y distinto al signo del resultado. En este caso el signo del resultado debe forzarse a ser igual que al de los operandos (véase las transparencias del tema 8). Al usar el tipo SIGNED que representa directamente los números en complemento a dos, se pueden realizar las operaciones de suma y resta, siendo únicamente necesario tener en cuenta el número de bits necesarios a la salida.

6.7.8. Listados VHDL¶

-- Ver en el campus Virtual de la Asignatura

-- Ver en el campus Virtual de la Asignatura

-- Ver en el campus Virtual de la Asignatura

-- Ver en el campus Virtual de la Asignatura

-- Ver en el campus Virtual de la Asignatura