6.5. Práctica 3: Funciones lógicas, minimización e implementación¶

6.5.1. Duración¶

Esta práctica tendrá una duración de 2 horas en el laboratorio (1 sesión).

6.5.2. Objetivos¶

El objetivo general de esta práctica es «Minimizar e implementar una función lógica». Otros objetivos específicos son los siguientes:

Realizar un diseño básico siguiendo la metodología que se definió en la Práctica 1.

Hacer el diseño y verificación de los sistemas digitales usando VHDL.

Introducir el concepto de diseño modular y jerárquico.

Profundizar en el uso de la herramienta Quartus II.

6.5.3. Introducción¶

En esta práctica se realizará la implementación de una función que debe minimizarse previamente usando el método de mapas de Karnaugh. Una vez minimizada se debe realizar el esquema usando únicamente puertas NOT y NAND. La descripción en VHDL de este circuito se debe hacer como una descripción estructural, es decir, tomando como referencia la estructura y componentes del circuito a describir. En el Campus Virtual se proporciona la descripción de las puertas básicas en VHDL (también se encuentra en el apartado Listados VHDL). La implementación de este circuito en la tarjeta DE10-Lite se puede realizar siguiendo los pasos de la Práctica 2.

6.5.4. Trabajo previo¶

6.5.4.1. Minimización de la función¶

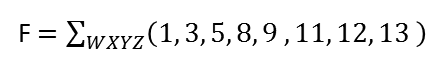

Escriba una ecuación normalizada y simplificada para la siguiente función F en forma de suma de productos. Emplear el procedimiento de mapas de Karnaugh para lograr la expresión que se busca.

Una vez minimizada haga un esquema de puertas únicamente usando puertas NOT y NAND. Esta entrega debe hacerse en el Campus Virtual.

6.5.4.2. Descripción estructural en VHDL¶

Realice una descripción estructural con VHDL del circuito desarrollado en el punto anterior. Esta función requeríra de la descripción VHDL de las puertas básicas:

Puerta NOT, cuya descripción está en el Listado 6.4.

Puerta NAND de dos entradas (NAND_gate_2). La descripción de la entidad está en: Listado 6.5, y

Puerta NAND de tres entradas (NAND_gate_3). La descripción de la entidad está en: Listado 6.6).

Nota

Descargar las descripciones de estas puertas en el Campus Virtual en la sección correspondiente a la Práctica 3.

Usando estas descripciones, realizar la descripción VHDL de tipo estructural de la expresión normalizada y simplificada obtenida en la tarea Minimización de la función en el laboratorio Virtual (VPL: Práctica 3: Funciones lógicas) que se encuentra en el Campus Virtual de la asignatura.

Nota

Tenga en cuenta que los tipos de datos deben ser STD_LOGIC y que las entradas siempre deben ser nombradas con el sufijo “_in”, es decir: w_in, x_in, y_in y z_in. Por su lado la salida debe ser f_out. Ver el esqueleto de descripción en Listado 6.7.

Opcionalmente puede simular el diseño con la herramienta EDA playground (https://www.edaplayground.com/) y realizar el banco de pruebas con el Testbench Generator (https://vhdl.lapinoo.net/testbench/) y chequear la sintaxis de la descripción realizada con la herramienta web VHDL-tool (https://www.vhdltool.com/tryit)..

6.5.5. Trabajo de laboratorio¶

6.5.5.1. Pasos a realizar en el QuartusII/Modelsim-Altera¶

Crear el directorio #DNI#/Practica3. Copiar el fichero Practica3_VHDL.zip y descomprimirlo. Los tres ficheros VHDL del (Listado 6.4, Listado 6.5 y Listado 6.6) se encuentran en el directorio ips-basicos. El subdirectorio quartus será el subdirectorio de trabajo.

Abrir QuartusII y, siguiendo los pasos del tutorial de Quartus II, crear un proyecto nuevo (Practica3.qpf) en el subdirectorio quartus.

Añadir al proyecto las descripciones básicas de las puertas que se encuentran en el subdirectorio ip-basicos: not_gate.vhd, nand_gate_2.vhd y nand_gate_3.vhd.

Crear un nuevo fichero VHDL para describir la función F1.

Introducir en este fichero la descripción realizada en el Trabajo Previo (apartado Descripción estructural en VHDL) y guardarlo con el nombre funcion.vhd.

Declarar a función.vhd como el top-level del circuito.

Compilar el diseño.

Crear un nuevo fichero de formas de onda con el University Wafeform Program (Waveform.vwf).

Simular este circuito usando Modelsim-Altera.

Introducir todos los pines del circuito en el diagrama de formas de onda.

Ordenar las señales según su peso: w, x, y, z.

Establecer el tiempo de simulación en 640 ns.

Dar valores a todas las entradas siguiendo la tabla de verdad (en total 16 combinaciones). Cada combinación de entrada tendrá una duración de 40 ns.

Agrupar las entradas en una sola señal, que se denominará input.

Ejecutar la simulación en Modelsim-Altera.

Comprobar que los resultados son exactamente iguales que los de la tabla de verdad.

6.5.5.2. Implementación en la tarjeta DE10_lite¶

Crear un COMPONENTE VHDL para el esquema del circuito (funcion.vhd). La descripción del componente se guardará automáticamente en el fichero ./Practica3/funcion.cmp.

Añadir al proyecto la descripción VHDL Practica3.vhd (Listado 6.8) y modificarlo para añadir la descripción del componente creado y realizar las asignaciones de entrada y salida.

Declarar a Practica3.vhd como el top-level del circuito.

Compilar el diseño.

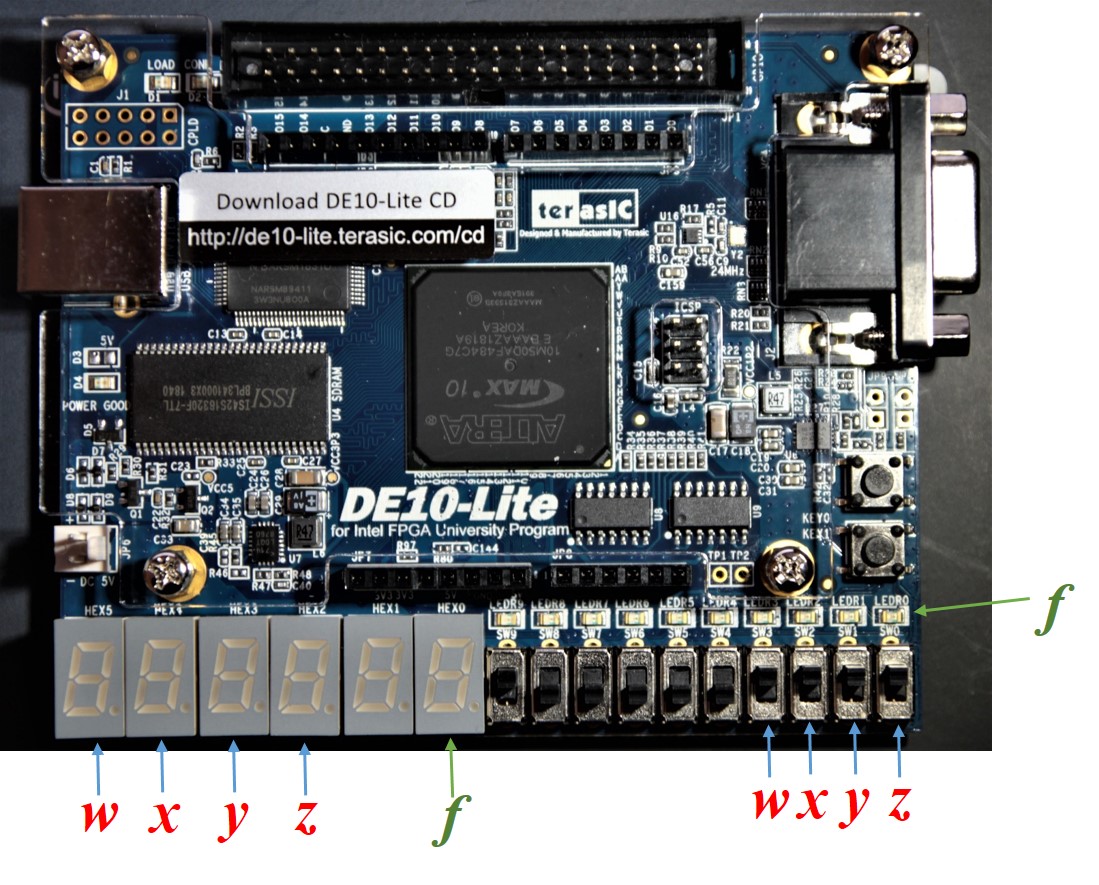

Asignar los pines correspondientes en la tarjeta DE10-Lite según la distribución de la Figura 6.3.

Figura 6.3 Pin-out de la Práctica 3.¶

La asignación de pines se hará siguiendo la Figura anterior y las siguientes tablas.

Señal |

w_in |

x_in |

y_in |

z_in |

f_out |

|---|---|---|---|---|---|

PIN |

PIN_C12 |

PIN_D12 |

PIN_C11 |

PIN_C10 |

PIN_A8 |

Corresponde a |

Slide Switch[3] |

Slide Switch[2] |

Slide Switch[1] |

Slide Switch[0] |

LED[0] |

Los pines de los displays de 7 segmentos se muestran en la siguiente tabla.

Nombre |

Pin |

Concepto |

|---|---|---|

display_7segment0[0] |

PIN_C14 |

Seven Segment Digit 0[0] |

display_7segment0[1] |

PIN_E15 |

Seven Segment Digit 0[1] |

display_7segment0[2] |

PIN_C15 |

Seven Segment Digit 0[2] |

display_7segment0[3] |

PIN_C16 |

Seven Segment Digit 0[3] |

display_7segment0[4] |

PIN_E16 |

Seven Segment Digit 0[4] |

display_7segment0[5] |

PIN_D17 |

Seven Segment Digit 0[5] |

display_7segment0[6] |

PIN_C17 |

Seven Segment Digit 0[6] |

display_7segment0[7] |

PIN_D15 |

Seven Segmenl Digit 0[7] , DP |

display_7segment2[0] |

PIN_B20 |

Seven Segment Digit 2[0] |

display_7segment2[1] |

PIN_A20 |

Seven Segment Digit 2[1] |

display_7segment2[2] |

PIN_B19 |

Seven Segment Digit 2[2] |

display_7segment2[3] |

PIN_A21 |

Seven Segment Digit 2[3] |

display_7segment2[4] |

PIN_B21 |

Seven Segment Digit 2[4] |

display_7segment2[5] |

PIN_C22 |

Seven Segment Digit 2[5] |

display_7segment2[6] |

PIN_B22 |

Seven Segment Digit 2[6] |

display_7segment2[7] |

PIN_A19 |

Seven Segmenl Digit 2[7] , DP |

display_7segment3[0] |

PIN_F21 |

Seven Segment Digit 3[0] |

display_7segment3[1] |

PIN_E22 |

Seven Segment Digit 3[1] |

display_7segment3[2] |

PIN_E21 |

Seven Segment Digit 3[2] |

display_7segment3[3] |

PIN_C19 |

Seven Segment Digit 3[3] |

display_7segment3[4] |

PIN_C20 |

Seven Segment Digit 3[4] |

display_7segment3[5] |

PIN_D19 |

Seven Segment Digit 3[5] |

display_7segment3[6] |

PIN_E17 |

Seven Segment Digit 3[6] |

display_7segment3[7] |

PIN_D22 |

Seven Segmenl Digit 3[7] , DP |

display_7segment4[0] |

PIN_F18 |

Seven Segment Digit 4[0] |

display_7segment4[1] |

PIN_E20 |

Seven Segment Digit 4[1] |

display_7segment4[2] |

PIN_E19 |

Seven Segment Digit 4[2] |

display_7segment4[3] |

PIN_J18 |

Seven Segment Digit 4[3] |

display_7segment4[4] |

PIN_H19 |

Seven Segment Digit 4[4] |

display_7segment4[5] |

PIN_F19 |

Seven Segment Digit 4[5] |

display_7segment4[6] |

PIN_F20 |

Seven Segment Digit 4[6] |

display_7segment4[7] |

PIN_F17 |

Seven Segmenl Digit 4[7] , DP |

display_7segment5[0] |

PIN_J20 |

Seven Segment Digit 5[0] |

display_7segment5[1] |

PIN_K20 |

Seven Segment Digit 5[1] |

display_7segment5[2] |

PIN_L18 |

Seven Segment Digit 5[2] |

display_7segment5[3] |

PIN_N18 |

Seven Segment Digit 5[3] |

display_7segment5[4] |

PIN_M20 |

Seven Segment Digit 5[4] |

display_7segment5[5] |

PIN_N19 |

Seven Segment Digit 5[5] |

display_7segment5[6] |

PIN_N20 |

Seven Segment Digit 5[6] |

display_7segment5[7] |

PIN_L19 |

Seven Segmenl Digit 5[7] , DP |

Nota

Se puede hacer copy&paste de los pines en el PIN_Planner. Se proporciona el fichero Practica3.qsf que se puede importar en el proyecto.

Advertencia

Comprobar que todos los pines están alimentados con 3.3V LVTTL.

Cerrar el Pin_planner y compilar el diseño.

Programar la tarjeta usando el fichero Practica3.sof.

Comprobar que los resultados son exactamente iguales que los de la tabla de verdad y los de la simulación realizada.

6.5.6. Entregables¶

6.5.6.1. Trabajo previo¶

Por hacer

E3.1. Realizar y subir al Campus Virtual el proceso de minimización de la función del apartado Minimización de la función usando mapas de Karnaugh, incluyendo la expresión algebraica y circuitos resultantes.

E3.2. Laboratorio Virtual (VPL) de la descripción estructural VHDL y simulación según los especificado en en el apartado Descripción estructural en VHDL.

6.5.6.2. Trabajo de laboratorio¶

Por hacer

E3.3. Mostrar al profesor de prácticas la realización de los pasos realizados según el apartado Pasos a realizar en el QuartusII/Modelsim-Altera.

E3.4. Mostrar al profesor el funcionamiento del circuito realizado en el apartado Implementación en la tarjeta DE10_lite.

6.5.7. Comentarios sobre la práctica¶

6.5.7.1. Recomendaciones¶

Para realizar esta práctica se recomienda repasar el tutorial de QuartusII-Modelsim.

Es importante no usar ningún nombre que contenga tildes o la letra “ñ” en los diseños.

6.5.7.2. Conceptos VHDL necesarios¶

Se refuerza el uso de COMPONENT.

Se refuerza el uso de SIGNALS.

6.5.8. Listados VHDL¶

-- Electronica Digital, curso 2

-- EITE-ULPGC

-- Puerta NOT sin retardo

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY not_gate IS

PORT(x_in : IN STD_LOGIC;

z_out : OUT STD_LOGIC );

END not_gate ;

ARCHITECTURE funcional OF not_gate IS

BEGIN

z_out <= NOT x_in;

END funcional;

-- Electronica Digital, curso 2

-- EITE-ULPGC

-- Puerta NAND de dos entradas

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY nand_gate_2 IS

PORT( x_in : IN STD_LOGIC;

y_in : IN STD_LOGIC;

z_out: OUT STD_LOGIC );

END nand_gate_2 ;

ARCHITECTURE funcional OF nand_gate_2 IS

BEGIN

-- REALIZAR LA DESCRIPCION DE (X·Y)'

END funcional;

-- Electronica Digital, curso 2

-- EITE-ULPGC

-- Puerta NAND de tres entradas

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY nand_gate_3 IS

PORT(w_in : IN STD_LOGIC;

x_in : IN STD_LOGIC;

y_in : IN STD_LOGIC;

z_out : OUT STD_LOGIC );

END nand_gate_3 ;

ARCHITECTURE funcional OF nand_gate_3 IS

BEGIN

-- REALIZAR LA DESCRIPCION DE (W·X·Y)'

END funcional;

-- Electronica Digital, curso 2

-- EITE-ULPGC

-- Circuito de Practica 3

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY funcion IS

PORT (

w_in : IN STD_LOGIC;

x_in : IN STD_LOGIC;

y_in : IN STD_LOGIC;

z_in : IN STD_LOGIC;

f_out : OUT STD_LOGIC );

END funcion ;

ARCHITECTURE estructural OF funcion IS

COMPONENT not_gate IS

PORT(

x_in : IN STD_LOGIC;

z_out : OUT STD_LOGIC );

END COMPONENT;

-- DECLARAR OTROS COMPONENTES NECESARIOS

-- DECLARAR LAS SEÑALES NECESARIAS

BEGIN

-- REALIZAR LA DESCRIPCIÓN ESTRUCTURAL DE LA FUNCION

END estructural;

-- Ver en el campus Virtual de la Asignatura