6.6. Práctica 4: Máquina de Estados Finitos (MEF)¶

6.6.1. Duración¶

Esta práctica tendrá una duración de 4 horas en el laboratorio (2 sesiones).

6.6.2. Objetivos¶

El objetivo general de esta práctica es el diseño y realización de una «Diseñar una MEF, describirla en VHDL e implementarla en Quartus II». Otros objetivos específicos son los siguientes:

Conocer las máquinas de estado y su descripción en VHDL.

Reforzar los conceptos de ejecución concurrente y secuencial (procesos).

Describir las MEFs en VHDL como tres procesos independientes.

Definición de los estados como tipos de datos.

Uso de procesos para la generación del estado siguiente y para la transición entre estados.

Depuración a nivel de estado de la MEFs parar encontrar errores.

6.6.3. Introducción¶

Según se ha visto en teoría las máquina de estados finitos (MEFs o FSM) pueden ser de dos tipos: Moore y Mealy (transparencias teoría tema 5 páginas 13-18). También hemos visto que las MEFs de Mealy son susceptibles de producir glitches. Según las transparencias de teoría del Tema 5 (páginas 31-42) principalmente existen tres tipos de MEF:

Controladores

Detector de patrones

Contadores módulo-p

Para describir el comportamiento de una MEF en VHDL existen técnicas normalizadas y establecidas. Estas estrategias para una Máquina de Moore se encuentran definidas en las transparencias de teoría del Tema 5 (páginas 24 a 30).

En esta práctica se va a realizar sobre la tarjeta DE10-Lite una MEF-Moore de tipo controlador. En concreto se va a realizar la implementación de la Máquina de refrescos con las siguientes variaciones:

Se realizará una MEF tipo Moore para evitar los glitches.

Aunque en la especificación del problema se indica que las entradas que detectan las monedas de 10 céntimos y de 20 céntimos no pueden ponerse a valor ‘1’ al mismo tiempo, QuartusII no acepta una descripción de MEF ambigua. Habrá que modificar la descripción para que no sea ambigua especificando todas las opciones posibles.

Para evitar que la introducción de una moneda pueda ser detectada por la MEF varias veces y para evitar que las dos entradas sean 1 a la vez tendremos que añadir un circuito de pre-procesamiento (da prioridad a entrada de veinte céntimos y hace de debouncer).

6.6.3.1. Descripción de la MEF¶

Se desea diseñar un autómata de Moore que controle una máquina expendedora de refrescos. El refresco cuesta 30 céntimos y la máquina es capaz de dar cambio de 10 céntimos. La máquina acepta monedas de 10 céntimos y de 20 céntimos en cuyo caso establecerá unas señales de entrada del autómata a 1; es decir, cuando se introduce una moneda de 10 céntimos la señal de entrada a_in pasa al nivel 1 durante un ciclo de reloj, y cuando se introduce una moneda de 20 céntimos la entrada b_in pasa a nivel 1 durante un ciclo de reloj.

Para hacer esta operación el autómata dispone de dos salidas; una salida denominada r_out (Refresco), que se pone a 1 cuando se debe dar un refresco al usuario; y otra salida denominada c_out (Cambio), que se pone a 1 cuando la máquina debe dar el cambio de 10 céntimos. Existirá otra salida, llamada monedas, que se pondrá a ‘00’, ’01’, ‘10’ o ‘11’ según la máquina haya recibido 0, 10, 20 o 30 céntimos o más, respectivamente.

Nota

Es imposible que las entradas a_in y b_in tomen el valor 1 a la vez.

6.6.3.2. Descripción del circuito completo¶

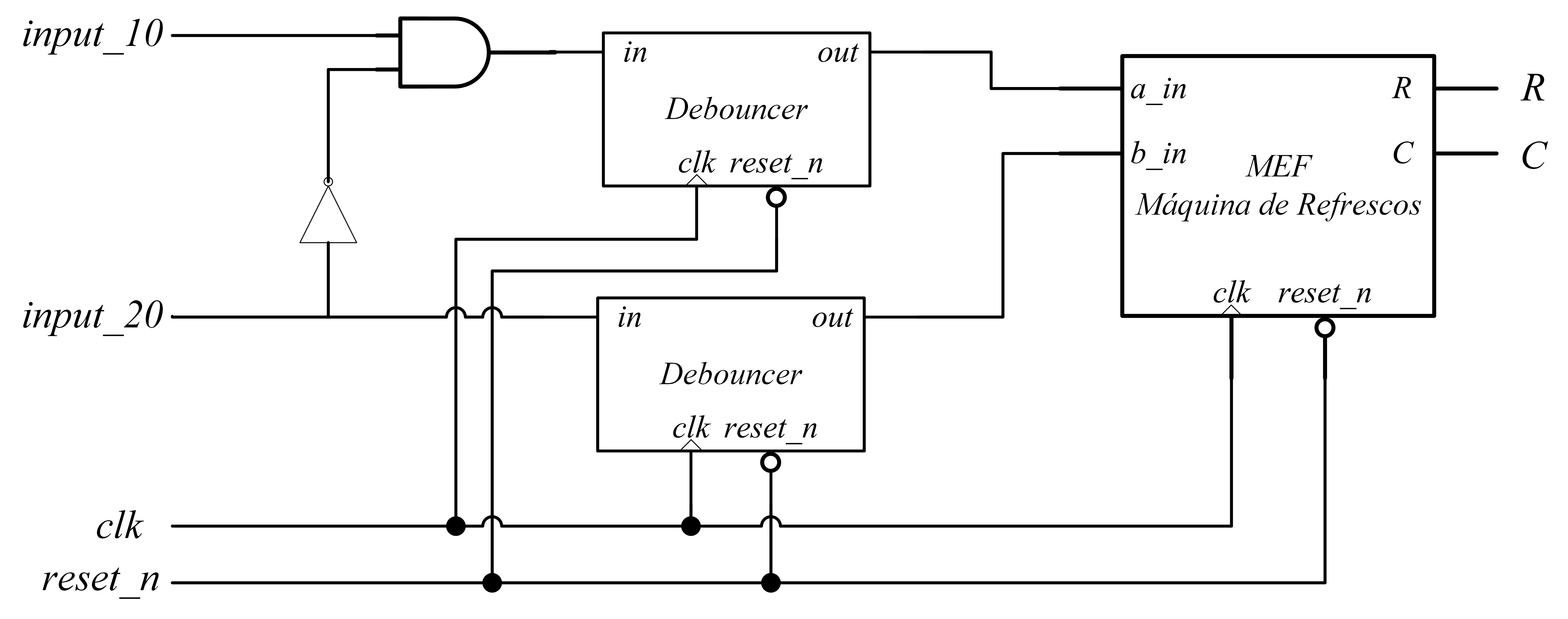

La figura Figura 6.4 representa el circuito al completo incluyendo la MEF que hace de controlador de la máquina de refrescos y el circuito de entrada que realiza de priorización y debouncer.

Figura 6.4 Esquema general del circuito de la Práctica 4.¶

Nota

En la Figura 6.4 la puerta NAND evita que las entradas a_in y b_in puedan ser 1 al mismo tiempo.

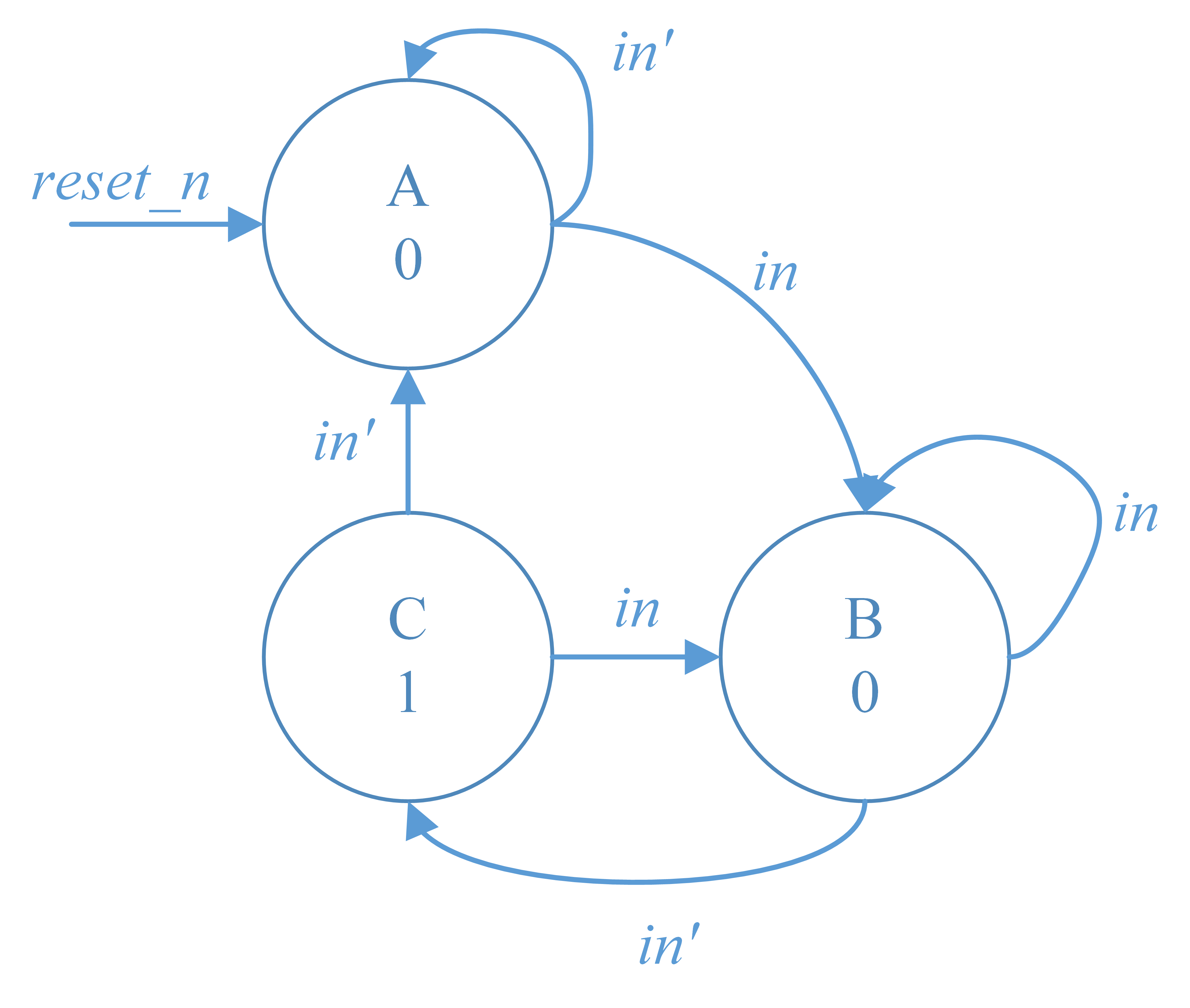

El funcionamiento del debouncer se expresa en el siguiente diagrama de estados (Figura 6.5). Las señales de salida «out» solo se pondrán a 1 en el flanco de bajada de la señal «in».

Figura 6.5 Diagrama de estados del Debouncer.¶

Nota

El debouncer (Figura 6.5) se incluye para que las entradas solo permanezcan a 1 un ciclo de reloj, justo cuando se suelta el pulsador de la tarjeta DE10-Lite.

6.6.4. Trabajo previo¶

6.6.4.1. Grafo de estados de la MEF¶

Diseñar una máquina de estados finitos tipo Moore que corresponde a un esquema de tipo controlador (ver transparencias del Tema 5, páginas 32 y 33), y cuya descripción funcional es la del apartado Descripción de la MEF.

Entradas/salidas:

Entradas: \(clock, reset\_n\) (activo a nivel bajo).

Entradas: \(a\_in \in \{0,1\}, b\_in \in \{0,1\}\).

Salidas: \(r\_out \in \{0,1\}, c\_out \in \{0,1\}, monedas \in \{0,1, 2, 3\}\).

Estados: \(S \in \{idle, diez\_cents, veinte\_cents, rnc, ryc\}\).

Funcionamiento: ver apartado Descripción de la MEF.

En este apartado hay que representar la funcionalidad de la MEF en un grafo que debe ser entregado en el Campus Virtual.

6.6.4.2. Descripción VHDL de la MEF¶

Se debe realizar la descripción VHDL de la MEF siguiendo la metodología estándar (transparencias de teoría del Tema 5, páginas 24 a 30) y describiendo la máquina sin ambigüedades (es decir, no admitiendo casos imposibles).

La descripción VHDL de esta MEF se realizará como un Laboratorio Virtual de Programación (VPL: Práctica 4: Máquina de refrescos) en el Campus Virtual de la asignatura.

Nota

En el VHDL a la señales que representan el estado actual y el futuro llamarlas Qactual o estado_actual y Qfuturo o estado_futuro, respectivamente.

6.6.5. Trabajo de laboratorio¶

6.6.5.1. Pasos a realizar en el QuartusII/Modelsim-Altera¶

Desde el Campus Virtual descargar el fichero Practica4.zip. Descomprimir este fichero en el directorio Practica4 creado para esta práctica. Entrar en QuartusII y crear un proyecto nuevo (Practica4.qpf).

Crear un nuevo fichero VHDL para describir la MEF.

Introducir en este fichero la descripción realizada en el apartado Descripción VHDL de la MEF y guardarlo con el nombre MEF_refrescos_moore.vhd.

Declarar a MEF_refrescos_moore.vhd como el top-level del circuito.

Establecer como preferencia de Quartus II la codificación Gray.

Seleccionar Assignements > settings > Compiler setting > Advanced setting (Synthesis).

En la casilla “Filter” poner “State”.

En el cuadro “State Machine Processing“ seleccionar “Gray” y aceptar hasta volver a la página principal de Quartus II.

Compilar el diseño.

Crear un nuevo fichero de formas de onda con el University Wafeform VWF (Waveform.vwf).

Simular este circuito usando Modelsim-Altera.

Introducir todos los pines del circuito en el diagrama de formas de onda.

Ordenar las señales de la siguiente manera: clock, reset_n, a_in, b_in, r_out, c_out, monedas.

Establecer el tiempo de simulación en 500 ns.

Definir el reloj como una señal periódica de 50 ns (20 MHz) y el reset_n siempre a ‘1’ a excepción de los primeros 60 ns que estará a ‘0’.

Añadir las variables de estado: Edit > Insert Node o Bus > Node Finder. En la nueva ventana en la casilla “Filter” seleccionar “All & Registers Post-fitting” y luego seleccionar “List”. Incluir en el diseño (en este orden): Qactual.state_bit_2, Qactual.state_bit_1 y Qactual.state_bit_0.

En la ventana de formas de ondas seleccionar Qactual.state_bit_2, Qactual.state_bit_1 y Qactual.state_bit_0, darle al botón derecho y seleccionar “Grouping”. El nombre del grupo debe ser “Estado_actual”. Mover el grupo justo debajo de la señal b_in.

Secuencia de entradas siguiente a partir de los 50 ns iniciales.

t (ns) |

b_in |

a_in |

|---|---|---|

70-80 |

1 |

0 |

120-130 |

0 |

1 |

170-180 |

1 |

0 |

270-280 |

1 |

0 |

320-330 |

0 |

1 |

370-380 |

0 |

1 |

420-430 |

0 |

1 |

Ejecutar la simulación en Modelsim-Altera (Simulation > Run Functional Simulation).

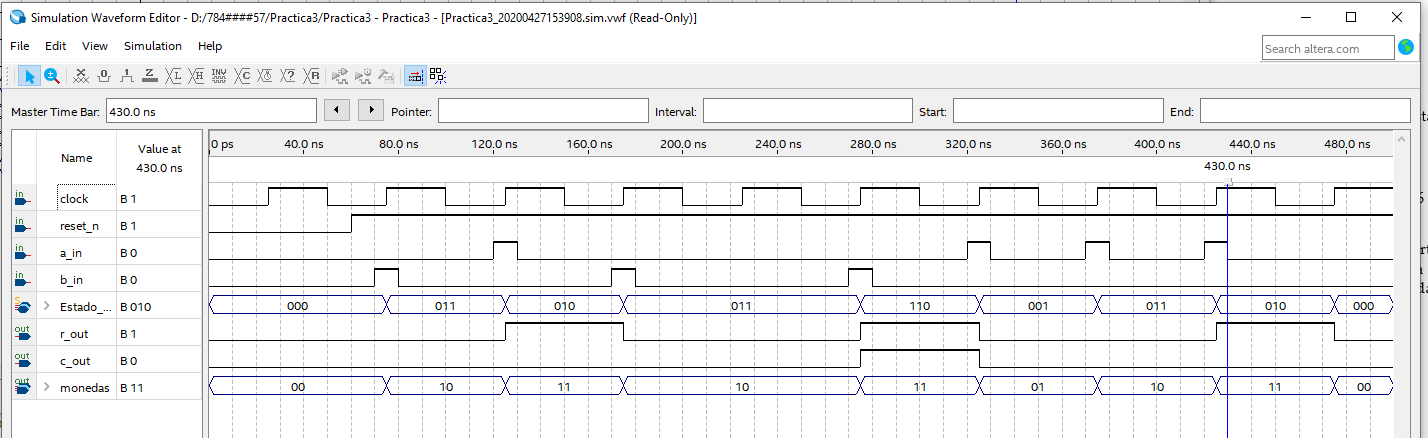

Comprobar que los resultados son los esperados según la transparencia la figura Figura 6.6.

Figura 6.6 Resultado de simulación de la MEF de la Práctica 4.¶

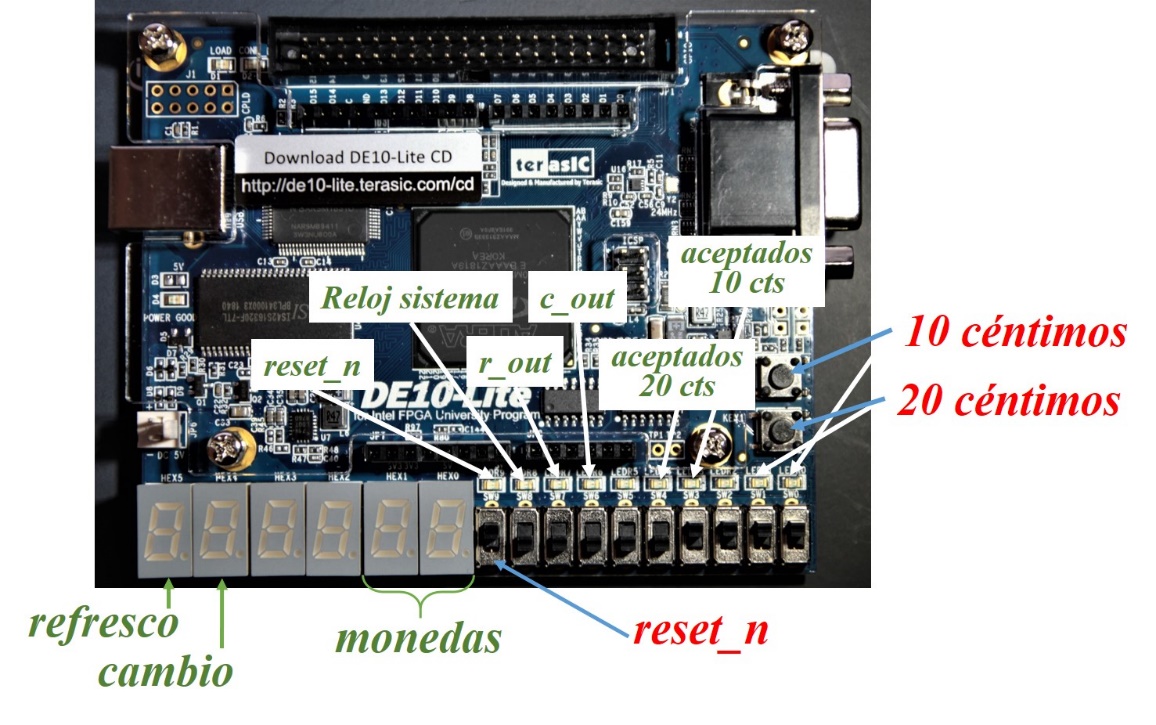

6.6.5.2. Implementación en la tarjeta DE10_lite¶

Añadir al proyecto un nuevo fichero VHDL que corresponde con el contador de reloj que se encuentra en el subdirectorio Practica4/ips-basicos (Listado 6.9). El fichero VHDL de denomina contador_reloj.vhd.

Hacer lo mismo con la descripción VHDL del debouncer que se encuentra en en el subdirectorio Practica4/ips-basicos (Listado 6.10) y que se denomina SM_debouncer.vhd.

Añadir al proyecto todos los ficheros VHDL que se encuentran en el directorio Practica4/ips-display que permitiran representar la información sobre los displays de 7 segmentos.

Añadir al proyecto un VHDL (Practica4.vhd) que se proporciona en el subdirectorio quartus (Listado 6.11). Se observa que este VHDL representa la descripción del sistema completo (tal como aparece en el apartado Descripción VHDL de la MEF) y las conexiones de entrada/salida de la placa DE10-Lite.

Declarar a Practica4.vhd como el top-level del circuito.

Compilar el diseño.

Importar las descripciones de los pines que aparece en el Campus Virtual (Practica4.qsf).

Figura 6.7 Pin-out Práctica 4.¶

Compilar el diseño.

Programar la tarjeta usando el fichero Practica4.sof.

- Comprobar que los resultados son exactamente iguales que la tabla de

verdad y a la simulación realizada.

6.6.5.3. Visor de máquina de estados¶

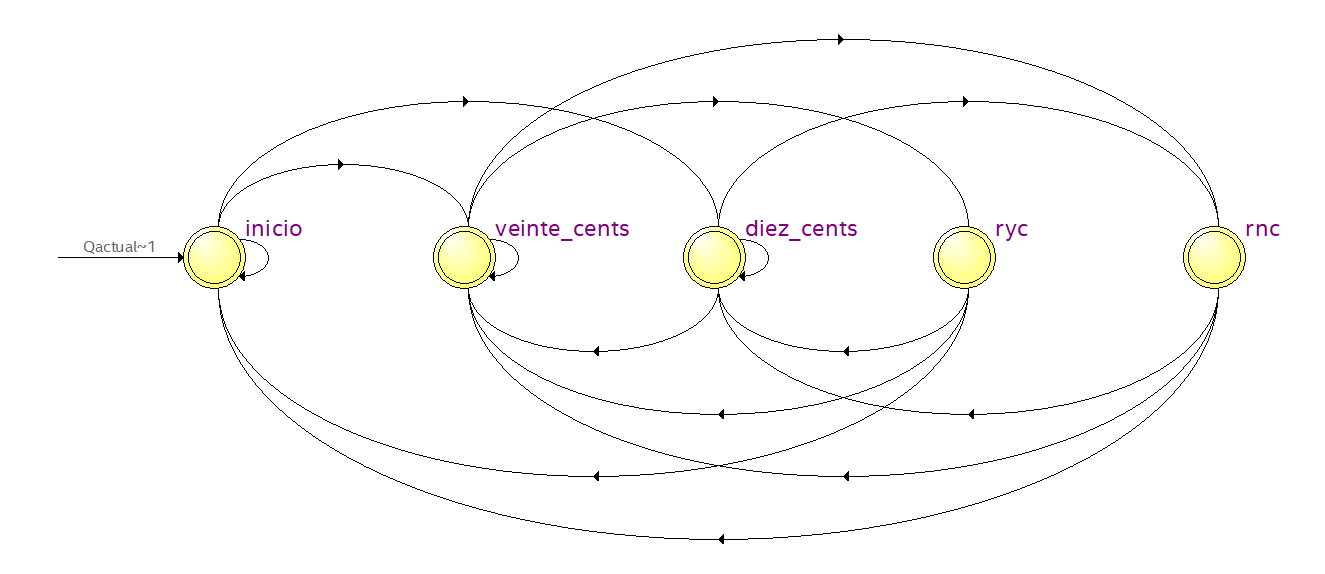

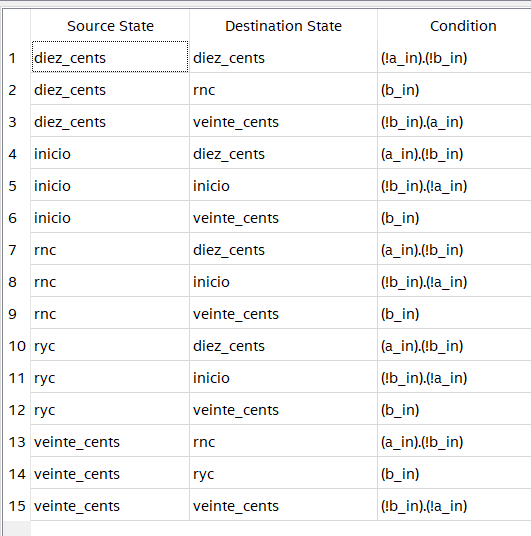

El Quartus II permite ver la máquina de estados diseñada tanto en forma de grafo como de tabla. En la página principal de Quartus dos usamos el siguiente menú: Tools > Netlist Viewer > State Machine. Quartus abrirá una nueva página. En la parte izquierda superior de esta página, podremos seleccionar la máquina de estados que queremos ver (en principio debe visualizar un SM_beuncer. En el menú desplegable seleccionamos |Práctica3|MEF_refrescos_moore:U1|Qactual. Podremos ver la máquina de estados diseñada tanto en formato de grafo (Figura 6.8) como de tabla (Figura 6.6).

6.6.6. Entregables¶

6.6.6.1. Trabajo previo¶

Por hacer

E4.1. Subir al Campus Virtual el grafo realizado según el apartado Descripción de la MEF.

E4.2. Realizar la descripción VHDL de la MEF en el Laboratorio Virtual de Programación (VPL) en el Campus Virtual de la asignatura.

6.6.6.2. Trabajo de laboratorio¶

Por hacer

E4.3. Mostrar al profesor de prácticas la realización de los pasos realizados según el apartado Pasos a realizar en el QuartusII/Modelsim-Altera.

E4.4. Mostrar al profesor el funcionamiento del circuito realizado en el apartado Implementación en la tarjeta DE10_lite.

6.6.7. Comentarios sobre la práctica¶

6.6.7.1. Conceptos VHDL necesarios¶

Instrucción PROCESS.

Crear tipos de datos con TYPE.

Ejecución concurrente y secuencial.

Concepto de lista de sensibilidad.

Generación del reloj VHDL.

Generación de señal de reset.

6.6.8. Listados VHDL¶

-- Ver en el campus Virtual de la Asignatura

-- Ver en el campus Virtual de la Asignatura

-- Ver en el campus Virtual de la Asignatura