6.4. Práctica 2: Introducción al Quartus II¶

6.4.1. Duración¶

Esta práctica tendrá una duración de 3 horas en el laboratorio (2 sesiones de 90 minutos).

6.4.2. Objetivos¶

Introducir el concepto de diseño con Quartus II y la verificación funcional con Modelsim-Altera.

Familiarizarse con el flujo de diseño de Quartus II y realizar todos los pasos de un diseño.

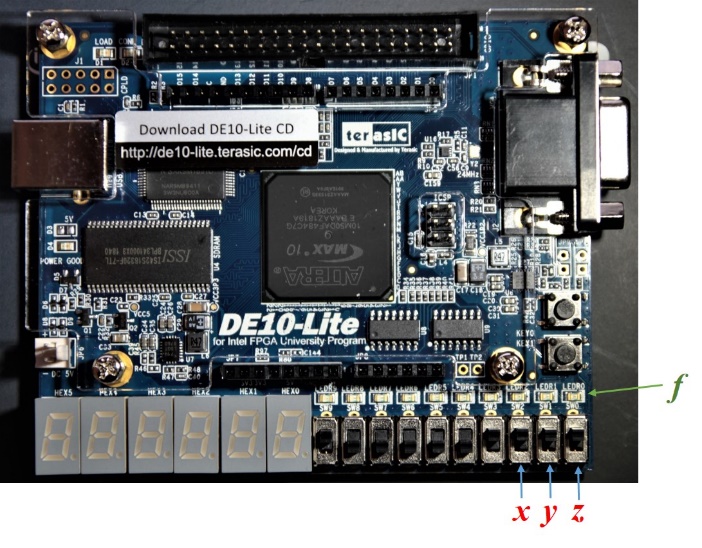

Implementar un diseño en la tarjeta Terasic DE10-Lite.

6.4.3. Introducción¶

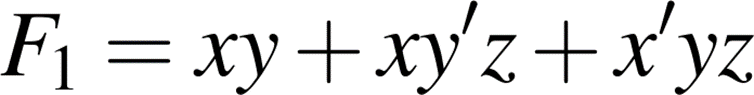

En esta práctica se va a implementar una función f de tres entradas (x, y, z) que viene definida por la siguiente expresión de suma de productos:

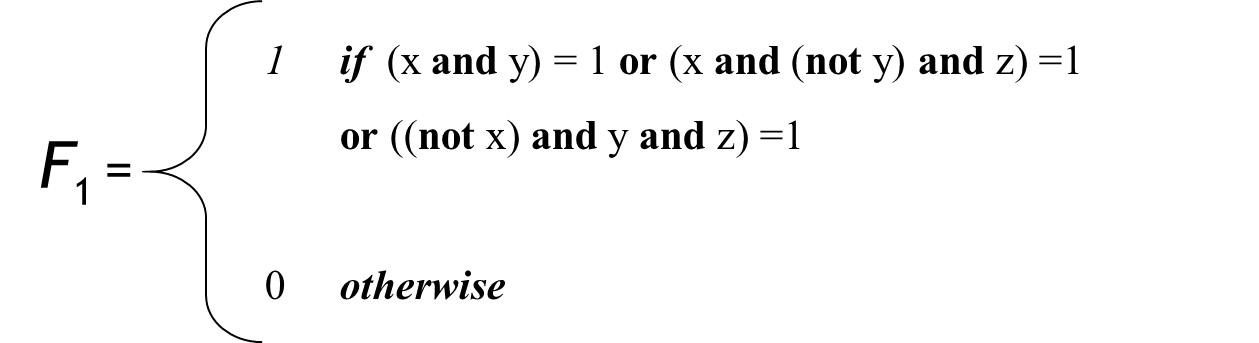

Especificación funcional:

Entradas: \(x, y, z \in \{0, 1\}\).

Salida: \(f \in \{0, 1\}\).

Función:

Siguiendo la especificación, la ecuación algebraica de la función es la siguiente:

En las transparencias de teoría del tema 2 (páginas 39 y 40) se explica cómo se obtiene la tabla de verdad de esta función. En las transparencias de problemas del tema 2 (páginas 7-10) se realiza la descripción VHDL y un banco de prueba (testbench) del diseño.

La descripción general de la práctica es como sigue. En la herramienta Quartus II, se realizará un esquema de puertas de la función F1. Para ello utilizaremos los siguientes elementos:

Tres puertos de entrada: x, y, z.

Un puerto de salida: f.

Dos inversores (NOT), una puerta AND de dos entradas (and2), dos puertas AND de tres entradas (and3) y una puerta OR de tres entradas (or3).

Posteriormente se simulará el diseño utilizando el generador de formas de ondas de Quartus II (University Wafeform VWF). Para verificar el diseño se utilizará la tabla de verdad de la página 40 de las transparencias de teoría del tema 2.

Finalmente se hará una implementación en la tarjeta DE10-lite, para lo cual se asignarán las entradas y salidas de la función a las entradas/salidas disponibles en la tarjeta DE10-Lite.

6.4.4. Trabajo previo¶

Como trabajo previo el estudiante deberá obtener el esquema de puertas de la función F1 y hacer la entrega en el Campus Virtual (Sección Prácticas de Laboratorio, Práctica 2). Asimismo, deberá ser capaz de entender la tabla de verdad de la función F1. Como ayuda referirse a las transparencias de teoría y de problemas antes mencionadas.

6.4.5. Trabajo de laboratorio¶

6.4.5.1. Tutorial de QuartusII/Modelsim-Altera¶

Para esta primera práctica se va a realizar un tutorial de QuartusII/Modelsim-Altera. Con este tutorial aprenderemos a iniciar el programa, a capturar una descripción de un circuito en este entorno, hacer simulaciones con el Modelsim-Altera usando el University Wafeform VWF. Finalmente el diseño se implementará en la placa DE10-Lite.

Nota

Antes de realizar la práctica, lea detenidamente los comentarios en la sección Intrucciones para ejecutar QuartusII.

El guion de este tutorial de QuartusII/Modelsim-Altera se proporciona en el Anexo (Quartus Tutorial). Este documento se empleará como guía de cuál debe ser el procedimiento a seguir en las simulaciones de los distintos circuitos que se modelen en las prácticas de la asignatura.

6.4.5.2. Resumen de pasos a realizar en el QuartusII/Modelsim-Altera¶

Crear un proyecto nuevo (Practica2.qpf).

Crear un esquema del circuito (funcion.bdf) diseñado en el trabajo previo.

Declarar funcion.bfd como top-level del diseño.

Simular este circuito usando el University Wafeform VWF (Waveform.vwf).

Crear un COMPONENTE VHDL para el esquema del circuito.

Crear un VHDL (Practica2.vhd) que incluya el componente creado.

Declarar Practica2.vhd como top-level del diseño.

Asignar los pines correspondientes en la tarjeta DE10-Lite.

Figura 6.2 Pin-out de la Práctica 2.¶

Programar la tarjeta usando el fichero Practica2.sof.

Analizar la base de datos generada por QuartusII.

6.4.6. Entregables¶

6.4.6.1. Trabajo previo¶

Por hacer

E2.1. Subir al Campus Virtual esquema del circuito diseñado con puertas básicas (ver Sección Trabajo previo).

6.4.6.2. Trabajo de laboratorio¶

Por hacer

E2.2. Mostrar al profesor de prácticas la realización de los pasos realizados según el apartado (ver Sección Resumen de pasos a realizar en el QuartusII/Modelsim-Altera) y entregar el informe de prácticas.

6.4.7. Comentarios sobre la práctica¶

6.4.7.1. Conceptos VHDL necesarios¶

Conocer los tipos de datos básicos STD_LOGIC y conocer los valores que puede tomar un STD_LOGIC.

Estructura de un diseño VHDL (ENTITY, ARCHITECTURE, BEGIN, END).

Instrucción COMPONENT (necesario para instanciar el DUT (Device Under Test).

Definir y utilizar señales (SIGNAL).

6.4.8. Listados VHDL¶

-- Electronica Digital, curso 2

-- EITE-ULPGC

-- Descripcion estructural practica 2

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY Practica2 IS

PORT(x_in : IN STD_LOGIC;

y_in : IN STD_LOGIC;

z_in : IN STD_LOGIC;

f_out: OUT STD_LOGIC );

END Practica2;

ARCHITECTURE estructural OF Practica2 IS

COMPONENT funcion IS

PORT (x : IN STD_LOGIC;

y : IN STD_LOGIC;

z : IN STD_LOGIC;

f : OUT STD_LOGIC);

END COMPONENT;

BEGIN

U1: funcion

PORT MAP(

x => x_in,

y => y_in,

z => z_in,

f => f_out

);

END estructural;