6.8. Práctica 6: Circuitos secuenciales¶

6.8.1. Duración¶

Esta práctica tendrá una duración de 2 horas en el laboratorio (1 sesión).

6.8.2. Objetivos¶

El objetivo general de esta práctica es «Realizar un contador ascendente-descendente con límite de cuenta». Otros objetivos específicos son los siguientes:

Usar los conceptos de VHDL aprendidos hasta el momento para usar circuitos secuenciales avanzados: contador.

Usar un contador ascendente para hacer un contador ascendente/descendente y con limitación de cuenta.

6.8.3. Introducción¶

Esta práctica consiste en realizar un contador ascendente/descendente de 8 bits con un límite de cuenta. El funcionamiento será el siguiente teniendo en cuenta que el límite de cuenta lo llamamos cuenta_fin.

Con up_down = ‘1’: 0, 1, 2, 3, 4, \(\ldots\), cuenta_fin, 0, 1 \(\ldots\)

Con up_down = ‘0’: cuenta_fin, cuenta_fin -1, \(\ldots\), 4, 3, 2, 1, 0, cuenta_fin, cuenta_fin -1, \(\ldots\)

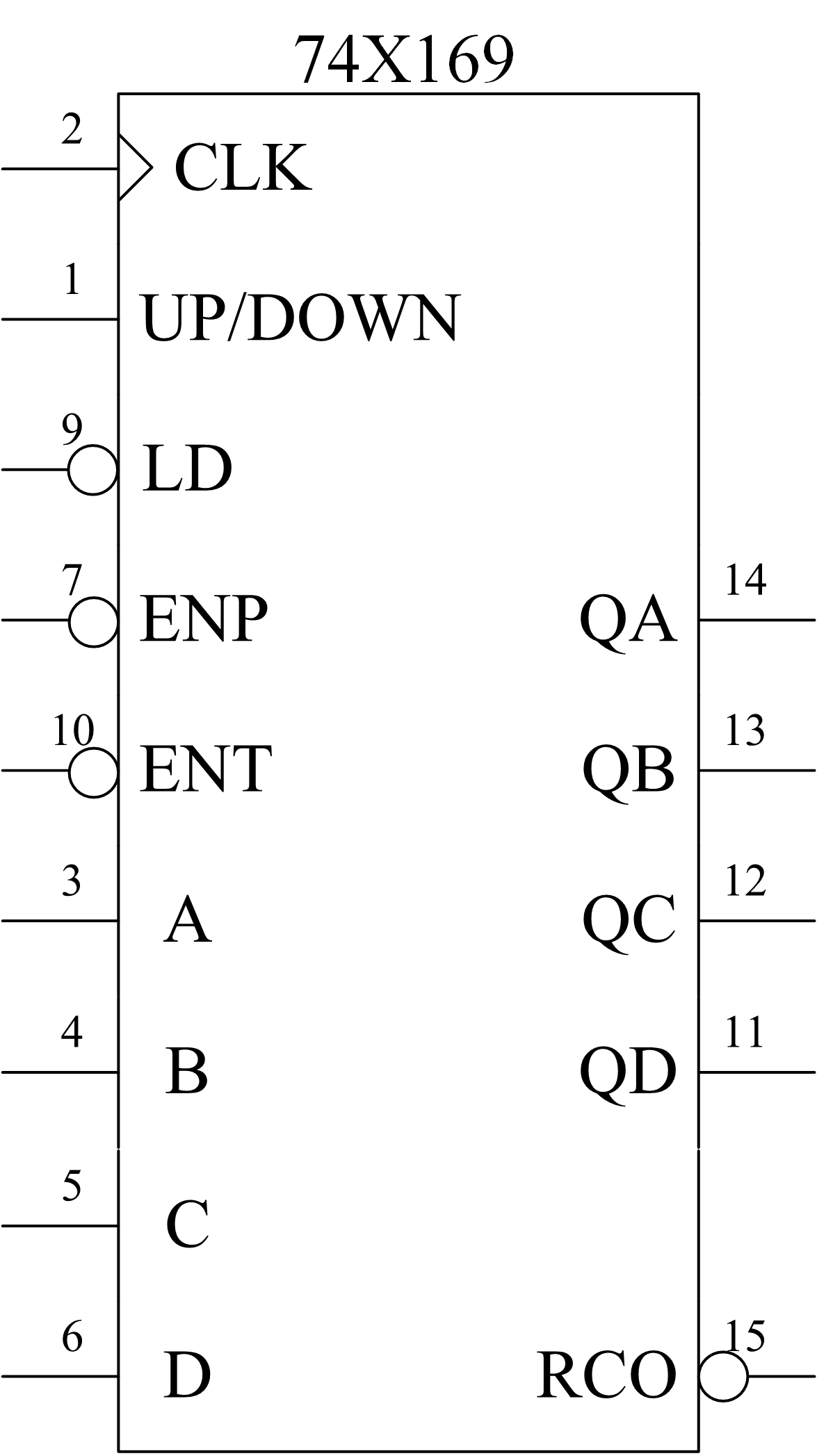

El contador de 8 bits a realizar estará basado en el 74x169, que es un contador ascendente/descendente de 4 bits. La Figura 6.12. representa las entradas salidas del contador 74x169.

Figura 6.12 Pin-out del 74x169.¶

La Práctica tendrá dos fases:

Crear el contador 74x169 a partir del un contador 74x163.

Crear un contador ascendente/descendente con límite de cuenta (cuenta_fin).

Para crear el contador 74x169 nótese que la entrada clear del 74x163 debe ser sustituida por la entrada up/down. El clear en este contador se realiza poniendo la entrada load (LD) a ‘0’ y las entradas DCBA a “0000”. El contador cuenta de forma ascendente cuando la entrada up/down es ‘1’ y lo hace de forma descendente cuando up/down = ‘0’. La señal RCO es activa a nivel bajo, permanece siempre a ‘1’ excepto en las dos situaciones siguientes, que establece su valor a ‘0’:

En cuenta ascendente (up/down = ‘1’) cuando la salida toma el valor 15, es decir QDQCQBQA = “1111”.

En cuenta descendente (up/down = ‘0’) cuando la salida toma el valor 0, es decir QDQCQBQA = “0000”.

6.8.4. Trabajo previo¶

6.8.4.1. Descripción VHDL de un contador ascendente/descendente 74x169¶

Hacer una descripción funcional de un contador ascendente/descendente (74x169) modificando la descripción del contador 74x163 dada en clase (véase la transparencia 20 del tema 9 o ver Listado 6.17). Nótese que el RCO es activo a nivel bajo. Usar los siguientes nombres para las entrasdas y salidas: clock, load_n, up_down, enp_n, ent_n, dato_in, q_out, rco_n (_n indicará activo a nivel bajo).

Nota

La señal RCO solo se activará (nivel lógico 0) cuando se llegue al valor 15 (cuenta ascendente) o cuando se llege al valor 0 (cuenta descendente). No se activará cuando se llege al valor límite de cuenta cuenta_fin.

Este trabajo previo se realizará en el Campus Virtual de la asignatura mediante un Laboratorio de Programación (VPL: Práctica 6: Contador 74x169) siguiendo la entidad descrita en el Listado %s.

6.8.5. Trabajo de laboratorio¶

6.8.5.1. Implementar el contador 74x169 en Quartus II y simular con Modelsim-Altera¶

Crear un proyecto nuevo (Practica6.qpf).

Crear un nuevo fichero VHDL para describir el contador 74x169 partiendo del Listado 6.17.

Introducir en este fichero la descripción realizada en el apartado Descripción VHDL de un contador ascendente/descendente 74x169 y guardarlo con el nombre contador_74169.vhd.

Declarar a contador_74169.vhd como el top-level del circuito.

Compilar el diseño.

Crear un nuevo fichero de formas de onda con el University Wafeform VWF (Waveform.vwf).

Simular este circuito usando Modelsim-Altera.

Introducir todos los pines del circuito en el diagrama de formas de onda.

Ordenar las señales de la siguiente manera: clock, load_n, up_down, enp_n, ent_n, dato_in, q_out, rco_n.

Establecer el tiempo de simulación en 1000 ns.

Definir el reloj como una señal periódica de 20 ns (50 MHz) y el load_n siempre a ‘1’, enp_n y ent_n siempre a ‘0’ y la señal up_down la mitad del tiempo a ‘1’ y la otra mitad a ‘0’.

En la ventana de formas de ondas seleccionar q_out, darle al botón derecho del ratón y seleccionar “Radix > Unsigned Decimal”.

Ejecutar la simulación en Modelsim-Altera (Simulation > Run Functional Simulation).

Comprobar que el contador cuenta de manera ascendente y luego descendente, y que la señal rco_n se pone a ‘0’ en los casos adecuados.

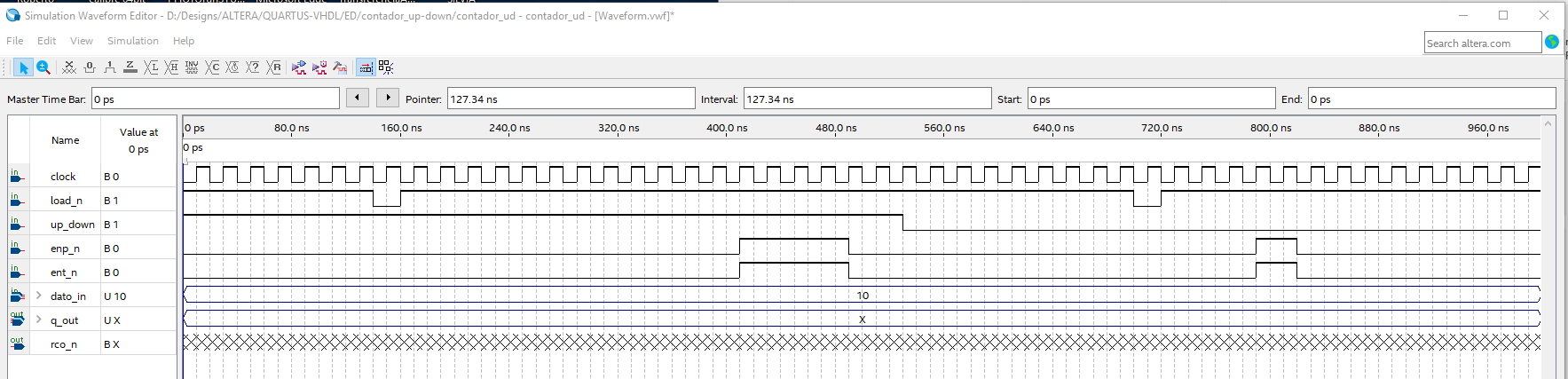

Establecer el valor de dato_in a “1010” y establecer el resto de señales como indica la siguiente Figura.

Figura 6.13 Estímulos para simular el contador 74x169.¶

Ejecutar la simulación en Modelsim-Altera (Simulation > Run Functional Simulation).

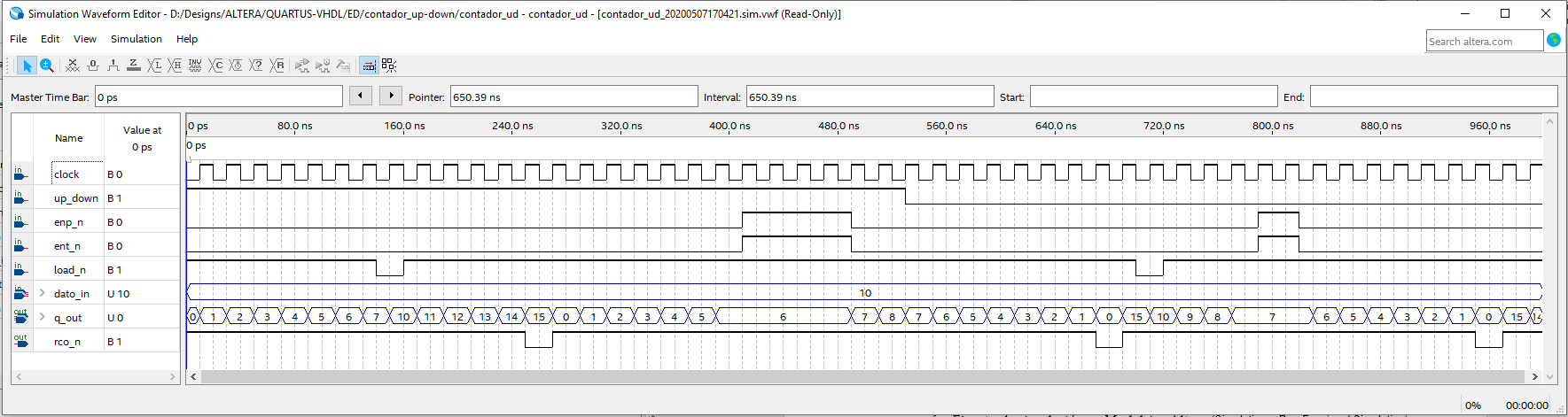

Comprobar que la salida del contador es como se representa en la siguiente Figura.

Figura 6.14 Resultados de la simulación del contador 74x169.¶

6.8.5.2. Implementación en la tarjeta DE10_lite¶

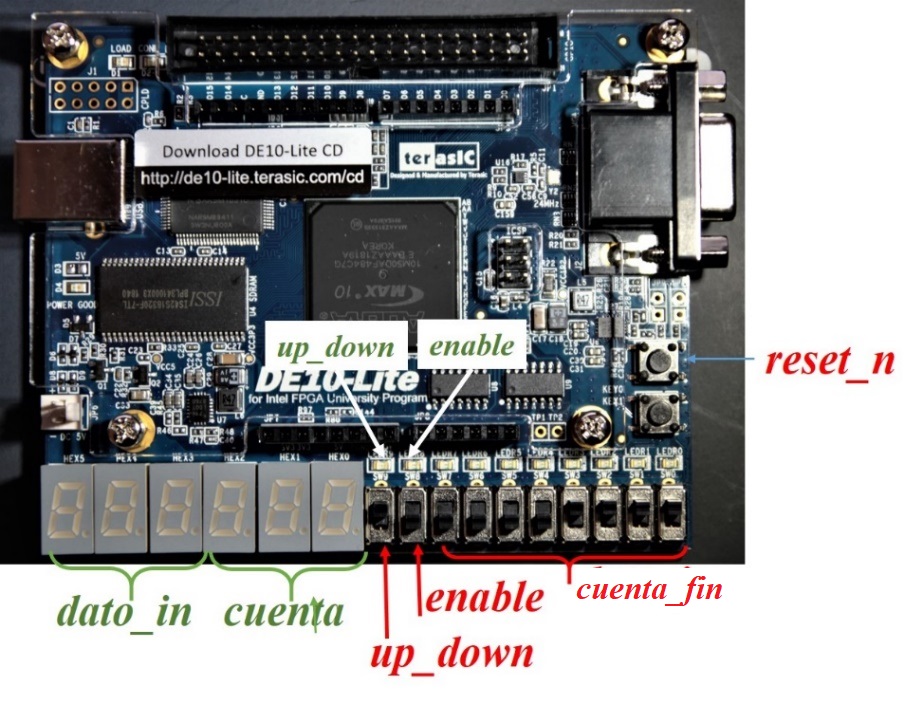

La información se introducirá mediante los interruptores de la siguiente manera:

El límite de la cuenta cuenta_fin se introducirá a través en los interruptores SW[7] a SW[0] (conectados a dato_in).

La señal de enable en el interruptor SW[8].

La señal up_down en el interruptor SW[9].

La señal de reset_n en el pulsador Key0.

La representación de la información se realizará en los displays de 7 segmentos de la siguiente manera:

El límite de la cuenta (dato_in) se representará en BCD en los displays números 3, 4 y 5 respectivamente.

El resultado final se representará en los displays 0, 1 y 2 en formato BCD.

Figura 6.15 Pin-out de la Práctica 6.¶

Para la implementación realizar las siguientes tareas:

Crear un nuevo fichero VHDL para describir el contador ascendente/descendente con límite de cuenta según el Listado 6.19.

Introducir en este fichero la descripción realizada en el Listado 6.17 y guardarlo con el nombre contador_ud_8bits.vhd.

Agregar al proyecto la descripción del contador de reloj que se encuentra en Listado 6.9 de la Práctica 3 y guardar el fichero como contador_reloj.vhd.

Añadir al proyecto la descripción VHDL (Practica6.vhd) que se proporciona en el Campus Virtual (ver Listado 6.19). Se observa que este VHDL representa la descripción del sistema completo y las conexiones de entrada/salida de la placa DE10-Lite.

Añadir al proyecto las descripciones proporcionadas en la Práctica 4 (ver Listado 6.12, Listado 6.13, Listado 6.14 y Listado 6.15), o en el Campus Virtual:

binary_to_7seg_display.vhd, que representa un valor en binario en un display de 7 segmentos;

bynary_to_BCD.vhd y binary_to_bcd_digit.vhd, que convierten un valor binario en código BCD; y

BCD_7segment.vhd, que representa un valor en BDC en un display de 7 segmentos.

Declarar a Practica6.vhd como el top-level del circuito.

Compilar el diseño.

Importar las descripciones de los pines de la Práctica 6 (Practica6.qsf): Assignments > Import Assignments ….

Compilar el diseño.

Programar la tarjeta usando el fichero Practica6.sof.

Comprobar que los resultados son exactamente iguales que la tabla de verdad y a la simulación realizada.

6.8.6. Entregables¶

6.8.6.1. Trabajo previo¶

Por hacer

E6.1. Descripción VHDL estructural del circuito del apartado Descripción VHDL de un contador ascendente/descendente 74x169 y verificación. Realizar el VPL En el Campus Virtual.

6.8.6.2. Trabajo de laboratorio¶

Por hacer

E6.2. Mostrar al profesor la simulación del contador 74x169 realizada en Quartus.

E6.3. Mostrar al profesor la implementación en la tarjeta DE10-Lite de la Práctica 6.

6.8.8. Listados VHDL¶

-- 74x163 en VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY contador_74163 IS

PORT(clk : IN STD_LOGIC;

clrn : IN STD_LOGIC;

ldn : IN STD_LOGIC;

enp : IN STD_LOGIC;

ent : IN STD_LOGIC;

dato_in : IN STD_LOGIC_VECTOR (3 DOWNTO 0);

q_out : OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

rco : OUT STD_LOGIC );

END contador_74163;

ARCHITECTURE funcional OF contador_74163 IS

SIGNAL iq: UNSIGNED (3 DOWNTO 0);

BEGIN

PROCESS (clk) BEGIN

IF RISING_EDGE(clk) THEN

IF clrn = '0' THEN iq <= (OTHERS => '0'); --clear y load síncronos

ELSIF ldn = '0' THEN iq <= UNSIGNED(dato_in);

ELSIF (ent AND enp) = '1' THEN iq <= iq + 1; --cuenta solo si ent=enp=1

END IF;

END IF;

IF (iq = 15) AND (ent = '1') THEN rco <= '1';

ELSE rco <= '0';

END IF;

q_out <= STD_LOGIC_VECTOR(iq);

END PROCESS;

END funcional;

-- Ver en el campus Virtual de la Asignatura

-- Ver en el campus Virtual de la Asignatura