6.1. Introducción a las prácticas de Electrónica Digital¶

Esta guía de prácticas de la asignatura Electrónica Digital contendrá toda la información necesaria para que los estudiantes puedan realizar las prácticas. Las prácticas se realizarán en el Laboratorio de ASICs y Sistemas Digitales con las siguientes herramientas y tarjeta de prototipado:

Software Altera Quartus II

Software de simulación Modelsim-Altera

Tarjeta de prototipado: Terasic DE10-Lite

6.1.1. Intel/Altera Quartus II¶

El software de diseño Altera Quartus II proporciona un entorno de diseño completo y multiplataforma que se adapta fácilmente a las necesidades de los diseños específicos. Es un entorno integral para el diseño de sistema en chip programable (SOPC). Es de acceso gratuito y se puede conseguir en la siguiente dirección:

https://fpgasoftware.intel.com/?edition=lite

La versión que se utilizará en las prácticas es la 19.1 Lite y debe incluir el software de simulación Modelsim-Altera y la configuración para el dispositivo MAX10.

6.1.2. Terasic DE10-Lite¶

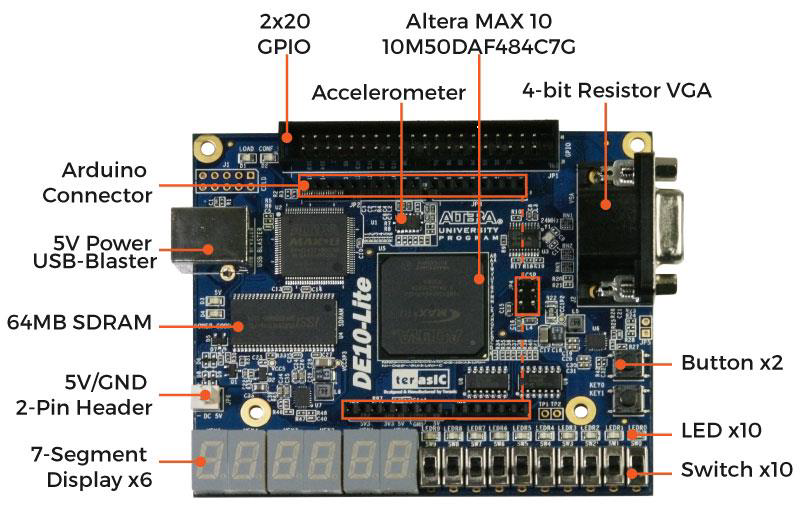

La tarjeta de prototipado Terasic DE10-Lite incluye una FPGA de la familia Altera MAX10 (en concreto la 10M50DAF484C7G). Más información se puede ver en el Anexo (Información sobre la tarjeta DE10-Lite) y en el manual de la tarjeta. De los distintos elementos que dispone la tarjeta (ver Figura 6.1) en las prácticas de Electrónica Digital se usarán los siguientes:

Entrada de información:

2 pulsadores (en la Figura Button x2).

10 interruptores de entrada (en la Figura Switch x10).

Salida/representación de la información:

10 LEDs.

6 displays de 7 segmentos (en la Figura 7-Segment Displays x6).

Para la conexión de la tarjeta al ordenador se usará el USB tipo B (5V Power USB-Blaster) que permitirá configurar la FPGA y alimentar la tarjeta DE10-Lite.

Figura 6.1 Tarjeta de prototipado DE10-Lite.¶

Nota

Esta tarjeta está disponible en el Laboratorio de práctias (Laboratorio de ASICS y Sistemas Digitales).

6.1.3. Otras herramientas usadas¶

6.1.3.1. Eda Playground¶

La herramienta que se utilizará en la primera práctica es la siguiente:

EDA playground (https://www.edaplayground.com/). Incluye las herramientas EDA Playground y EPWave que permiten introducir una descripción VHDL y ver las formas de onda. EDAPlayground requiere registrarse en la página web y se pueden ir almacenando los diseños en un espacio propio.

6.1.3.2. Otras-heramientas¶

Otras herramientas interesantes son las siguientes:

VHDL-tool (https://www.vhdltool.com/tryit). Herramienta que chequea la sintaxis de una descripción VHDL. Se puede usar desde la página web (recomendado) o se puede descargar e instalar, pero solo está disponible en Linux.

Testbench Generator (https://vhdl.lapinoo.net/testbench/). Herramienta que genera el esqueleto de un banco de pruebas (testbench) para un diseño determinado. Este testbench luego puede ser utilizado en el EDAPlayground.

6.1.3.3. Procedimiento¶

Para la realización del trabajo previo de cada una de las prácticas se recomienda usar se siguiente procedimiento para utilizar estas herramientas (ver el Anexo Simulación de descripciones VHDL en el entorno Eda_Playground Anexo 2):

Se inicia sesión en EDAPlayground y se realiza la descripción VHDL del circuito que se quiere diseñar.

Se comprueba la sintaxis de la descripción realizada con VHDL tool. Para ello se hace un copy&paste del diseño y se lleva a la página https://www.vhdltool.com/tryit.

Si no hay errores, se hace un copy&paste de la descripción VHDL en el Testbench Generator y se genera un testbench para el diseño.

Se hace un copy&paste de este testbench y se lleva al EDAPlayground. Se completan los estímulos y se realiza la simulación.

No obstante, en muchas prácticas es obligatorio realizar el trabajo previo en el Campus Virtual mediante la realización de un VPL.

6.1.3.4. Editores de texto¶

Tambien es recomendable el uso del Notepad++ como editor de ficheros VHDL (https://notepad-plus-plus.org/). Cuando se selecciona el lenguaje VHDL dentro de Notepad++ el editor remarcará los elementos de la sintaxis en diversos colores, facilitando su lectura.

6.1.4. Uso de esta guía de prácticas¶

Léase bien y por completo el guion de cada práctica. Observe que en la mayoría de los casos es necesario realizar cálculos, diseños y/o simulaciones para su realización. Se exige que con carácter primordial realice previamente los cálculos, diseños y/o simulaciones que se precisen. Este trabajo previo siempre se debe de entregar o de realizar en el Campus Virtual en unas frechas preestablecidas. La realización de las prácticas no requiere de material adicional.

Cada práctica tiene una estructura que incluye al menos los siguientes apartados:

Duración: tiempo disponible en el Laboratorio para terminar la práctica. No incluye el tiempo necesario para hacer el trabajo previo.

Objetivos: Objetivos docentes de la práctica.

Trabajo previo:. Trabajo que debe realizarse antes de realizar la práctica en el Laboratorio. Cada práctica define bajo este epígrafe todos los cálculos, diseños y simulaciones que debe hacer para afrontar la práctica en el laboratorio.

Advertencia

Queda bajo la responsabilidad del estudiante las consecuencias que se deriven de que no se realicen dichos cálculos, diseños y/o simulaciones.

Trabajo de laboratorio: Trabajo que debe realizarse en el Laboratorio y en el tiempo especificado en la duración de la práctica.

Entregables: Documentos/circuitos que deben entregarse como justificación de haber realizado la práctica.

Advertencia

Los entregables se pueden referir al trabajo previo, que deben entregarse antes de las sesiones de Laboratorio en el Campus Virtual; o pueden referirse al trabajo de laboratorio que se entregarán al finalizar la práctica en el Laboratorio.

Comentarios sobre la práctica: Comentarios informativos sobre la práctica, entre los cuales se incluyen los conceptos imprescindibles que deben aprenderse de teoría antes de afrontar la práctica. En cualquier caso, es necesario que los estudiantes asimilen los conceptos de teoría antes de afrontar las prácticas.

6.1.5. Resumen de las prácticas¶

6.1.5.1. Práctica 1. Simulación de descripciones VHDL en el entorno Eda Playground¶

Objetivo: |

Familiarizarse con el uso del entorno Eda Playground |

|---|---|

Duración: |

2 horas en el laboratorio (1 sesión). |

Temas: |

Temas 1 de la asignatura. |

6.1.5.2. Práctica 2. Introducción al Quartus II¶

Objetivo: |

Familiarizarse con el uso de la herramienta Quartus II |

|---|---|

Duración: |

3 horas en el laboratorio (2 sesiones de 90 minutos). |

Temas: |

Temas 2 y 3 de la asignatura. |

6.1.5.3. Práctica 3. Funciones lógicas, minimización e implementación¶

Objetivo: |

Minimizar e implementar una función lógica |

|---|---|

Duración: |

2 horas en el laboratorio (1 sesión). |

Temas: |

Tema 4 de la asignatura. |

6.1.5.4. Práctica 4. Máquina de Estados Finitos (MEF)¶

Objetivo: |

Diseñar una MEF, describirla en VHDL e implementarla en Quartus II |

|---|---|

Duración: |

4 horas en el laboratorio (2 sesiones). |

Temas: |

Temas 5 y 6 de la asignatura. |

6.1.5.5. Práctica 5. Unidad Aritmético Lógica (ALU)¶

Objetivo: |

Diseño e implementación de una ALU que realiza operaciones aritméticas |

|---|---|

Duración: |

2 horas en el laboratorio (1 sesión). |

Temas: |

Tema 8 de la asignatura. |

6.1.5.6. Práctica 6. Circuitos secuenciales¶

Objetivo: |

Realizar un contador ascendente-descendente con límite de cuenta |

|---|---|

Duración: |

2 horas en el laboratorio (1 sesión). |

Temas: |

Tema 9 de la asignatura. |

6.1.6. Resumen de entregables¶

Por hacer

ET1.1. Memoria de trabajo incluyendo el diagrama de ejecución del multiplicador.

ET1.2. Diagrama de bloques completo del Multiplicador serie.

Por hacer

ET1.3. Realizar la descripción VHDL de la unidad de control del Multiplicador serie usando el VPL del Campus Virtual.

ET1.4. Realizar la descripción VHDL funcional del data-path del multiplicador serie del apartado Describir la unidad de data-path en VHDL y y simular con Modelsim-Altera.

ET1.5. Implementación del multiplicador serie en la tarjeta DE10-Lite.

Por hacer

ET2.1. Memoria de trabajo incluyendo el diagrama de ejecución del divisor.

ET2.2. Diagrama de bloques completo del divisor serie.

Por hacer

ET2.3. Realizar la descripción VHDL funcional del data-path del divisor serie del apartado Describir la unidad de data-path en VHDL y y simular con Modelsim-Altera en el VPL disponible en el Campus Virtual.

ET2.4. Realizar la descripción VHDL de la unidad de control del divisor serie en el VPL disponible en el Campus Virtual.

ET2.5. Implementación del divisor serie en la tarjeta DE10-Lite.

Por hacer

ET3.1. Memoria de trabajo incluyendo el grafo de estados de la solución propuesta y el diseño del data-path.

ET3.2. Diagrama de bloques completo del encriptador.

Por hacer

ET3.3. Resolución laboratorio virtual (VPL) en el Campus Virtual de la máquina de control.

ET3.4. Resolución laboratorio virtual (VPL) en el Campus Virtual del encriptador de Vigenère.

ET3.5. Implementación del cifrador serie en la tarjeta DE10-Lite.

Por hacer

ET4.1. Memoria de trabajo incluyendo el diagrama de ejecución del microprocesador.

ET4.2. Diagrama de bloques completo del microprocesador.

Por hacer

ET4.3. laboratorio virtual (VPL) con la descripción VHDL funcional de la ALU y del datapath.

ET4.4. laboratorio virtual (VPL) con la descripción VHDL de la unidad de control del microprocesador.

ET4.5. Implementación del microprocesador serie en la tarjeta DE10-Lite.

Por hacer

ET6.1. Memoria de trabajo.

ET6.2. Grafo de estados del decodificador de pulsos.

ET6.3. Grafo de estados del intérprete de caracteres.

Por hacer

ET6.3. laboratorio virtual (VPL) con la descripción VHDL funcional del decodificador de pulsos del apartado Decodificador de pulsos (pulse decoder).

ET6.4. laboratorio virtual (VPL) con la descripción VHDL funcional del intérprete de caracteres del apartado Intérprete de caracteres (char decoder).

ET6.5. Implementación del decodificador Morse en la tarjeta DE10-Lite.

Por hacer

ET7.1. Memoria de trabajo incluyendo el grafo de estados de la solución propuesta.

ET7.2. Resolución laboratorio virtual (VPL) en el Campus Virtual.

Por hacer

ET7.3. Implementación en el laboratorio de la primera versión de la hormiga (parte desde la posición [1,1].

ET7.4. Memoria de trabajo incluyendo el grafo de estados de la solución propuesta en el cual la hormiga pueda partir de cualquier posición.

ET7.5. Implementación en el laboratorio de la versión definitiva de la hormiga en la tarjeta DE10-Lite.

Por hacer

E1.1. Mostrar al profesor de prácticas la realización de cada uno de los pasos realizados según el apartado (ver Sección Trabajo de laboratorio).

Por hacer

E2.1. Subir al Campus Virtual esquema del circuito diseñado con puertas básicas (ver Sección Trabajo previo).

Por hacer

E2.2. Mostrar al profesor de prácticas la realización de los pasos realizados según el apartado (ver Sección Resumen de pasos a realizar en el QuartusII/Modelsim-Altera) y entregar el informe de prácticas.

Por hacer

E3.1. Realizar y subir al Campus Virtual el proceso de minimización de la función del apartado Minimización de la función usando mapas de Karnaugh, incluyendo la expresión algebraica y circuitos resultantes.

E3.2. Laboratorio Virtual (VPL) de la descripción estructural VHDL y simulación según los especificado en en el apartado Descripción estructural en VHDL.

Por hacer

E3.3. Mostrar al profesor de prácticas la realización de los pasos realizados según el apartado Pasos a realizar en el QuartusII/Modelsim-Altera.

E3.4. Mostrar al profesor el funcionamiento del circuito realizado en el apartado Implementación en la tarjeta DE10_lite.

Por hacer

E4.1. Subir al Campus Virtual el grafo realizado según el apartado Descripción de la MEF.

E4.2. Realizar la descripción VHDL de la MEF en el Laboratorio Virtual de Programación (VPL) en el Campus Virtual de la asignatura.

Por hacer

E4.3. Mostrar al profesor de prácticas la realización de los pasos realizados según el apartado Pasos a realizar en el QuartusII/Modelsim-Altera.

E4.4. Mostrar al profesor el funcionamiento del circuito realizado en el apartado Implementación en la tarjeta DE10_lite.

Por hacer

E5.1. Descripción funcional VHDL de la ALU descrita en el apartado Descripción en VHDL de la ALU y su verficación en el VPL del Campus Virtual.

Por hacer

E5.2. Mostrar al profesor de prácticas la realización de los pasos realizados según el apartado Pasos a realizar en el QuartusII/Modelsim-Altera.

E5.3. Mostrar al profesor el funcionamiento del circuito realizado en el apartado Implementación en la tarjeta DE10_lite en la tarjeta DE10-lite.

Por hacer

E6.1. Descripción VHDL estructural del circuito del apartado Descripción VHDL de un contador ascendente/descendente 74x169 y verificación. Realizar el VPL En el Campus Virtual.

Por hacer

E6.2. Mostrar al profesor la simulación del contador 74x169 realizada en Quartus.

E6.3. Mostrar al profesor la implementación en la tarjeta DE10-Lite de la Práctica 6.